La semana pasada saltó la noticia de que IBM se había convertido en el primer fabricante en crear chips funcionales con litografía de 2 nm, algo que llamó especialmente la atención porque los grandes de la industria a este respecto son TSMC y Samsung, quienes todavía no han llegado a tal hito. En este artículo queremos analizar en profundidad estos chips a 2 nm de IBM para ver si, de verdad, tienen o no dicho tamaño.

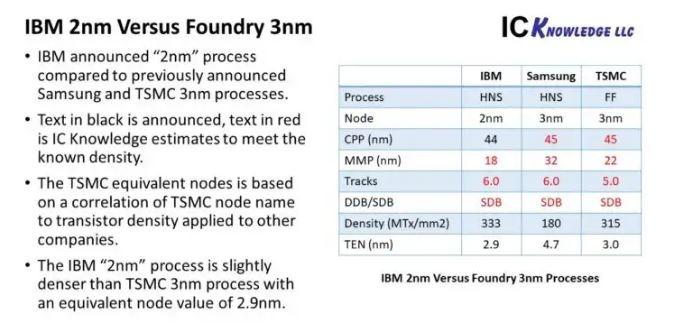

Según el anuncio de IBM, sus nuevos chips utilizan una litografía de 2 nm y contienen 50.000 millones de transistores en el «área de una uña», un tamaño que luego concretaron definiéndolo como 150 mm cuadrados (333 millones de transistores por milímetro). También definieron que estos chips contenían CPP (Contracted Poly Pitch) de 44 nm con 12 nm de longitud en las puertas lógicas, y que están construidos utilizando un proceso GAA con nanohojas horizontales (HNS).

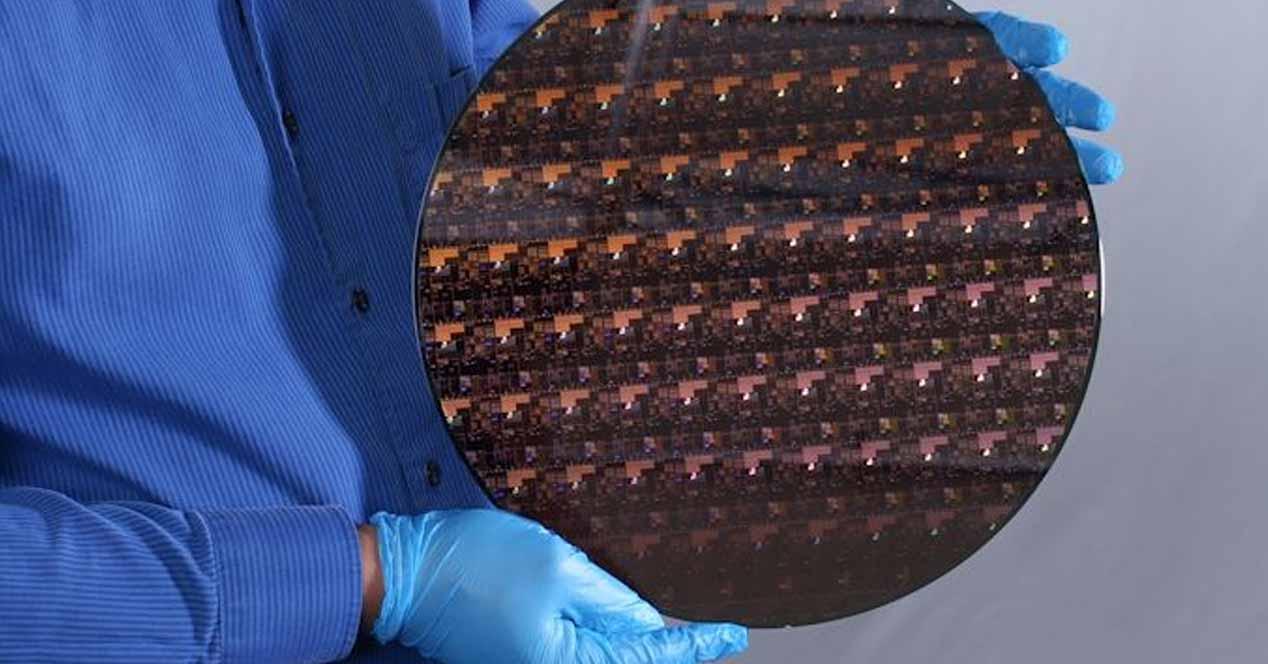

Los chips a 2 nm de IBM

Con estos chips, IBM presume de que han obtenido un 45% más de rendimiento y un 75% de ahorro de energía comparado con los chips más avanzados a 7 nm que existen hasta la fecha pero, ¿son realmente chips de 2 nanómetros o simplemente una mejora de algo que ya existía?

En la tabla que colocamos debajo de estas líneas podemos ver una comparación de los chips a 2 nm de IBM con las estimaciones para los procesos de Samsung y TSMC a 3 nm. Sabemos que Samsung también hace uso de HNS y TSMC se queda con FinFET a 3 nm. Samsung y TSMC han anunciado mejoras de densidad para sus procesos de 3 nm frente a sus procesos de 5 nm, por lo que conocemos la densidad de transistores de las tres empresas y se puede calcular el TEN de todas ellas. Como se señaló anteriormente, el TEN de IBM es 2.9, mientras que el de Samsung es 4,7 y el de TSMC es 3,0, lo que refuerza la teoría de que el nodo de IBM es en realidad comparable a los 3 nm de TSMC.

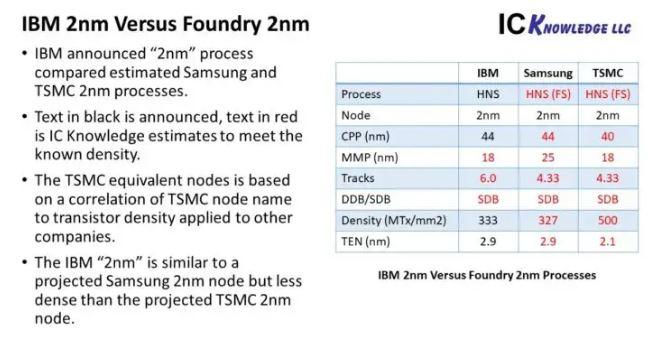

Por otro lado, también se han proyectado los procesos de Samsung y TSMC de 2 nm en la siguiente tabla. Ambas compañías usarán BPR (que todavía no está listo pero lo estará para cuando Samsung y TSMC presenten sus propios 2 nm hacia 2024), y también se asume que Samsung y TSMC utilizarán una arquitectura de hoja de horquilla NHS para alcanzar una altura de pista de 4,33, lo que relajará algunos de los otros requisitos de tamaño.

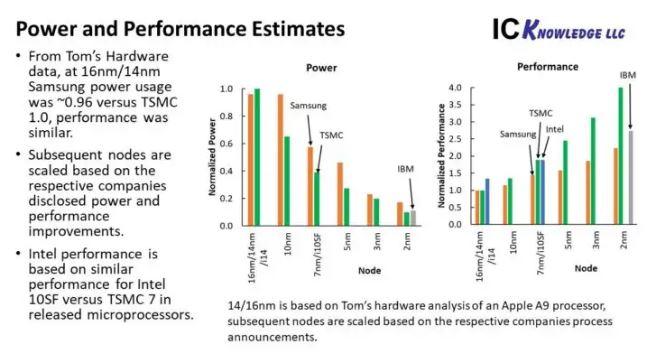

En el ISS de este año, se calculó la potencia y el rendimiento relativos para Samsung y TSMC por nodo con algunos datos de rendimiento adicionales de Intel. La tendencia por nodo se basa en las estimaciones de escalado de potencia y rendimiento anunciadas por las empresas frente a las comparaciones reales disponibles para los nodos de 14 y 16 nm.

Dado que IBM ha comparado sus mejoras de potencia y rendimiento con los nodos de 7 nm existentes, no resulta complicado hacer una regla de tres para ver esta potencia y rendimiento en comparación, para lo que tenéis la siguiente tabla.

El uso de HNS por parte de IBM produce una reducción significativa en la energía consumida y hace que su proceso de 2 nm sea más eficiente energéticamente que el proceso de 3 nm de Samsung o TSMC (no obstante, se piensa que TSMC adoptará HNS a 2 nm también, por lo que igualarán a IBM a este respecto). En cuanto al rendimiento, se estima que el proceso de 3 nm de TSMC superará al de 2 nm de IBM.

En conclusión: más bien hablamos de 3 nm «mejorados»

Tras analizar el anuncio de IBM y «jugar» con todos los datos que están disponibles, lo más probable es que en realidad el proceso de fabricación de 2 nm anunciado por IBM se trate más bien de un proceso a 3 nm (de TSMC) desde una perspectiva de densidad de transistores pero con mejoras de eficiencia, si bien en detrimento del rendimiento.

El anuncio de IBM es bastante impresionante, pero es un dispositivo de investigación que solo tiene un beneficio claro en comparación con los procesos existentes de Samsung o TSMC: la eficiencia energética. Para todo lo demás, demuestra ser peor incluso en términos de rendimiento, de nuevo basándonos en estimaciones con los datos empíricos de que se disponen y de los datos proporcionados por IBM.

Además, lo más probable es que TSMC tome de nuevo el liderazgo en la industria en cuanto a densidad, potencia y rendimiento a 2 nm en cuanto su proceso entre en producción entre 2023 y 2024.