En el 26º simposio de tecnología de TSMC, el fabricante dio los primeros detalles sobre su progreso con el nodo N7 a 7 nm, así como los nodos N5, N4 y N3 de 3 nm. TSMC también compartió detalles sobre su nueva tecnología 3DFabric y brindó algunas pistas sobre qué tecnologías utilizará para continuar escalando más allá del nodo de 3 nm. En este artículo te contamos cómo funciona este as en la manga mediante el que TSMC ya está mirando a Intel por el retrovisor.

TSMC ya ha interrumpido el orden jerárquico de la industria de los semiconductores cuando dejó de lado a Intel y Samsung y se trasladó a su nodo de 7 nm líder en la industria, lo que impulsó a los competidores de Intel (AMD entre otros) a la vanguardia. Aun así, la compañía no muestra signos de desacelerar su rápido ritmo de iunnovación y tienes planes para comenzar la producción en masa de su tecnología de 3 nm para 2022 (para ver esto en perspectiva, Intel planea presentar su tecnología de 7 nm a finales de 2022 o principios de 2023).

Los procesos de fabricación de TSMC

El proceso N5 a 5 nm de TSMC emplea tecnología EUV de manera «extensa», y ofrece los beneficios esperados que se obtienen en el escalado de litografía con respecto al N7 a 7 nm. TSMC afirma que el proceso N5 ofrece hasta un 15% más de rendimiento (con el mismo consumo), o un 30% de reducción de consumo a igualdad de rendimiento, con una ganancia de densidad lógica de 1,8X veces sobre el proceso N7. También afirman que la curva de aprendizaje de densidad de defectos para N5 es mucho más rápida que N7, lo que significa que este proceso alcanzará tasas de rendimiento más altas y más rápidamente que su predecesor.

| N5 sobre N7 (7nm) | N5P sobre N5 | N4 (5nm) sobre N5 | N3 (3nm) sobre N5 (5 nm) | |

|---|---|---|---|---|

| Potencia a igualdad de rendimiento | 30% | 10% | ? | 25-30% |

| Rendimiento con el mismo consumo | 15% | 5% | ? | 10-15% |

| Mejora de densidad | 1.8X | ? | ? | 1.7X |

| Riesgo / Fabricación en masa | En producción | Hacia 2021 | 2022 | Segunda mitad de 2022 |

TSMC también cuenta con su nodo mejorado N5P, que está en desarrollo para aplicaciones de alto rendimiento, con planes para producción en masa en 2021. N5P ofrece un 5% más de rendimiento o una reducción del 10% de consumo sobre N5. Según la compañía, ya tienen su próximo chip para servidores en el proceso N5, por lo que está claro que TSMC ya ha superado la mayoría de obstáculos de diseño para los 5 nm.

Debido a la compatibilidad con el nodo N5, el proceso N4 a 5 nm ofrece una migración sencilla con mejoras de rendimiento, potencia y densidad que todavía no han estimado. TSMC no ha dado muchos detalles, pero se sabe que el proceso de fabricación requiere menos capas, y planean comenzar la producción de riesgo en el cuarto trimestre de 2021, llegando a la producción en masa hacia 2022.

La compañía también dijo que su nodo N3 a 3 nm comenzaría la producción de riesgo en 2021 y alcanzaría la fabricación en masa en la segunda mitad de 2022. Este nodo ofrece un escalado completo del nodo con respecto a N5 y traerá una mejora de rendimiento del 10-15%, o una reducción de consumo del 25-30% junto con una mejora de densidad de hasta 1.7X veces. El nodo sigue utilizando la arquitectura FinFET y ofrece un aumento de 1,2X veces en la densidad de SRAM y de 1,1X veces en la densidad analógica.

Los nodos por debajo de 3 nm buscarán alternativas al silicio

TSMC también está trabajando en la definición de su próximo nodo más allá del N3, y compartió algunos de los avances de la industria que podrían ayudarles a llegar más allá de los 3 nm, si bien no nombró las tecnologías que utilizarían. Enumeraron nanohojas y nanocables entre los avances junto con el uso de nuevos materiales, como canales de alta movilidad, transistores 2D y nanotubos de carbono como candidatos en los que ya están investigando.

TSMC tiene más de 15 años de experiencias con tecnologías de nanohojas y ha demostrado que puede producir dispositivos SRAM de 32 Mb de nanohojas que funcionan a 0,46V. También han identificado varios materiales sin silicio adecuados para 2D que podrían escalar el espesor del canal incluso por debajo de 1 nm. Por supuesto, los nanotubos de carbono también entran en sus planes.

Para ello, la compañía sigue profundizando en sus investigaciones y la inversión de 2.960 millones solo en 2019 lo demuestra. Están construyendo un nuevo centro de I+D con 8.000 ingenieros junto a la sede de la compañía, y la primera fase de este proyecto esperan que se complete en 2021.

3DFabric, el as en la manga de TSMC

Reflejando lo que ya hemos escuchado por parte de otros actores de la industria, TSMC cree que las tecnologías de empaque avanzadas son la clave para una mayor escala de densidad, y que las tecnologías de empaque 3D son el camino a seguir. Ahí es donde entra en juego la tecnología 3DFabric.

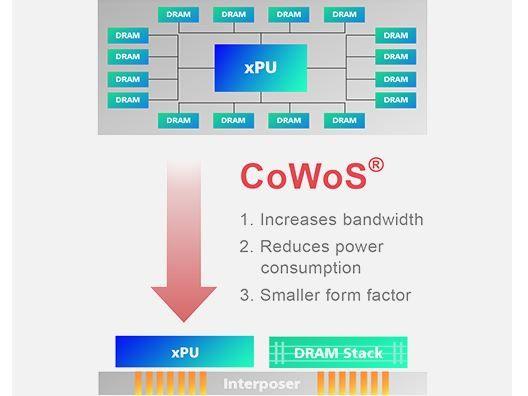

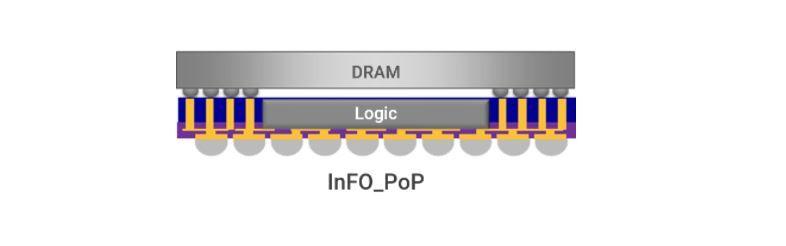

TSMC ya tiene una sólida cartera de tecnologías de empaquetado 3D en sus tecnologías 3DIC a nivel de oblea, CoWoS (Chip-on-Wafer-on-Substrate), InFO-R (Integrated Fan Out), COW (Chip on Wafer) y WoW (wafer on wafer). La compañía ahora está tratando de implementar estas tecnologías bajo el nombre 3DFabric, que parece ser un nuevo esquema de marca para sus tecnologías de empaque 3D que unen chiplets, memoria de gran ancho de banda e IP especializadas en paquetes heterogéneos.

Así pues, en resumidas cuentas 3DFabric es una especie de «familia» que engloba todas las diferentes tecnologías en las que TSMC está trabajando tanto para el nodo a 3 nm como para los que vendrán detrás, y prevén que podrán bajar incluso de 1 nm utilizando esta tecnología.