El mercado de los procesadores gráficos o GPUs, ya sean en forma de tarjetas gráficas como en GPUs integradas se encuentra en estos momentos ocupado por NVIDIA, AMD y en menos medida Intel. ¿Significa esto que no es posible construir una GPU que no utilice tecnología comercial? La solución puede venir en el uso de la ISA totalmente libre y abierta RISC-V, en una variante pensada para gráficos bajo el nombre de RV32X

La gente de Pixilica, creadores de la CPU basada en la ISA RISC-V llamada SiFive han hecho una propuesta llamada RV32X, la cual tiene como objetivo la creación de GPUs haciendo uso de la ISA RISC-V. Lo cual por la naturaleza completamente libre y abierta de RISC-V podría cambiar el futuro de las GPU por completo.

RV32X, aplicando RISC-V para construir una GPU

El estándar RISC-V es un conjunto de registros e instrucciones de uso totalmente libre y abierto que se basa en una especificación base y una serie de extensiones opcionales para la creación de CPUs para diferentes tipos de usos y utilidades. Pero, ¿es posible utilizar RISC-V para crear unidades shader como los SM de NVIDIA o las Compute Unit de AMD? De entrada no y sería necesario una nueva extensión de dicha ISA para utilizarla para crear una unidad shader.

La empresa Pixilica ha propuesto la creación de una GPU donde las unidades shader se basen en la ISA RISC-V y para ello ha propuesto una extensión adicional a la ISA RISC-V con una serie de instrucciones que le permitan manipular primitivas gráficas. Ya sean píxeles, vértices y otro tipo de datos utilizados en el renderizado de gráficos a tiempo real.

Para ello proponen utilizar la extensión de V para instrucciones vectoriales de RISC-V y ampliar la lista de instrucciones a partir de ella con tal de crear la unidad shader.

¿Cuáles son los componentes de una unidad Shader?

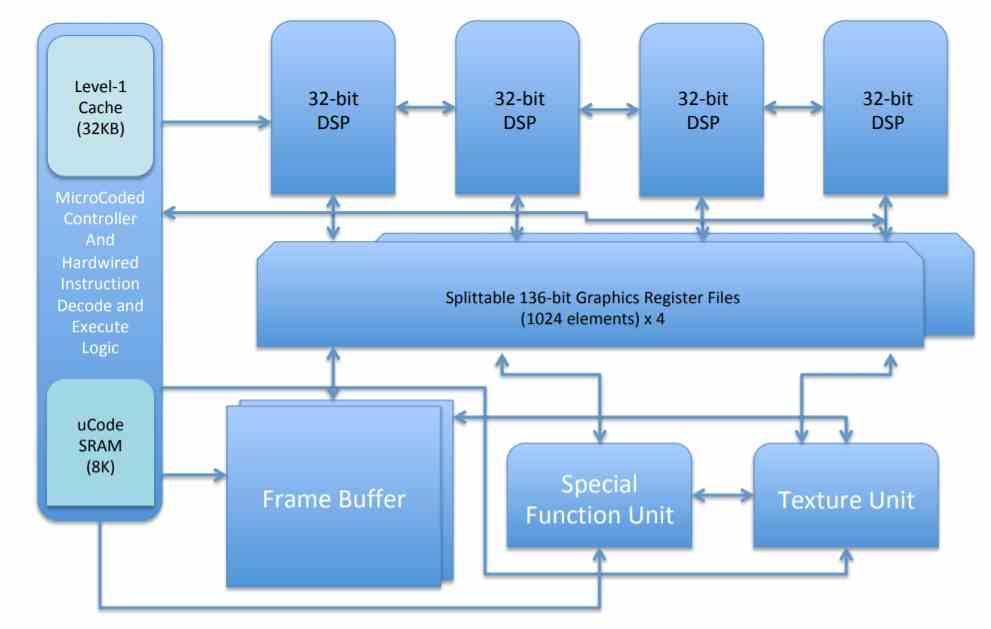

Toda unidad shader, independientemente de la marca que hablemos tiene los siguientes componentes:

- Un descodificador, planificador que toma las olas de hilos de ejecución y las organiza.

- Un pozo de registros, sobre los que el planificador coloca ordenadamente los hilos a ejecutar por parte de las ALUs o unidades de ejecución.

- ALUs o unidades de ejecución con la capacidad de hacer operaciones aritméticas y lógicas sobre los datos. Estas pueden ser vectoriales o SIMD y escalares.

- Unidades de texturas para realizar la interpolación de los píxeles de las texturas. Estas unidades son de función fija.

- Caché de primer nivel para datos

- Capacidad para exportar los datos desde la caché de datos a niveles superiores de la cache, pero más alejados de la unidad shader, y también para exportar a los ROPS

- Una caché de instrucciones que puede ser interna a cada unidad shader o compartirse entre varias.

Una vez conocidas los elementos básicos comunes veamos la propuesta de Pixilica.

El RV32X, una unidad Shader basada en RISC-V

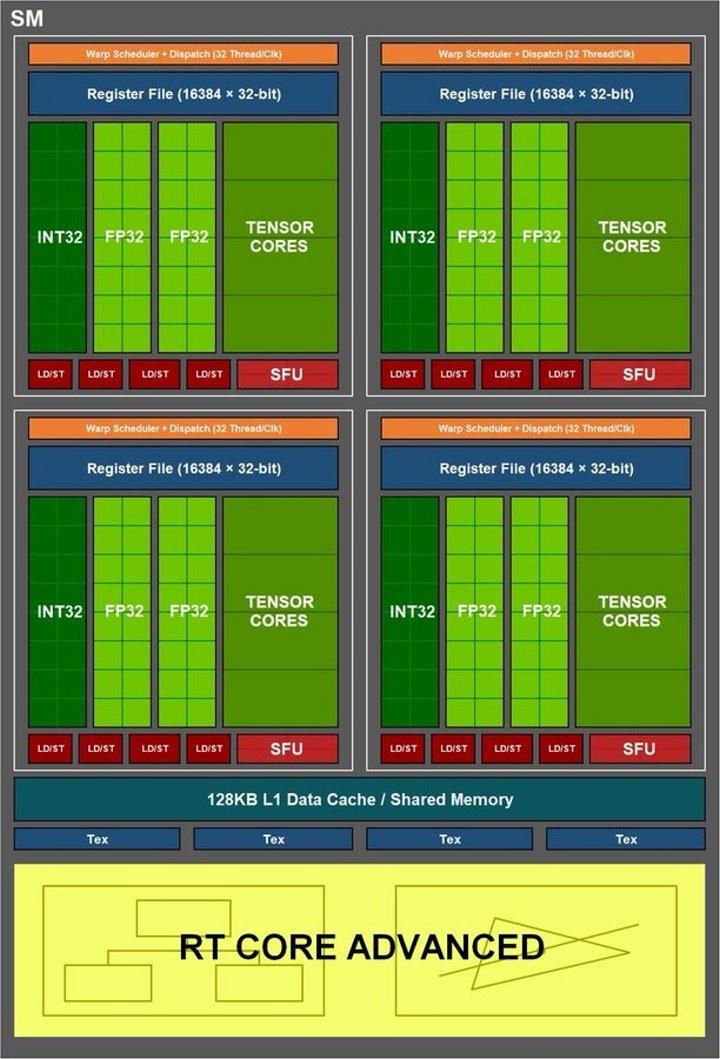

Lo primero que tenemos que tener en cuenta es que el estándar para vectores en RISC-V soporte hasta 128 bits, los cuales se pueden implementar de la siguiente manera: 1 operación de 128 bits, 2 de 64 bits, 4 de 32 bits, 8 de 16 bits o 16 de 8 bits. A esta capacidad de dividir la precisión a la mitad en cualquier ALU lo llamamos SIMD sobre registro. Aunque en el caso que nos ocupa la propuesta es colocar 4 ALUs de 32 bits en coma flotante.

El otro tipo de unidades son las llamadas unidades de función especial, las cuales en el diseño serán escalares y con una precisión de enteros de 16 bits. Las instrucciones que ejecutarían serían las llamadas trascendentales. Es decir seno, coseno, tangente, potencias, logaritmos y raíces de diferentes grados. Los cuales son difíciles de implementar en una unidad SIMD debido al coste en transistores.

Una diferencia respecto a las unidades SIMD utilizadas en una CPU sería que los registros no serían de 128 bits, sino de 136 bits, donde los 8 primeros bits servirían para definir el tipo de primitiva gráfica o de dato a tratar. Los 8 bits permiten hasta 256 tipos de datos, por lo que existe un amplio margen para definirlos, algunos de los tipos de datos le permiten interactuar con las diferentes unidades de función fija que hay en la GPU, así como con la VRAM.

En total tenemos unos 4 pozos de registros, cada uno de ellos 1024 elementos distintos de 136 bits cada uno, el cual el bloque de hilos de ejecución máximo en la actualidad en APIs como Direct3D dentro de DirectX. Cada uno de los pozos de registros está conectado a una unidad SIMD de 4 ALUs de 32 bits en coma flotante. Esto se traduce en 16 ALUs por pozo de registros, lo cual se vería confirmado por el soporte de instrucciones con matrices de 4 x 4 elementos.

Descodificación de instrucciones en el RV32X

La descodificación de las instrucciones vendría en un descodificador de función fija. Se ha de tener en cuenta que las instrucciones serían de 32 bits de longitud y por tanto de tamaño fijo. Estas llegarían a través de la caché de instrucciones, mientras que los datos de cada instrucción estarían en la caché de datos también dentro de la Compute Unit. También es posible el uso de un descodificador de instrucciones por microcódigo.

La propuesta incluye la integración de un núcleo RISC-V estándar acompañando al RV32X, lo que no significa que se transforme en una CPU al uso, sino que sería utilizado para integrar la ejecución Round-Robin típicas de las GPUs, la cual se basa en darle un tiempo de ejecución a cada instrucción. Si no se ejecuta en el tiempo determinado, normalmente por una falta de datos. Entonces se mueve hacía atrás en la lista.

Hay que tener en cuenta que las ALUs de las unidades shader ejecutan las instrucciones de los diferentes hilos de ejecución en cascada según les llegan de los registros. Cuando el planificador ha llenado los registros con los datos de las caches de datos e instrucciones cuando son operados por las ALUs como si fueran una pila, una vez un grupo de instrucciones ha sido resuelta las ALUs leen el siguiente grupo, hasta que se recorren todos los registros y no hay hilos que ejecutar.

Función fija en el RV32X

Las unidades de función fija de la misma manera que el resto de aceleradores no vienen definidos en el RV32X, pero si las instrucciones que permiten la interacción con estas desde las unidades Shader. Dichas unidades se encargan de realizar siempre la misma función, ya que se encuentra cableada o utiliza un microcódigo fijo, pero en todo caso serían unidades completamente aparte del RV32X en su mayoría.

Por lo que cada fabricante tendría sus propias unidades de función fija e implementación de las mismas. Así como también crearía extensiones propietarias en el caso de que estas tuviesen implementadas funciones adicionales sobre el funcionamiento común de las mismas. Hay que tener en cuenta que el RV32X no define una GPU al completo sino una unidad shader que es parte de una GPU, la cual es importante por el hecho que ejecuta los diferentes tipos de shaders, pero no es toda la GPU al completo.

Como apunte, en cuanto a las unidades de texturas tenemos una por pozo de registros. Hay que tener en cuenta que el ratio habitual entre ALUs de las unidades SIMD suele ser de 16:1 en la mayoría de GPUs. Dentro de cada Unidad Shader, solemos ver cuatro unidades de texturas, lo que eleva el ratio a 64 ALUs de 32 bits en coma flotante de media por cada unidad shader.

¿Abre esto una nueva rama en el mercado de las GPUs?

Dejando de lado toda la parte técnica, si miramos en el mercado de los dispositivos PostPC y los SoC que tienen asignados veremos que una gran cantidad de GPUs integradas son totalmente propietarias. Hasta el momento la más utilizada en los SoC hechos en China era la arquitectura Mali, pero con la compra de ARM por parte de NVIDIA esto limita las posibilidades. Qualcomm tiene la arquitectura Adreno en su propiedad, Apple tiene la suya propia también e incluso Imagination con PowerVR supone tener que licenciar a un tercero el uso de la tecnología.

El hecho de que exista la propuesta de una unidad shader basada en RISC-V es clave, ya que va a permitir la creación de nuevas GPUs basadas en un estándar que es completamente libre y por tanto no propietario. Esto significará que se podrán crear nuevas unidades y mejoras que solucionen problemas comunes en vez de buscar la misma solución desde diferentes perspectivas distintas al mismo tiempo.

Si hemos de mirar una potencia mundial que se puede beneficiar de una tecnología así está claro que la primera que nos viene a la mente es China, pero también podemos ver una evolución de AMD, NVIDIA o Intel a utilizar la versión de RISC-V para construir unidades shader con tal de beneficiarse de los progresos en común. De la misma manera que ocurre en el software y el mundo del código abierto.