El chiplet I/O de AMD Zen 2 es de 12 nm, y no de 14 nm como se creía: ¿cómo afectará?

Las informaciones que teníamos sobre AMD y su nuevo chiplet I/O para Zen 2 eran erróneas, lo curioso es que fue AMD la que dispuso dicha información a los medios, por lo que el anuncio de hoy es una sorpresa. Finalmente, dicho I/O no llegará a 14 nm como se esperaba, sino que llega en 12 nm, probablemente fabricado por GlobaFoundries ¿cómo afectará esto a las CPUs?

AMD sorprende con un chiplet de menos nanómetros para su I/O

Era la principal novedad de la arquitectura dejando a un lado el MCM por chiplet, pero sorprende el movimiento de última hora al respecto. La información que AMD facilitó en su momento hacía referencia a un chiplet de 14 nm fabricando por GlobalFoundries, donde ya hablamos largo y tendido sobre él y sobre su acuerdo con la fundición que les ata hasta dentro de unos años en pedidos de obleas de 12 y 14 nm.

No entendimos cómo era posible que los de Lisa Su no optaran por un proceso litográfico más avanzado como es el de 12 nm, ya que tendría ventajas claras frente a los 14 nm y más en una CPU.

Como ya vimos en su momento en los chips de sus GPU al pasar de 14 a 12 nm, la innovación repercutía principalmente en la eficiencia energética, ya que el segundo era una innovación del primero, donde el pitch de los transistores se mantuvo inalterado.

Por ello, dar el salto a los 12 nm en una superficie tan pequeña y densa en transistores como es una CPU tenía el mayor de los sentidos, donde mientras que AMD mantuvo el argumento de sus 14 nm nosotros lo atribuimos al contrato que tenían cerrado con GlobalFoundries.

La noticia supone un salto hacia delante, donde ahora sabemos que los TDPs tan contenidos son también fruto de este paso.

Núcleos más simples, pero I/O más complejo

No hay que olvidar que la reestructuración de la arquitectura ha supuesto cambios muy importantes en la adjudicación de partes tan importantes como el controlador de memoria.

Si nos fijamos en concreto en el I/O, este ahora alberga el controlador de memoria Dual Channel, las líneas PCIe 4.0, Southbridge, puertos SATA y USB, LPCIO y SPI entre otras cosas.

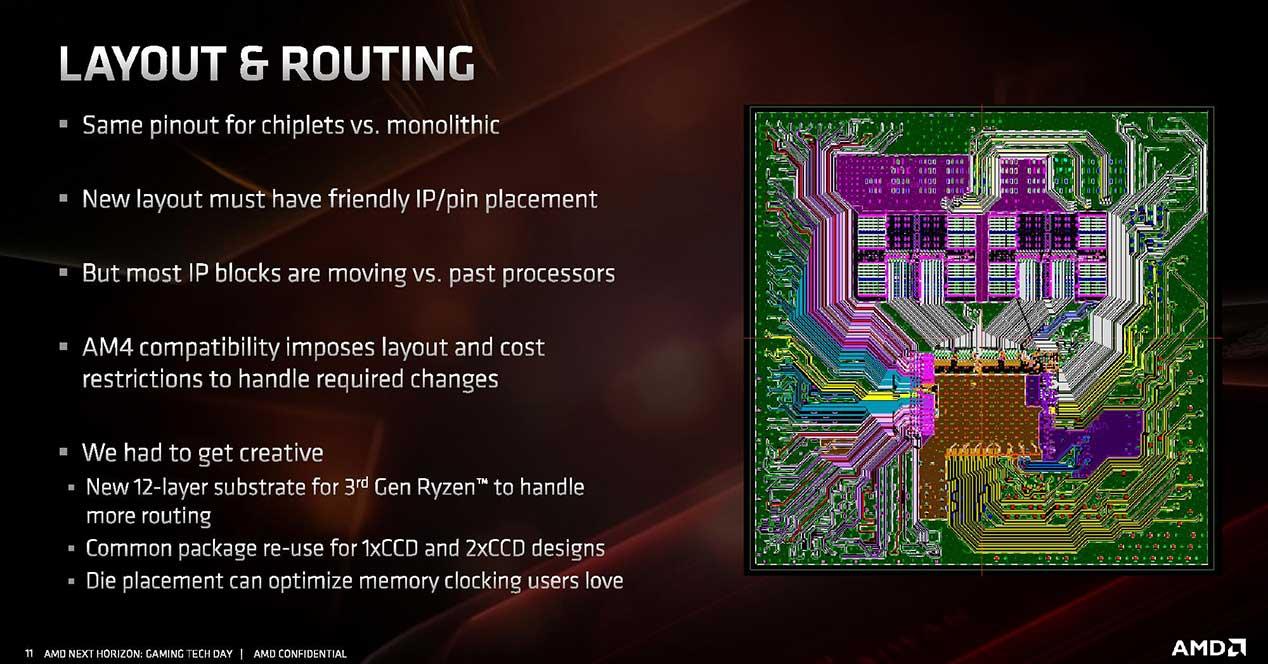

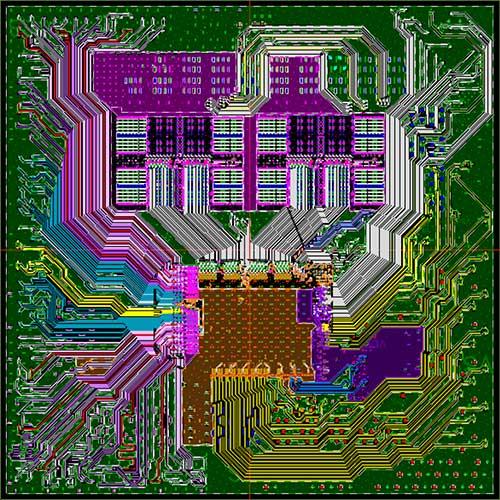

Hoy también sabemos el diseño completo de la reestructuración eléctrica y de conectividad de los chips. Inteligentemente, AMD ha dispuesto los tres chiplets para que las conexiones sean perfectas pin a pin con las generaciones Zen anteriores, todo a base de matrices monolíticas, también llamado LAYOUT & ROUTING.

Esto quiere decir que el pinout es exactamente el mismo en los chips monolíticos que en los sistemas que usarán chiplets, es decir, entre Zen y Zen+ frente a Zen 2. Para ello, AMD ha tenido que usar 12 capas de sustrato par añadir más rutas entre ellos y así poder conectar todos los chiplets y pines.

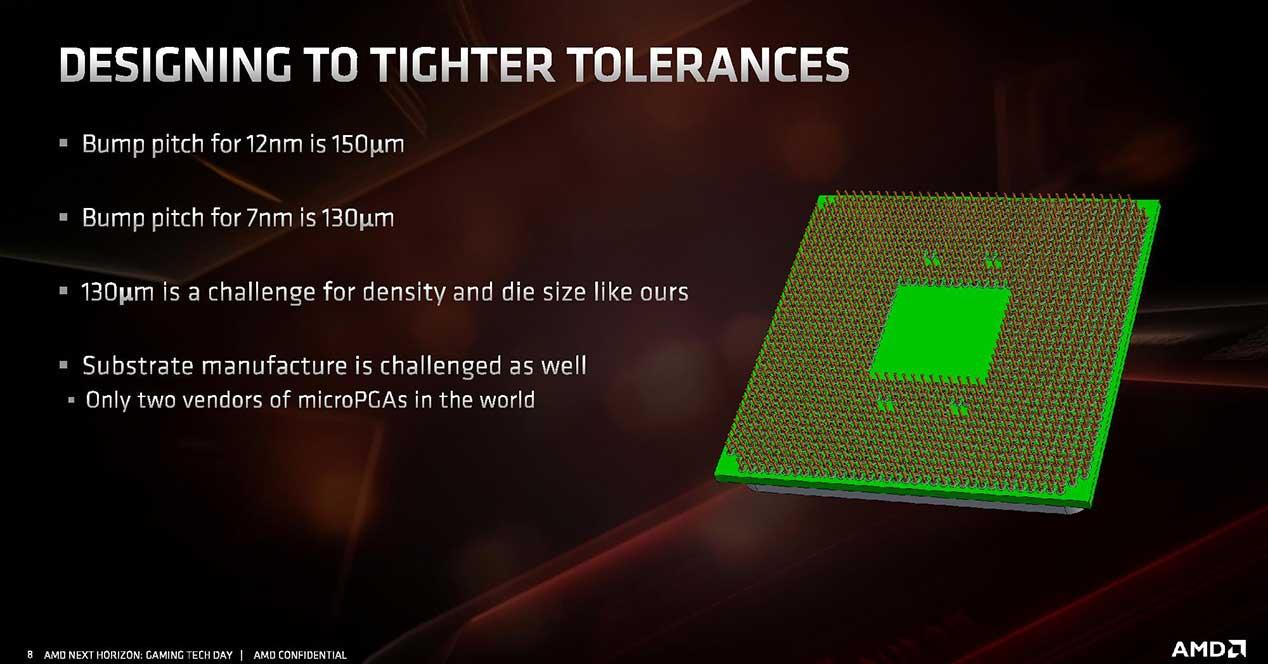

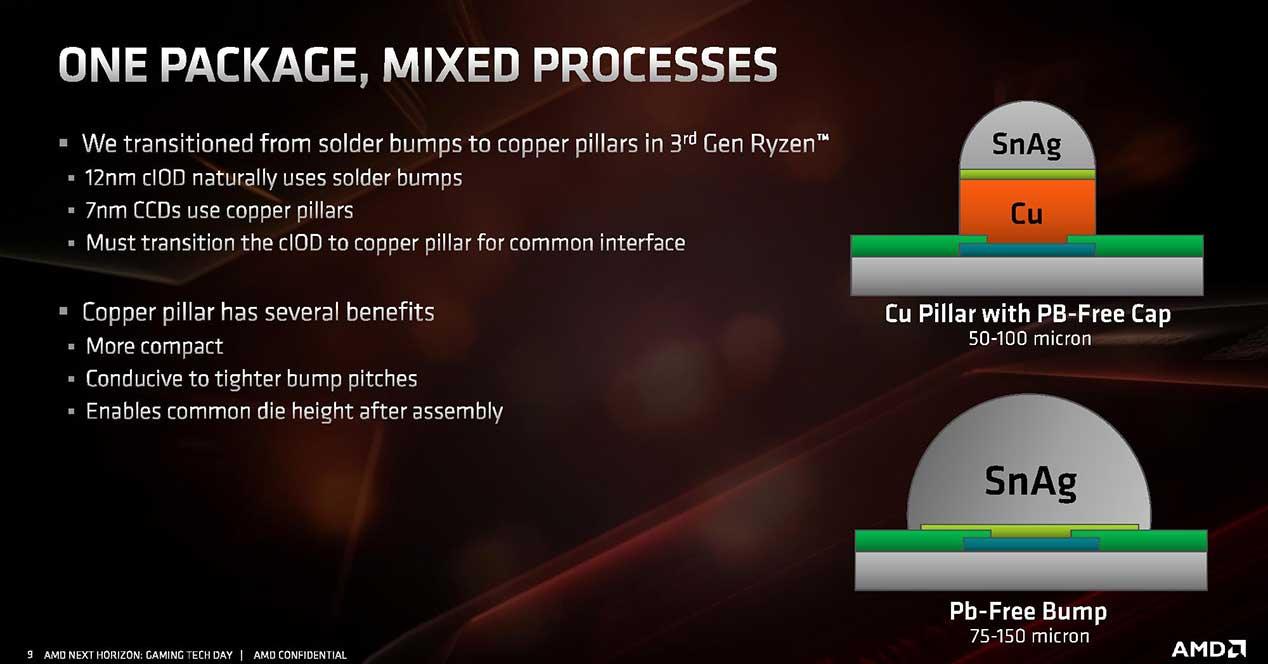

Este diseño prescinde de interposer y TSV, es un diseño unibody sin interconexiones clientelares entre matrices, gracias en parte a la mayor densidad pero también a las nuevas soldaduras que AMD ha implementado en tamaños de entre 50 y 75 µ.