En una conferencia qué ha dado Intel en China, el presidente del Centro de investigación qué tiene la compañía en dicho país ha hablado de los objetivos que tienen de cara a 2030 y que se pueden resumir en hacer chips cada vez más pequeños HP y que consuman cada vez menos. Lo que se traduce en mayor número de transistores y mayor eficiencia energética. ¿Cómo pretenden conseguirlo?

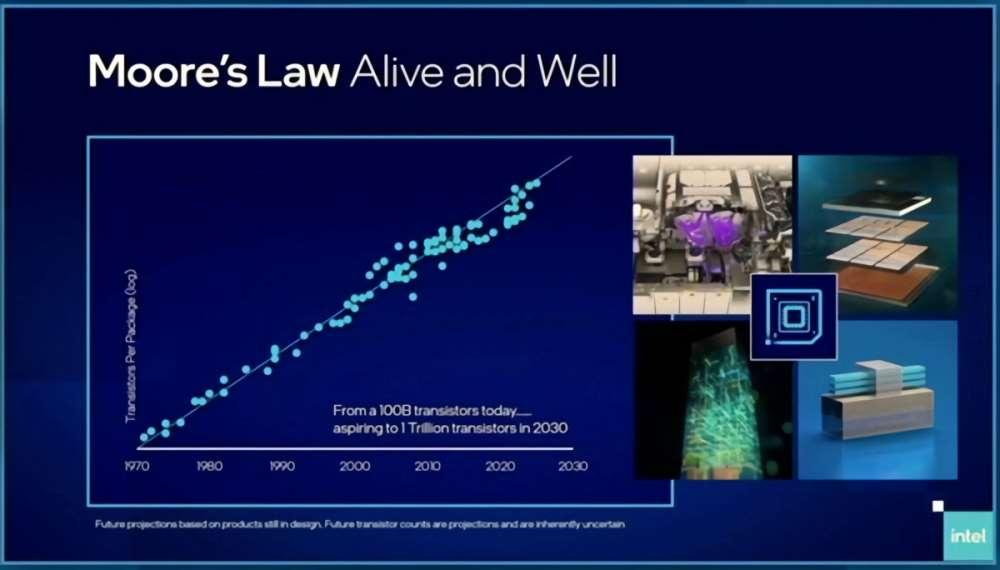

La ley de Moore, la cual fue acuñada por el fundador de Intel y tampoco se puede decir que sea una ley, sino más una observación, suele estar malinterpretada dado qué muchas veces se confunden conceptos sobre la misma. En todo caso, hay que dejar claro que la misma no hace referencia ni a la economía de los chips ni a la potencia de los mismos, sino a la densidad de transistores en un espacio dado que se duplica cada cierto tiempo. Si bien esta sí ha ido haciendo más lenta con el tiempo, la realidad es que a día de hoy sigue vigente.

Chips de un trillón de transistores para 2030 por parte de Intel

Para los que seguimos el avance del mundo de los chips, o sea de los semiconductores, tenemos muy claro a día de hoy que el futuro de cara a poder duplicar la densidad de los transistores cada cierto tiempo pasa por el uso de nuevas técnicas de fabricación y diseño, en especial conceptos como chips disgregados, y el uso de estructuras en tres dimensiones, es decir, apilando chips uno encima del otro y todo ello para hacer chips que serán hasta 10 veces más eficientes y que albergar en su interior hasta un billón de transistores.

En la actualidad el chip más complejo que se utiliza en PC es el AD102 de NVIDIA, que nosotros que la GPU central de las RTX 4090, que tiene una densidad del 7,6% respecto a ese objetivo, por lo que estamos hablando de un tiempo bastante largo a qué Intel consiga ese objetivo, es más, se han planteado conseguir llegar a ello en el 2030 aunque no sabemos si lo harán en sus CPU Core o, por el contrario, en sus GPU ARC. No olvidemos que los llamados microprocesadores disgregados, o chiplets, permiten romper el límite de retícula de la oblea y sacar composiciones con mayor número de transistores que en un chip monolítico.

En todo caso hemos de tener en cuenta que una vez que se manden los chips de una sola pieza el panorama habrá cambiado completamente, ya que significará el uso obvio de chips más pequeños, lo cual se persigue también por el aumento de costes que tiene cada nodo de fabricación de chips nuevo.

Una orden de magnitud de mejora en eficiencia energética

Si ya hablamos de la eficiencia energética, lo que tenemos que tener en cuenta es que dichas palabras, pese a ser un objetivo loable de cara a cosas como reducir la huella de carbono. No podemos olvidar que desconocemos la potencia con la que quieren medir este parámetro y el tipo de hardware así como las pruebas de rendimiento que piensan usar como referencia o en su defecto hoy parámetros como la casa de instrucciones por segundo, la potencia en coma flotante, etcétera.

Se trata de un objetivo que no le será fácil de conseguir y que requerirá la implementación de desarrollo de varias tecnologías, muchas de ellas todavía en desarrollo y otras de pronto despliegue. Estamos hablando de cosas como los transistores tipo RibbonFET para densidades de 2 nanómetros o inferiores, las fuentes de alimentación Power VIA, el uso de sistemas litografía avanzada que por el momento son de uso inédito y nuevos sistemas empaquetamiento de chips similares a Foveros.