Intel comienza a implementar PCIe Gen 4.0 en sus FPGA con chiplets HBM2 y UPI

Intel en muchos apartados está yendo a remolque de AMD, pero se está poniendo al día a un gran ritmo. Uno de los aspectos comunes que más se le está criticando tanto en el mercado de escritorio como en el de servidor es la ausencia del bus PCIe Gen 4.0. Por ello, los de Swan han anunciado que su Stratix 10 DX ya incluye dicho bus PCIe Gen 4.0 y además integran UPI.

El ancho de banda se está volviendo crucial en los servidores

La gama EPYC Rome tiene un gran punto a favor a la hora de trabajar con el ancho de banda del PCIe, ya que implementa su versión 4.0 y permite que diferentes dispositivos trabajen en tándem con un mayor rendimiento que el ya veterano PCIe 3.0.

Sin embargo, Intel parecía que se lo estaba tomando con calma y ha llegado a decir que la nueva versión del bus no es necesaria en escritorio, donde llevan razón en gran parte.

Pero en servidores todo es distinto, el nivel de información que se maneja es apabullante y cualquier mejora siempre es bienvenida.

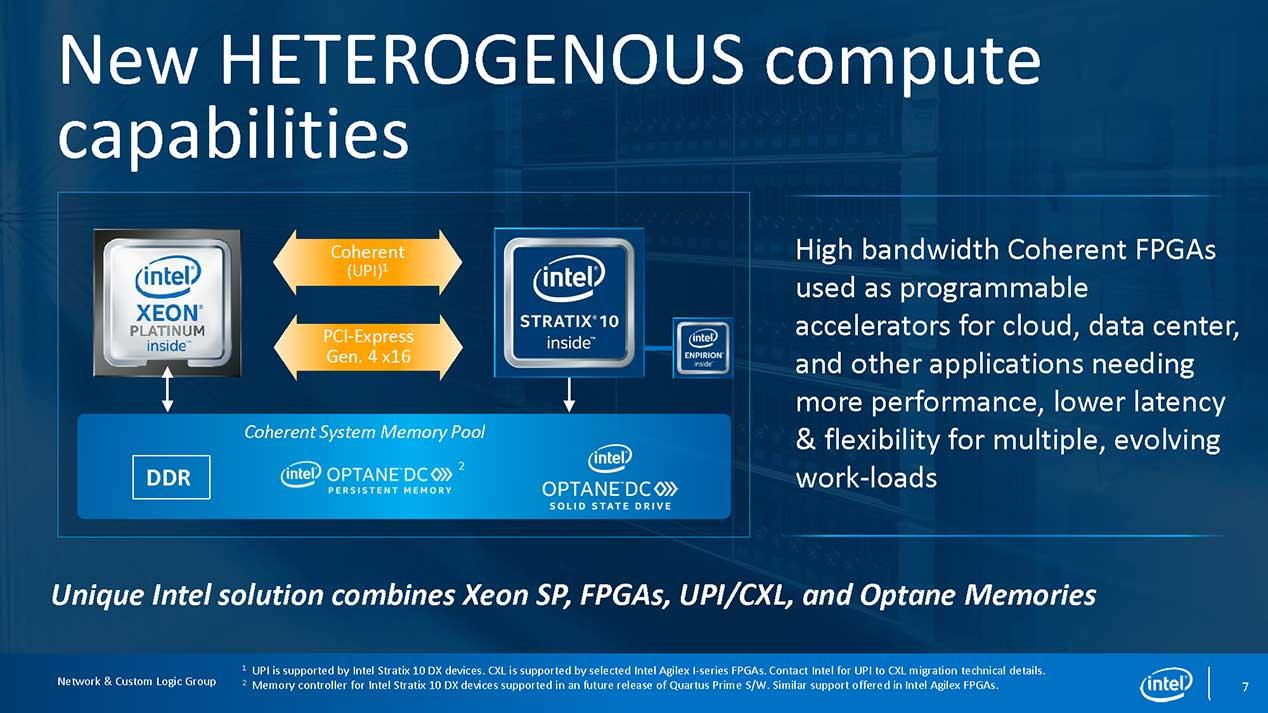

Uno de los componentes que más se están usando en los últimos años son los FPGA, los cuales se están usando como aceleradores y un nexo de interconexión entre CPU y memoria, los cuales agilizan tareas específicas.

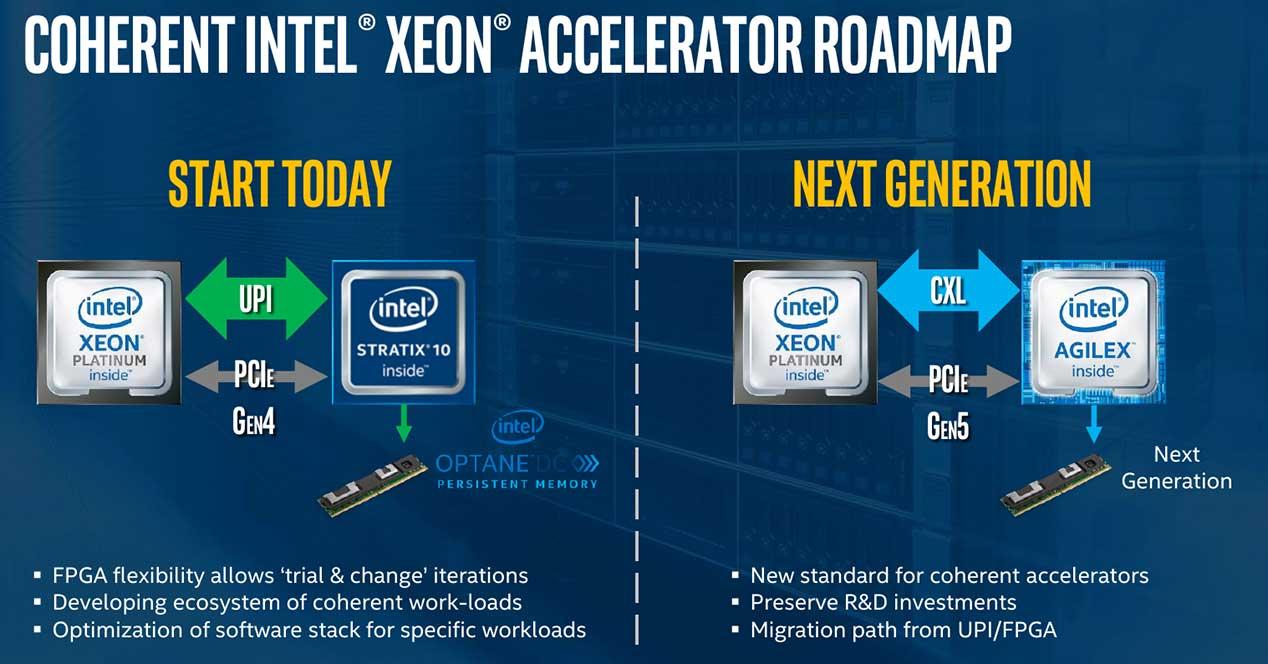

Aquí es donde entra Stratix 10 DX, ya que es el último FPGA de Intel y el cual soporta la tan buscada coherencia de caché. Para brindar este sistema Intel ha incluido UPI (Ultra Path Interconnect) el cual le permite conectarse directamente a los procesadores Xeon a una velocidad de 11,2 GT/s por enlace (22,4 GB/s en total).

Pero, ¿por qué Intel no usa para ello el bus PCIe? Según la compañía, UPI permite una latencia un 37% menor en las tareas de coherencia de memoria debido a que es una interconexión específica para ello.

Stratix 10 DX, diseño basado en chiplets con PCIe Gen 4.0

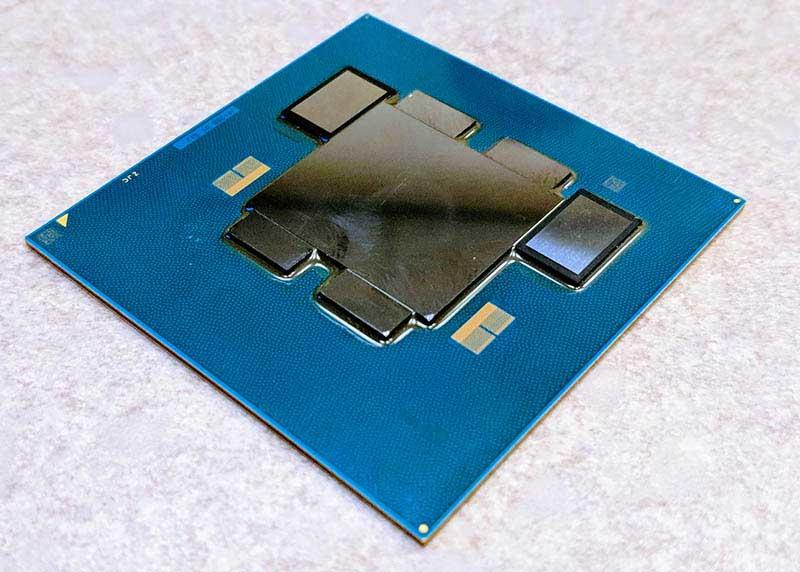

Es bien sabido que Intel ya estaba trabajando en implementar chiplets como paso intermedio de Foveros y la arquitectura Lakefield.

Stratix 10 DX llega como el primer FPGA de Intel en implementar en un solo PCB 4 pilas de HBM2 y dos transceptores, lo cual es un paso bastante grande de los de Swan para el poco tiempo que han tenido desde su presentación.

Para el tráfico no coherente y dadas las prestaciones del FPGA, Intel ha implementado por primera vez en uno de sus sistemas el bus PCIe Gen 4.0, donde el controlador de memoria de Stratix 10 DX conectará la HBM2 y al propio sistema con dispositivos Optane (si estuvieran instalados).

Intel ofrecerá Stratix 10 DX en tres versiones: DX 1100, DX2100 y DX 2800, donde el mayor de ellos será el que porte los 2X4 GB de HBM2.

El siguiente paso de Intel es todavía más radical, ya que piensa prescindir de UPI y PCIe Gen 4.0 para dar vida por primera vez a CXL y PCIe 5.0, donde sus FPGA Agilex serán los primeros del mundo en implementar esta tecnología, la cual mediante su consorcio aúna a las principales empresas del mundo, incluida recientemente AMD entre ellas.