«Samsung está por delante de TSMC en GAA por aproximadamente 12 meses y dos o tres años por delante de Intel.» Esto fue lo que afirmó Handel Jones, director de International Business Strategies, y es que Samsung presentó su mayor innovación hasta la fecha: su proceso de 3 nm con un nuevo enfoque para los transistores y procesadores, al que ha puesto por nombre 3GAE y que llegará maduro y en masa en 2021.

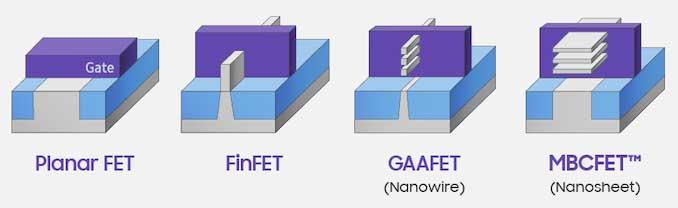

FinFET dejará paso, tras una década, a GAAFET y MBCFET

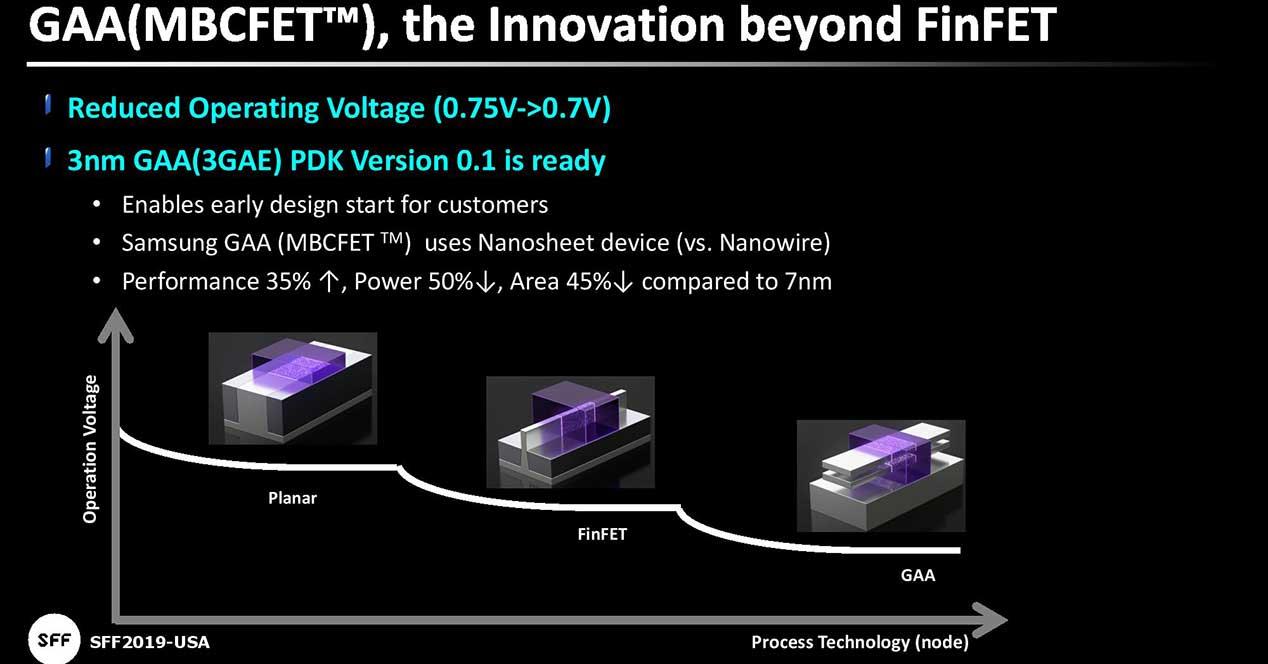

Los procesos litográficos basados en FinFET tienen las horas contadas, si bien ayudaron al diseño de transistores con un mejor desempeño y escala de voltaje aumentando el área de contacto entre el canal y la Gate en vertical, ahora debe dejar paso a un nuevo tipo de diseño para transistores que permitan una mayor escalabilidad.

El paso lógico es aumentar el área de contacto una vez más entre el canal y la Gate (puerta), donde para ello Samsung ha creado y definido como diseño Gate-All-Around o GAA, un concepto que se podría entender como un ajuste de las dimensiones del transistor para que las Gate se apilen verticalmente, permitiendo al mismo tiempo que los transistores hagan lo mismo.

Los FET de nueva generación basados en GAA (GAAFET) llegarán al principio en procesadores de baja potencia, debido a que el primer diseño se realizará con anchos de canal pequeños, lo que ofrecería Gates del mismo ancho. Para aumentar el rendimiento estos canales y Gates deben de ampliarse siendo el siguiente paso de evolución de los transistores.

Dicho paso se basa en nano-sheet (hojas) apiladas de nuevo verticalmente, lo que daría un nuevo proceso llamado Multi-Bridge Channel FET o MBCFET, según la propia Samsung.

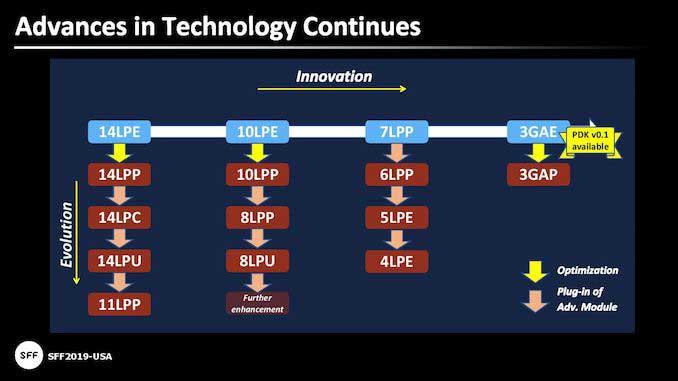

La compañía afirma que los primeros PDKs (product designs kits) están listos, por lo que las empresas que deseen comenzar a diseñar chips bajo este proceso litográfico podrían trabajar desde ahora para sus productos de baja potencia. Estos PDKs van mejorando con el paso del tiempo, haciendo más sencillo el diseño de chips o mejorando de forma sencilla su construcción.

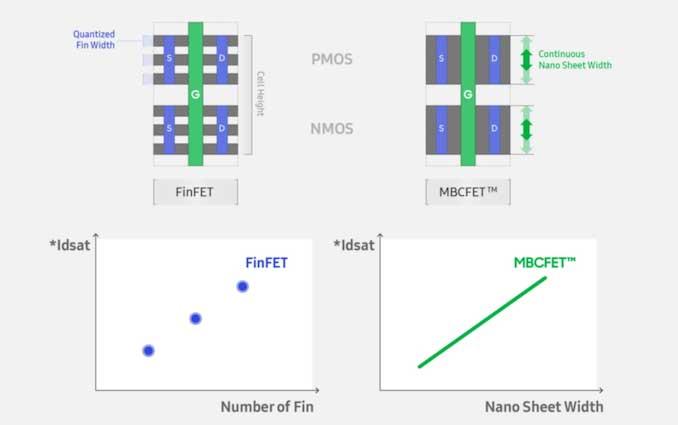

Mayor ancho, mayor rendimiento, MBCFET es el futuro

Como hemos dicho, a mayor ancho del canal/Gate mayor rendimiento (nano sheet), por lo que es importante que los PDKs que suministra la fundición estén muy claros en este aspecto y tengan opciones distintas para ajustarse al consumo de energía, ya que a mayor ancho mayor rendimiento y mayor potencia necesaria.

La ventaja que presenta MBCFET es que no solo admite perfiles concretos o puntos de diseño específicos como FinFET, sino que es una escala continua que el fabricante puede ofrecer si lo precisa.

El diseño de la primera generación de 3 nm bajo MBCFET será conocido internamente como 3GAE, donde como hemos dicho ya hay disponible un PDK en versión Alpha para su proceso, pero ¿qué aporta realmente estos 3 nm frente a, por ejemplo, los 7 nm actuales de Samsung?

La propia compañía nos ofrece una serie de datos concretos bastante impresionantes. En primer lugar, consiguen disminuir el voltaje de operación de 0.75V a 0.70V, esto implica un 6,66% de reducción de energía a mismo proceso litográfico. Pero esto es solo un pequeño paso para lo que ofrece este nuevo nodo litográfico, ya que según Samsung y en segundo lugar, estos 3 nm GAA (3GAE) ofrecerán un 1.35X de rendimiento, una reducción del consumo de energía total del 50% y un área de matriz con una mejora del 45%, es decir 0.65X.

3GAE llegará con a finales de 2021

Samsung espera que las primeras obleas lleguen a los clientes en 2020, donde a finales del año que viene llegaría su «producción en riesgo» para finalmente llegar en volumen de fabricación global en 2021.

Pero no se detienen aquí, ya que la segunda generación de 3 nm conocida como 3GAP y con un enfoque de alto rendimiento (que es lo interesante), llegará como producción de riesgo en 2021 y una producción en masa fijada para 2022.

Esto explicaría los últimos rumores que situaban a NVIDIA con Samsung para la próxima generación de tarjetas gráficas a 7 nm y posteriores, donde visto esto y el avance que tiene actualmente la empresa, es posible y factible pensar que un supuesto acuerdo se cierre para varios años, garantizando con ello la prioridad sobre estos y futuros procesos litográficos.

En cualquier caso, Samsung está demostrando que TSMC se puede quedar atrás en apenas dos años, no digamos Intel, ya que, aunque no se han ofrecido datos exactos de densidad, el gigante azul tendría complicado actualmente conseguir casi un 50% de mejora en apenas 24 meses, ni siquiera con EUVL. ¿Se están quedando Intel y TSMC atrás como afirma Handel Jones?