EL MIT y la Universidad de Stanford quieren hacer obsoleto el bus de datos

Las universidad del Stanford y los investigadores del MIT de Massachussets han aunado sus fuerzas. Para crear el primer procesador que carece de bus de datos para el procesador. Y para hacerlo han recurrido al grafeno en lugar de usar el tradicional silicio. El resultado ha sido un prototipo que mezcla en el mismo cuerpo el núcleo con la memoria RAM.

Normalmente, la comunicación entre el procesador de un ordenador y la memoria RAM de un sistema se produce a través de un bus, que es esencialmente una carretera de comunicación entre datos almacenados en la DRAM y los datos que el procesador necesita para procesar / acabar de terminar el procesado. La CPU y la RAM más rápidas son todavía tan rápidas como el bus, y las cargas de trabajo recientes han aumentado la cantidad de datos a procesar (y por lo tanto transferidos) por varios órdenes de magnitud. Como tal, los ingenieros han estado tratando de encontrar formas de aumentar la velocidad de comunicación entre el procesador y el subsistema de memoria. Ya que parece cada vez más probable que los próximos cuellos de botella en HPC no proceden de una falta de rendimiento del procesador o de la memoria. Más bien vienen del cuello de botella entre ambos.

Eliminando el bus de datos, se acabó el problema

¿La solución del MIT y de los investigadores de Stanford? Acabar con un bús por completo. Entrelazando el procesador y la memoria juntos tan estrechamente que no hay posibilidad de crear cuellos de botella. De acuerdo con el autor principal en el trabajo de investigación, Max Shulaker,

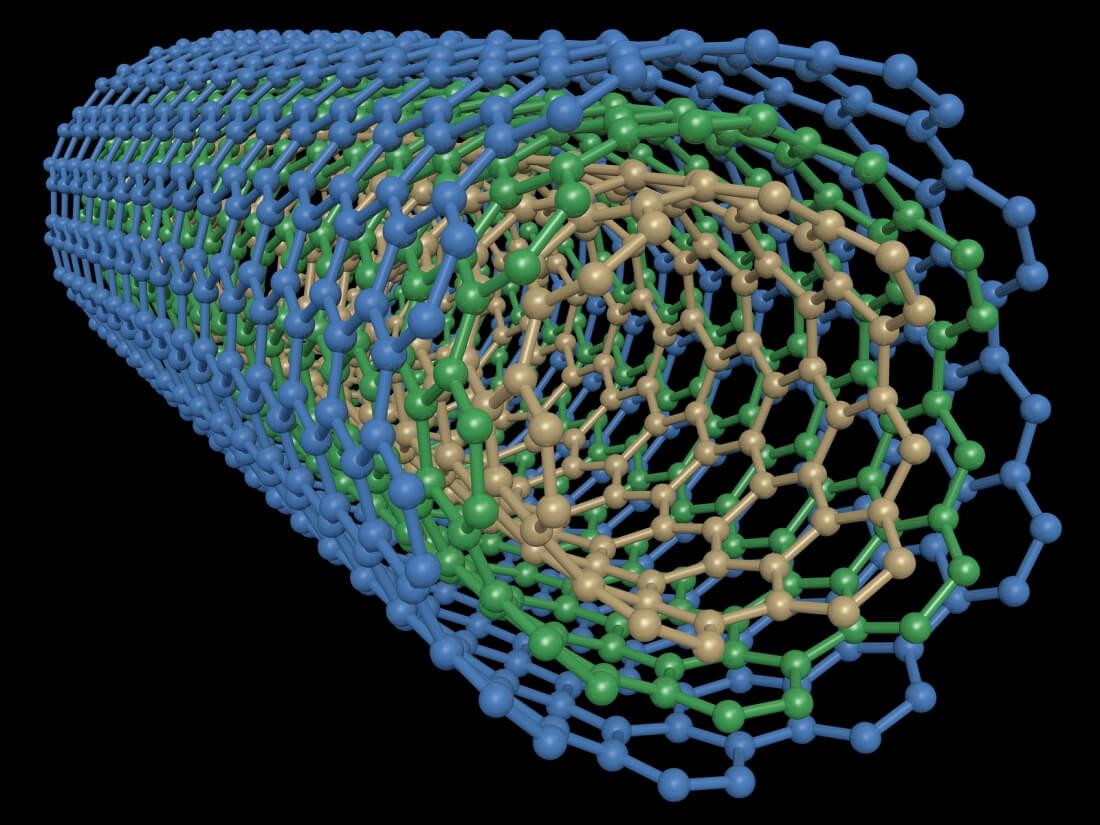

«El RRAM y los nanotubos de carbono se construyen verticalmente unos sobre otros, haciendo una nueva, densa arquitectura informática tridimensional con capas de intercalación de la lógica y la memoria.Al insertar cables ultradensos entre estas capas, esta arquitectura tridimensional promete solucionar el problema del cuello de botella de la comunicación.»

Como prueba de concepto, el equipo ha producido una computadora de nanotubo de carbono a pequeña escala (CNT), y consigue esto: era realmente capaz de ejecutar programas, un programa básico El sistema operativo multitarea y la realización de instrucciones MIPS. El emparejamiento con RRAM (Resistive Random Access Memory) es una hazaña en sí mismo, dado que la RRAM puede ser más densa, más rápida y más eficiente en consumo de energía en comparación con la DRAM.

Uno de los principales beneficios de la fabricación de los nuevos chips de computadora de grafeno se debe a las temperaturas. Mucho más bajas involucradas en la fabricación. Y es lo que hace que un matrimonio entre un procesador y su memoria sea casi imposible a través del silicio. La creación de chips de silicio requiere temperaturas de hasta 1.000 grados centígrados. Por lo que es difícil hacer capas múltiples y estructuras 3D sin dañar las capas anteriores. Sin embargo, los circuitos de nanotubos de carbono y la memoria RRAM pueden ser fabricados a temperaturas mucho más bajas, por debajo de 200 °C. Lo que permite el apilado y la interconexión de la memoria y la CPU a través de cables finos.