Muchos han sido los rumores y filtraciones que llevamos de Zen 3, pero en realidad la información ha sido dada con cuenta gotas y realmente no hemos avanzado en cuanto a detalles más concretos, hasta ahora. Nuevas filtraciones revelan el aumento de IPC real que AMD obtendría con Zen 3, su fecha de lanzamiento y el posible uso de DDR5 y PCIe 5.0 en Milan, así como un rendimiento dispar conforme se aumenta el número de núcleos,

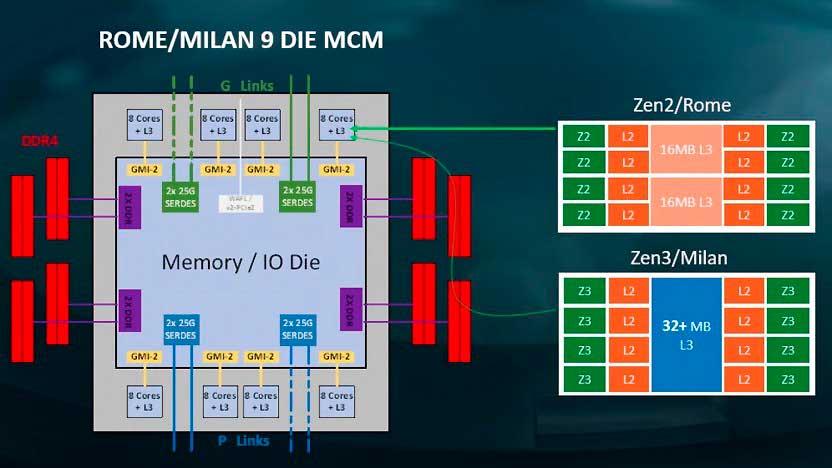

Para entender en qué punto estamos con Zen 3 tenemos que tirar un poco de hemeroteca, ya que la información llega muy espaciada en el tiempo y es fácil perderse. Los primeros datos sobre esta arquitectura llegaron de la mano de la unificación de las memorias cachés L3, lo que da un curioso resultado, ya que aunque el tamaño se mantiene en general, la caché L3 será el doble por la unificación de dos CCX en un CCD. ¿Es una ampliación? Sí, parcialmente, misma caché, más tamaño disponible y menor latencia.

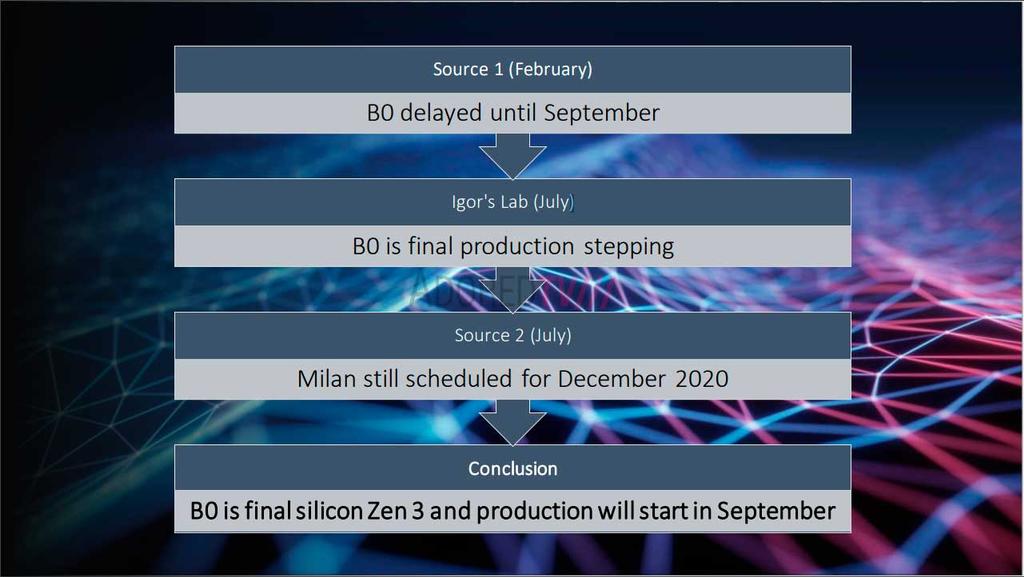

Más tarde conocimos las dos versiones filtradas como muestras de ingeniería en versiones A0 y B0, donde las primeras llegaron con clocks muy bajos y en algún caso sin SMT activo. Las segundas son probablemente muestras mucho más capaces y que reflejarían estar a un paso de las versiones comerciales finales, con un poco menos de frecuencia. Entonces, ¿qué hay de nuevo?

AMD retrasa la llegada de Zen 3, pero conseguirá lanzarlo en 2020

Aquí hay que hacer otro inciso, puesto que se estuvo especulando que AMD no llegaría a lanzar Zen 3 en 2020 por el COVID-19. Esto parece que finalmente va a ser descartado, aunque el roadmap interno parece desplazarse hacia final de año realmente y de ahí dichos rumores.

Al parecer, la fecha de presentación será en algún momento de septiembre y la producción en masa comenzará a partir de ese momento, por lo que podrían llegar al mercado entre octubre y noviembre si todo va correctamente.

Un segundo roadmap mostraba al parecer una línea temporal anexa de AMD, donde se especulaba para este tercer trimestre y, curiosamente, tras el anuncio de Micron y JEDEC, que Milan podría tener una variante con DDR5 y PCIe 5.0 exclusiva para servidores HPC, por lo que se adelantaría en este aspecto a Intel con Sapphire Rapids, pero es de momento solo un rumor, aunque muy interesante.

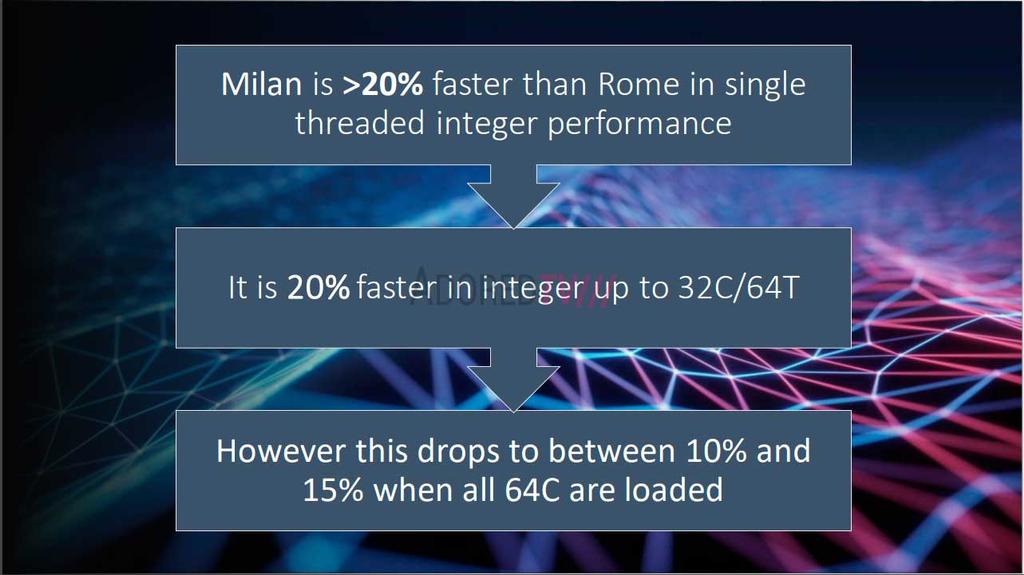

En cuanto a las ganancias de rendimiento, siempre se compara a Milan con Rome, no a Vermeer con Matisse, esto es importante. Y lo es porque el número de núcleos parece que va a determinar el aumento de rendimiento así como la escalabilidad.

Los datos de IPC pueden no ser tan optimistas

Al hablar de IPC hay que hacerlo desde un mismo punto de vista en cuanto a cargas de trabajo se refiere, es decir, hay que comparar el rendimiento de enteros con enteros o flotante con flotante. Es un problema de cálculo de ganancias según lo que se esté midiendo, por lo que podemos encontrar diferentes aumentos de IPC según donde miremos.

Las fuentes informan por tanto que Zen 3 sería un 20% más rápido en cargas de trabajo bajo enteros y en un solo subproceso, pero esto para una versión de 32 núcleos en un chip. Si aumentamos el número de núcleos hasta 64 (versión tope de gama en Milan) el aumento de IPC en enteros sería de entre un 10 y un 15%.

En este punto no está claro si dicha disminución viene aportada por un menor clock general o por algún tipo de cuello de botella. Lo que sí confirman son las ganancias generales de la arquitectura, que a fin de cuentas es lo que realmente interesa: +15% en enteros y menos del 10% en flotante.

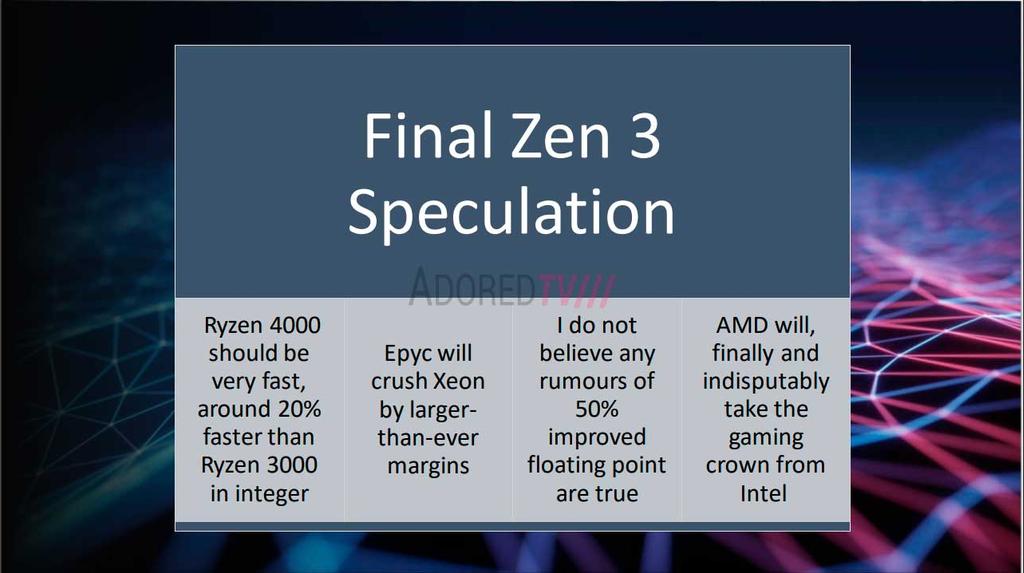

En general, si comparamos Zen 3 con Zen 2, afirman que la ganancia de IPC está en un punto entre el 10% y el 15%, peores números que los de hace meses (+15%). En cualquier caso, estos datos son suficientes para asegurar que AMD se pondría por delante en los dos apartados donde sigue por detrás: portátiles gaming y gaming desktop en general.