Si hay alguien que esté apretando las tuercas a Intel y Samsung es TSMC. El fabricante taiwanés ha estado callado durante algunos meses, esperando agazapado a presentar sus futuras armas y a dar plazos concretos. Ha sido en el simposio de tecnología anual de la empresa donde ha presentado toda su artillería y como era de esperar, la compañía va a dejar a Intel y Samsung obsoletas antes que presenten sus nuevos nodos de 5 y 3 nm.

Como si hablásemos del ritmo de un tambor, así se ha presentado TSMC, con aires de guerra, reivindicándose y ajustando unos plazos que sus competidores no van a poder seguir. Vamos a conocer la hoja de ruta y las mejoras que trae la compañía en sus nodos, de los cuales tanto AMD, Apple o NVIDIA van a verse beneficiados.

TSMC 5 nm, el sustituto natural de los 7 nm actuales, pero más avanzado

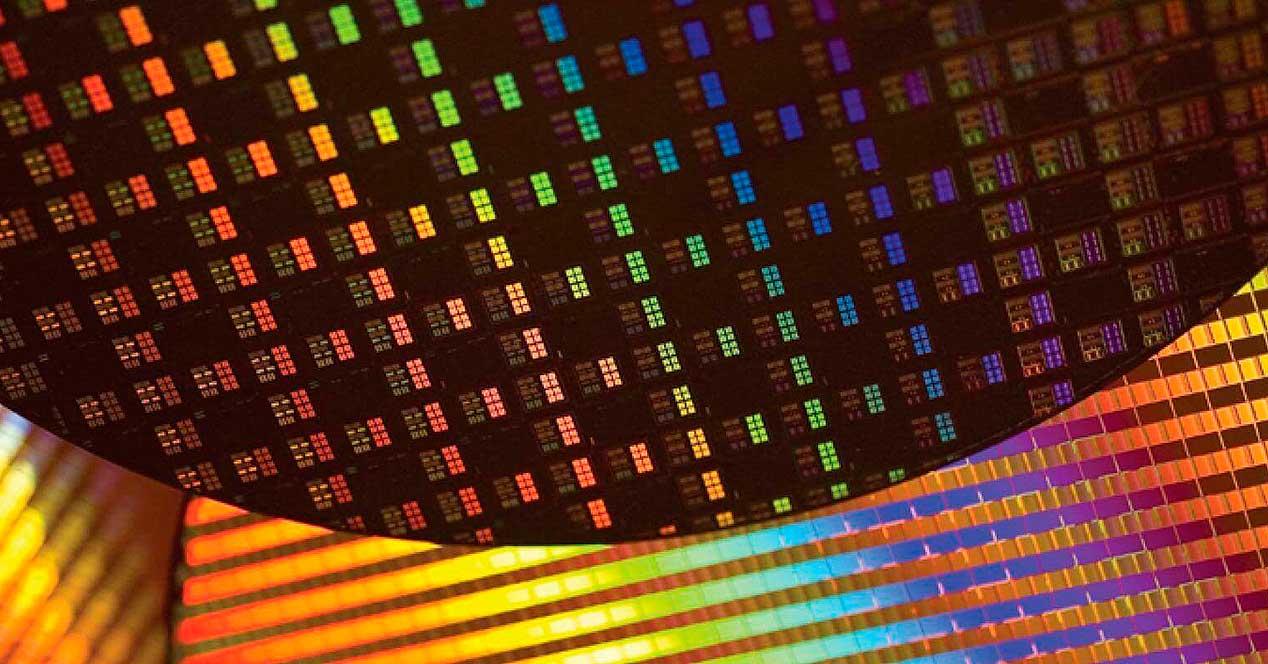

No hay demasiadas novedades en lo que respecta al nodo de 5 nm de la compañía. Como bien adelantamos hace meses, el proceso está en producción en masa y muy probablemente Apple ya esté haciendo buen uso de ello. Este N5 es bastante más eficiente que el N7 y N10 anteriores, hasta el punto que la compañía asegura tener un cuarto menos de defectos que dichos nodos ya veteranos. Por si esto no fuera suficiente N5 ofrecerá hasta un 15% más de rendimiento a misma potencia o un 30% de reducción de energía a mismo rendimiento, todo con una densidad lógica de +1,8x.

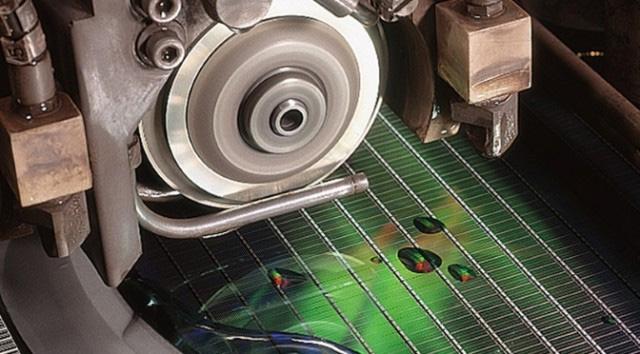

En otras palabras, hay un 25% menos de defectos por oblea y esto hace que la compañía tenga un mayor rendimiento, lo cual dicho sea de paso, solo puede ir a mejor. Hasta tal punto tienen controlada la tecnología EUV que están preparando su sucesor natural: N5P, el cual ampliará el rendimiento y mejorará la eficiencia.

Los datos son claros, +5% en velocidad y un 10% en ahorro de energía. Lo malo es que no hay fecha concreta sobre este nodo. Donde sí la hay es en su sustituto natural, el llamado N4, el cual usará más capas EUV para reducir el número de máscaras en juego, lo que facilitará la migración de los diseños para sus socios.

La producción de riesgo de este N4 llegará en el 4T21 y su producción en masa será en algún punto de 2022.

TSMC 3 nm, el mata gigantes

Si N5 ya es un nodo más que apetecible por cualquier empresa de chips, el N3 va a ser sin duda otra vuelta de tuerca en el sector. Y eso que no contará con los nuevos transistores GAA, por lo que TSMC se mantendrá en FinFET hasta ese momento. A cambio, la empresa asegura que contará con unas «características innovadoras» que les ha permitido llegar a unos números realmente sorprendentes si lo comparamos con N5.

Así, N3 ofrecerá entre un 10 y un 15% más de rendimiento a mismo nivel de potencia, o en cambio podremos reducir la potencia en un 25 o 30% a mismas velocidades que su predecesor. En cuanto a la mejora de densidad, hablamos de entre 1,7x y 1,8x en el mejor de los casos.

Como bien sabemos, esta mejora de la densidad no se dará en todas las partes de cada chip, ya que la escalabilidad se determina según su SRAM y relación lógica, pero la compañía espera una contracción media del 26% aproximadamente.

Quizás lo más impactante de esto sean sus fechas de entrega, ya que N3 entrará en producción de riesgo ya en 2021 y en producción en masa para el 2S de 2022. Si esto lo comparamos con sus rivales directos, tendremos que Intel llegará con sus 7 nm+ para dicho año y se espera que Samsung haga acto de presencia con sus 3 nm GAE, muy parecidos a este N3 pero con peor densidad. De momento Samsung ya tiene sus 8 nm en el mercado.

| Improvement | 5 nm ‘N5’ over 7nm ‘N7’ | 5nm ‘N5P’ over N5 | 5nm ‘N4″ over N5 | 3nm ‘N3’ over 5nm ‘N5’ |

| Power at Same Performance | 30% | 10% | ? | 25-30% |

| Performance at Same Power | 15% | 5% | ? | 10-15% |

| Density Improvement | 1.8X | ? | ? | 1.7X |

| Risk / High Volume Manfacturing | In HVM | Ramp in 2021 | Risk 4Q21 / HVM 2022 | Risk 2021 / HVM 2H22 |

Así que de nuevo TSMC llegará entre 1 y 2 años antes que sus rivales, mucho tiempo si tenemos en cuenta como acelera la industria actualmente y donde posiblemente hasta 2025 sus competidores no puedan ponerse más o menos a la altura.