Aunque lo supimos a finales del año pasado a través de una filtración, el uso de memoria HBM en la siguiente generación de los Intel Xeon cogió a todos por sorpresa. Meses después de esa «filtración» desde Intel ya han confirmado que la siguiente generación de los Xeon Scalable Processors, conocida como Sapphire Rapids, tendrá modelos que equiparan memoria HBM como RAM.

El mercado de la inteligencia artificial está siendo ocupado por las marcas creadoras de aceleradores, como es el caso de las GPUs de NVIDIA. Intel quiere que el mercado de los servidores para IA no dependa de tener que comprar un acelerador externo con sus próximos Xeon, aunque para ello tengan que añadir memoria HBM.

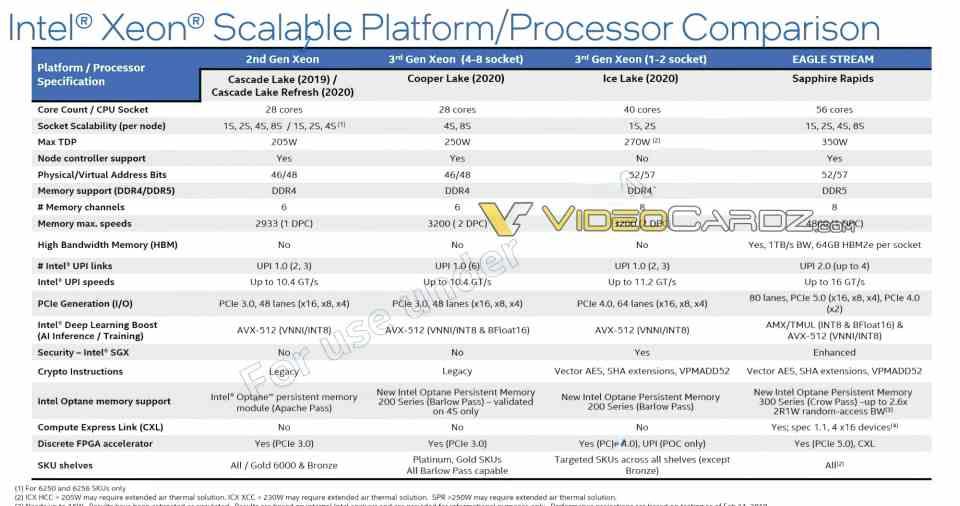

Especificaciones de los siguientes Intel Xeon

Intel ha publicado una tabla donde podemos ver las especificaciones de sus Xeon que saldrán después de los recién lanzados Ice Lake-SP, los cuales reciben el nombre Sapphire Rapids, pero han pasado a ser referenciados como EAGLE STREAM en vez de Xeon por la propia Intel.

Sus especificaciones como se puede ver en la tabla son las siguientes:

- La cantidad de núcleos por CPU pasará de los 40 de los actuales Xeon hasta los 56 núcleos del tipo Golden Cove, los mismos que se van a utilizar en los Alder Lake para CPUs para CPUs de portátiles y PCs de escritorio a finales de este año.

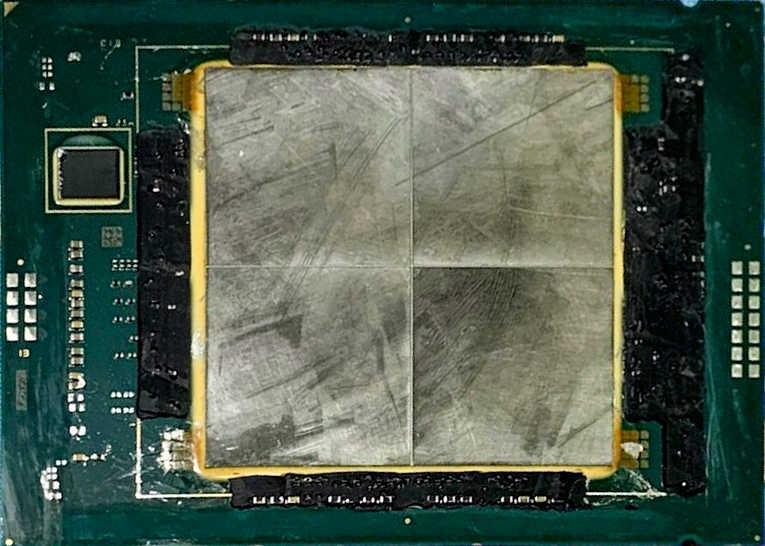

- Al contrario que los actuales Xeon, Intel adoptará por primera vez un diseño basado en chiplets. El cual estará compuesto por 4 procesadores simétricos de 14 núcleos cada uno.

- Configuraciones de 2, 4 y 8 sockets de procesador, por otro lado el TDP ha aumentado de los 270 W a los 350 W.

- La memoria RAM no será DDR4 sino DDR5 con 8 canales de memoria. El máximo de velocidad soportada será la DDR5-4800.

- 80 líneas PCI Express 5.0, frente a las 64 líneas PCI Express 4.0 de los actuales Xeon, además con soporte CXL.

- UPI 2.0, el Ultraprocessor Interconnect ahora usa 4 líneas y su velocidad ha aumentado a las 16 GT/s.

- Mejoras de cara al Deep Learning, con el añadido de las unidades AMX,

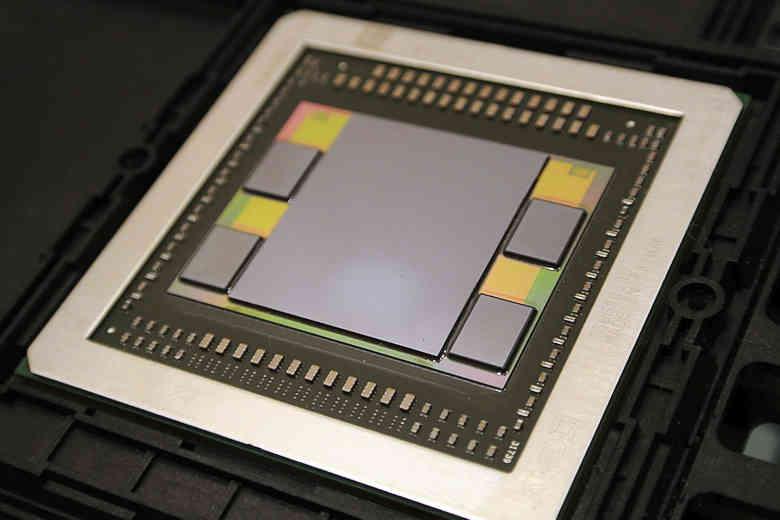

Pero lo que realmente destaca es la capacidad de utilizar memoria HBM, en concreto cada CPU tiene una interfaz de 4096 bits HBM2, con la que se puede conectar a 4 pilas HBM2e con una capacidad total de 64 GB y un ancho de banda de 1 TB/s, lo que resulta en un ancho de banda monstruoso para lo que es una CPU.

¿Para qué necesita un Intel Xeon memoria HBM?

Hace unos meses cuando os comentamos sobre el soporte de memoria HBM, concretamente HBM2E, en los Xeon de siguiente generación os comentamos el hecho que una pila de memoria HBM soporta hasta 8 canales de memoria, por lo que de la misma manera que podemos conectar la CPU a 8 canales DDR4 o DDR5 lo podemos hacer a 8 canales de memoria HBM.

Lo que no esperábamos era una configuración que hiciese uso de una interfaz de 4096 bits HBM, lo que se traduce en un impresionante ancho de banda de 1 TB/s, Lo cual es una exageración para lo que es una CPU, ¿La explicación? El añadido de las unidades Intel AMX, el cual es un array sistólico similar a los utilizados en los Tensor Cores de las GPUs de NVIDIA y las TPU de Google. Todos estos núcleos requieren grandes cantidades de ancho de banda para funcionar.

Esto significa que Intel dejará de utilizar las ineficientes, en consumo y arquitectura, unidades AVX-512 para apostar por un tipo de hardware ya probado de cara a todo lo que rodea a la inteligencia artificial en sus Xeon de siguiente generación. No sabemos si lo incluiría en los Alder Lake, dado el ancho de banda que requieren los algoritmos para IA.