Por lo visto Intel se olvidó de eliminar las instrucciones AVX-512 de sus CPU de escritorio y ahora tiene planes para suprimirlas por completo. Y no, no estamos hablando de un simple bloqueo, sino más bien que no se encuentren en ninguno de sus núcleos de las gamas Core 12 en adelante. ¿Cómo pretenden hacerlo?

Dicen los rumores de que Intel no tenía planeado el lanzamiento de los Xeon Sapphire Rapids para estaciones de trabajo y que eso fue una idea de última hora. El objetivo era que los Intel Core 12 de alta gama fueran los orientados a las mismas, pero al final los de Pat Gelsinger decidieron hacer marcha atrás. ¿El problema? El AVX-512 a eliminar ya se encontraba en los núcleos Golden Cove y no había tiempo para cambios.

Intel va a eliminar por completo el AVX-512 en sus Core 12

El núcleo Golden Cove o P-Core de decimosegunda generación es común en las arquitecturas Alder Lake y Sapphire Rapids, no obstante a Intel no le interesa que una de las capacidades del mismo como es la ejecución de instrucciones AVX-512 quede solamente para sus CPU para estaciones de trabajo o servidores. Técnicamente, tiene sentido utilizar el mismo núcleo para evitar duplicar recursos de manera innecesaria, pero esto significa que ciertas capacidades lleguen a ciertas gamas de CPU que no son del interés de Intel.

No olvidemos que de manera oficial, Intel jamás ha mencionado las instrucciones AVX-512 en relación con sus Intel Core 12. Es más, se necesita desactivar los E-Cores a través de la BIOS para poder activar dichas instrucciones. Una función que se incluyo en las placas base con chipset Z690 y que luego Intel retiró en las placas base de la serie 600 a través de una actualización de la BIOS. Es por ello que no nos debería sorprender el plan de Intel de eliminar el AVX-512 por completo de los núcleos P-Core o Golden Cove.

Es decir, Intel ha desarrollado una versión del núcleo de rendimiento de sus CPU de escritorio más potente del momento que no puede ejecutar instrucciones AVX-512 de ninguna manera. Lo cual hará que la primera remesa de los procesadores con arquitectura Alder Lake-S se revalorice para quienes utilizan aplicaciones optimizadas para las instrucciones SIMD de 512 bits de Intel.

Intel pretende promocionar las instrucciones AMX

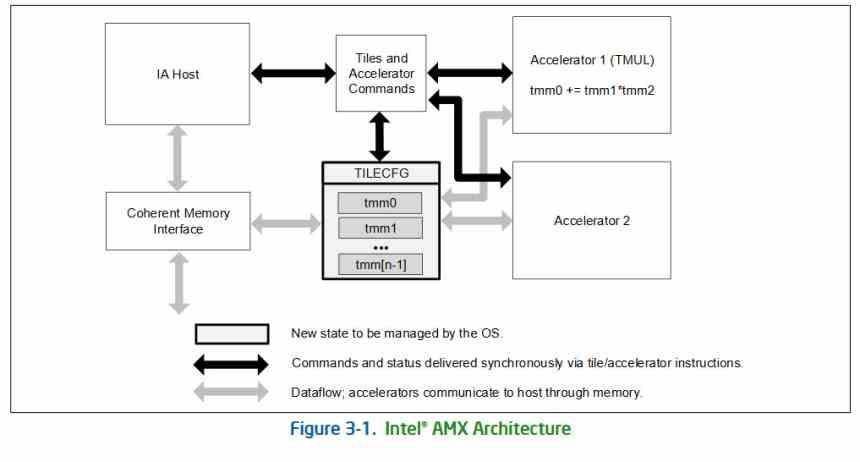

El movimiento de Intel de eliminar las instrucciones AVX-512 responde al hecho de que han añadido sus nuevas instrucciones AMX. Las cuales están optimizadas no para el cálculo vectorial sino matricial que es ampliamente usado en aplicaciones de aprendizaje profundo. Es decir, son el equivalente a las unidades Tensor de las GPU de NVIDIA y las CDNA de AMD, pero en una CPU. Estas nuevas instrucciones por el momento no han sido adoptadas por AMD a nivel de escritorio, aunque si las veteranas AVX-512 a partir de Zen 4. Por lo que está claro que Intel pretende con ello que las nuevas versiones de las aplicaciones se optimicen para el nuevo tipo de unidad e instrucciones que tienen en exclusiva para tener ventaja sobre su rival.

No esperamos que Intel recupere el soporte para sus instrucciones de 512 bits de longitud en Raptor Lake, dada la política que están llevando a cabo de eliminar cualquier reminiscencia de las mismas en sus gamas de escritorio y para portátiles. En todo caso, se trata de una instrucciones polémicas por el hecho que requieren mucha energía para funcionar y son un problema para el paradigma de aumentar el rendimiento respecto al consumo en cada generación.