Uno de los mayores problemas de la informática actual es el conocido como «muro de la memoria«, la diferencia entre el tiempo de procesamiento y el tiempo que se tarda en enviar los datos al procesador desde los chips de la memoria. La creciente popularidad de las aplicaciones de IA solo ha hecho que ese problema sea más pronunciado, porque las enormes redes que encuentran rostros, entienden el habla y recomiendan bienes de consumo rara vez caben en la memoria integrada de un procesador. Ahora, grupos de investigación separados de EEUU y Bélgica creen que un nuevo tipo de DRAM con latencia cero podría ser la solución, y a continuación os explicamos cómo funciona.

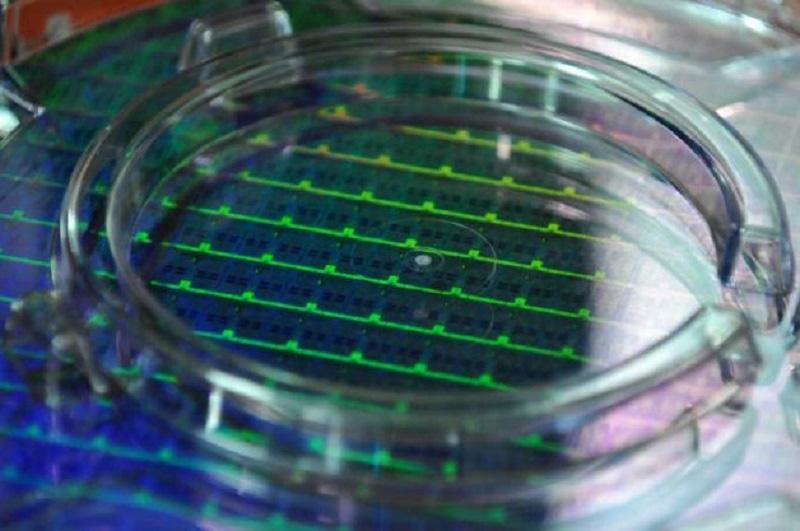

La nueva DRAM, hecha de semiconductores de óxido y construida en capas por encima del die del procesador (es decir, que está integrada) retiene cientos o miles de veces más de bits que la DRAM comercial y podría proporcionar un gran ahorro de área y energía, especialmente el ejecutar grandes redes neuronales.

Cómo funciona la DRAM de latencia cero

Las celdas de memoria DRAM en tu PC están hechas de un solo transistor y un solo condensador cada una en un diseño llamado 1T1C. Para escribir un bit en la celda el transistor se enciende y la carga se empuja hacia (1) o se quita de (0) el condensador. Para leer de él, la carga (si la hay) se retira y se mide; es un sistema muy rápido, barato y que consume poca energía pero tiene algunas desventajas: por un lado, leer el bit agota el condensador por lo que hay que volver a escribirlo en la memoria y, de hecho, incluso si no se lee el bit la carga eventualmente se escapará del condensador a través del transistor.

Por lo tanto, todas las celdas deben actualizarse periódicamente solo para poder mantener los datos, y en los chips modernos esto se hace cada 64 milisegundos.

La incrustación de DRAM en el propio chip del procesador se realiza comercialmente, pero tiene sus límites. El desafío con el diseño monolítico 1T1C siempre ha sido la dificultad de construir el condensador, así como de fabricar un transistor que no tenga fugas utilizando el proceso de fabricación destinado a transistores lógicos. Los buenos condensadores son difíciles de fabricar en los procesos de fabricación creados para circuitos lógicos.

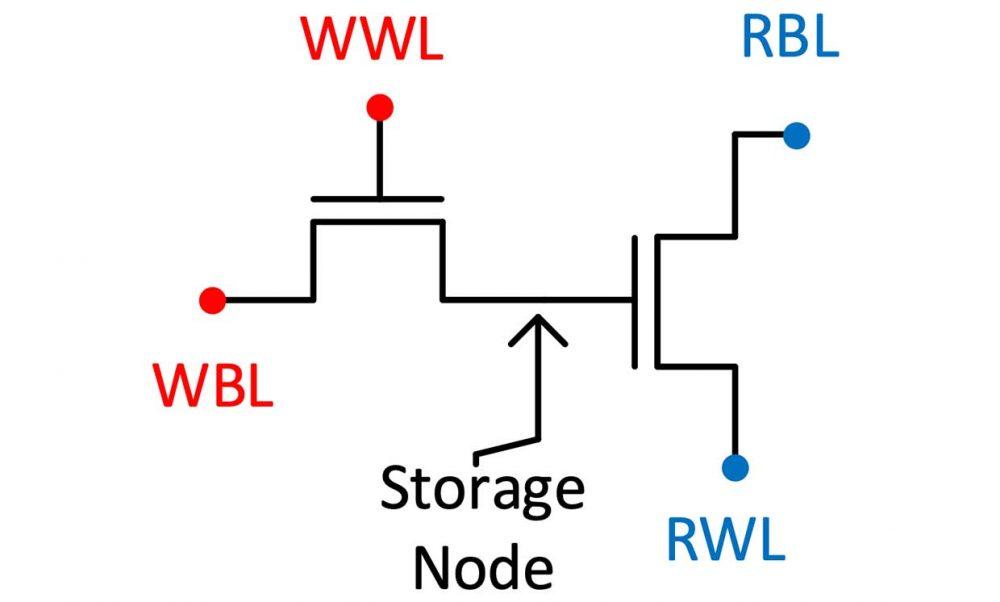

En cambio, la nueva DRAM incorporada está hecha de solo dos transistores y no utiliza condensador (2T0C), y esto funciona porque la puerta de un transistor es un condensador natural, aunque pequeño. Entonces, la carga que representa el bit se puede almacenar ahí, y este diseño tiene algunos beneficios clave, especialmente para la IA.

Una de estas ventajas es que escribir y leer implica hacerlo en dispositivos separados, y por lo tanto se puede leer desde una celda DRAM 2T0C sin destruir los datos y tener que volver a escribirlos. Todo lo que tiene que hacer es ver si la corriente fluye a través del transistor cuya puerta mantiene la carga, y si esta está ahí, encenderá el transistor, la corriente fluye, y si no hay cambios se para.

Esta es una lectura de latencia cero, y es especialmente importante para la IA porque las redes neuronales tienden a leer al menos tres veces por cada escritura. No obstante, una disposición 2T0C no funciona bien con transistores lógicos de silicio, y cualquier bit se drenaría inmediatamente porque la capacitancia de la puerta del transistor es demasiado baja y la fuga a través de los transistores es demasiado alta. Por eso, los investigadores han recurrido a dispositivos fabricados con semiconductores de óxido amorfo, como los que se utilizan para los píxeles de algunas pantallas.

Un nuevo método de fabricación para una nueva DRAM

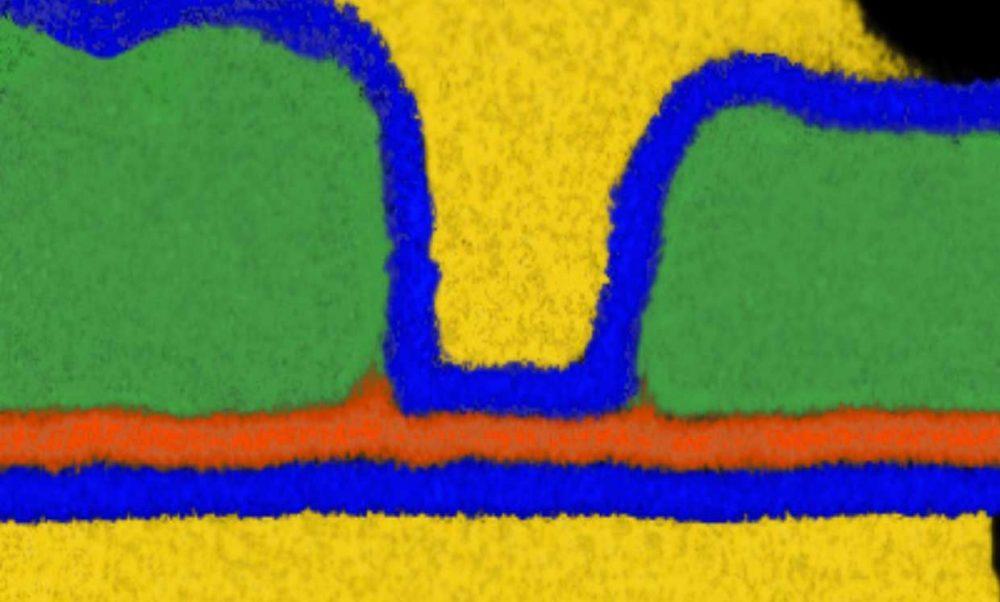

Este tipo de materiales tienen algunas cualidades especialmente útiles para la DRAM. En particular, pueden conducir mucha corriente, lo que hace que la escritura sea más rápida, y cuando están apagados pierden muy poca carga, lo que hace que los bits duren más. El equipo con sede en EEUU utilizó óxido de Indio dopado a aproximadamente un 1% con Tungsteno (IWO) como su semiconductor. Las corrientes en este tipo de dispositivo brindan suficiente velocidad de lectura y escritura suficiente para operaciones lógicas, y al mismo tiempo las corrientes de apagado son realmente pequeñas, del orden de dos o tres veces menos que con Silicio.

En la imagen de arriba podemos ver los transistores en la DRAM sin condensador que ha desarrollado el equipo de EEUU. Incluye un semiconductor de óxido de Indio dopado con Tungsteno (naranja), puertas superior e inferior de Paladio (amarillo), electrodos de drenaje y fuente de Níquel (verde) y dieléctricos de óxido de Hafnio (azul).

Igual de importante es que los óxidos como estos pueden procesarse a temperaturas relativamente bajas. Eso significa que los dispositivos fabricados con estos materiales se pueden construir en capas de interconexiones por encima del silicio de un procesador sin dañar los dispositivos que tienen debajo. La construcción de celdas de memoria en esa posición brinda una ruta directa de gran ancho de banda para los datos que lleguen a los elementos de procesamiento en el silicio, derribando efectivamente la pared de la memoria y con latencia cercana a cero.