SK Hynix acaba de presentar su primer chip fabricado de memoria HBM3 y esperan que Intel, AMD y NVIDIA la adopte para sus futuras arquitecturas gráficas y de CPU para computación de alto rendimiento e inteligencia artificial. ¿Qué tal se presenta el futuro de la High Bandwidth Memory según esta multinacional surcoreana?

La memoria HBM3 aún no tiene el estándar definitivo, pero los diseñadores de diferentes partes del mundo tienen a punto sus propuestas, ya que quien consiga convertir en estándar su propuesta tendrá el beneficio de ser el primer fabricante en alimentar las primeras GPU para computación de alto rendimiento. Por lo que pese a que aún falta un largo tiempo para que las nuevas generaciones de NVIDIA Tesla y AMD Instinct con este tipo de memoria lleguen al mercado el tiempo corre en contra, ya que las interfaces con los nuevos tipos de memoria se han de desarrollar.

En el caso de las memorias de este tipo la complicación aumenta si tenemos en cuenta que tanto la GPU como la memoria se montan sobre un mismo interposer, el cual va a tener unas especificaciones distintas en la HBM3 que en la actual HBM2 y no solo incluye el enrutado entre la memoria y el chip gráfico, sino todo el Power Delivery Network encargado de distribuir la energía entre los diferentes elementos encima del interposer.

Así es la memoria HBM3 según SK Hynix

En la actualidad Corea del Sur es el mayor fabricante de memorias, tanto no volátiles como RAM, del mundo con multinacionales especializadas como Samsung y la que nos ocupa en esta noticia. Y es que SK Hynix ha presentado su prototipo de memoria HBM3 y por tanto su propuesta de cara a ser aceptada por la JEDEC. ¿La ventaja respecto al resto? Pues que al tener su propia fundición ellos pueden fabricar la memoria e ir más allá de un diseño en VHDL o Verilog.

¿Y qué han conseguido? Han fabricado dos pilas distintas, la primera compuesta por 8 chips de memoria y con 16 GB de capacidad en total y la segunda con una pila de 12 y 24 GB de capacidad. Por lo que es la primera vez que vemos superar el límite de los 8 chips por pila en una memoria de este tipo.

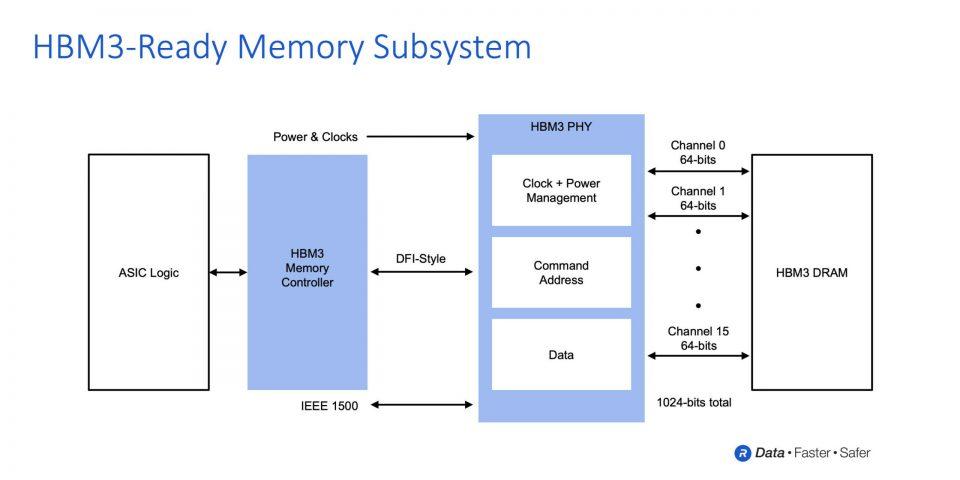

En cuanto al ancho de banda, han llegado hasta los 819 GB/s, hemos de tener en cuenta que el punto en que difiere la memoria HBM3 respecto a sus predecesores es en el uso de canales de memoria de 64 bits por chip en la pila en vez de 128 bits. Esto significa que en una interfaz de 1024 bits podemos colocar hasta 16 chips distintos. Una pila de 12 chips es un bus de 768 bits y un ancho de banda por pin de datos de 8.5 Gbps, aunque cabe la posibilidad de que la velocidad de transferencia de la que habla SK Hynix sea con el bus de 1024 bits.

Si esto fuese así, entonces estaríamos hablando de un ancho de banda real de 409.6 GB/s en el caso del stack de 8 chips y de 614,25 GB/s para el de 12. En ambos casos estaríamos hablando de 6.4 Gbps por pin de datos.

El tamaño del interposer es crucial

La memoria HBM3 parece ser que va a tener chips más altos y más pequeños que las generaciones anteriores del estándar de la High Bandwidth Memory, pero en su prototipo de la HBM3 SK Hynix ha conseguido que la altura de los chips de DRAM se haya reducido un 30% respecto a la generación anterior, tampoco hemos de pasar por alto el uso de nodos de fabricación más avanzados.

El motivo de utilizar canales de memoria de 64 bits y con ello tener chips más pequeños tiene que ver con el hecho de que los interposers son chips monolíticos gigantes sobre los que irán tanto las CPU como las GPU que hagan uso de este tipo de memoria y por tanto el espacio es limitado. Si a esto le sumamos el uso de GPU basadas en chiplets entonces el área se vuelve en un bien preciado. Dicho de otra manera, chips HBM3 más pequeños como los de SK Hynix le dan más área a las CPU y GPU del futuro.