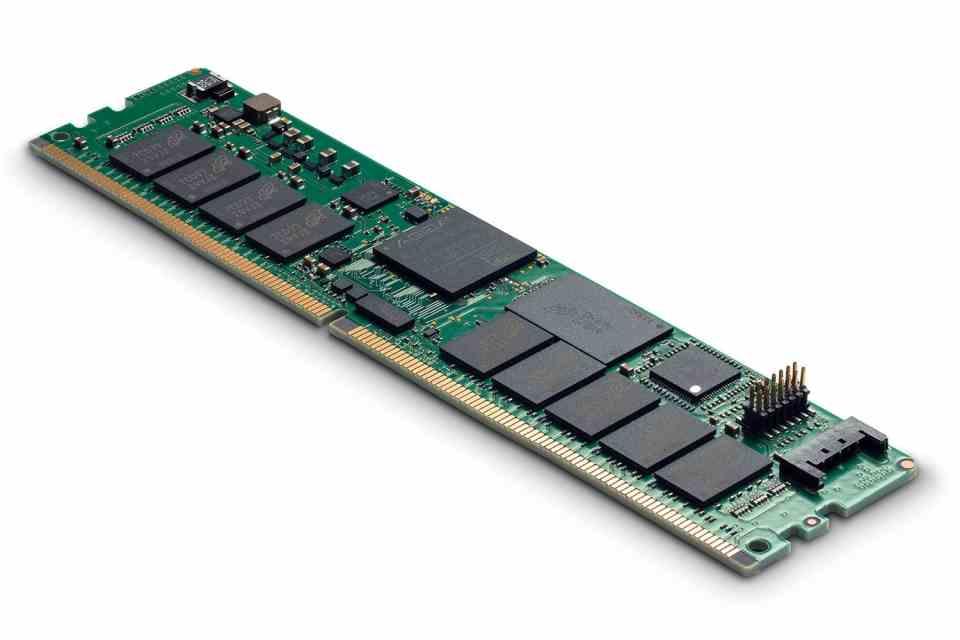

Los módulos de memoria NV-DIMM tienen la particularidad de llevar en su interior RAM no volátil o NAND Flash, entre ellos destaca la NVDIMM-P, la cual se basa en colocar memoria RAM y NAND Flash en un solo módulo DIMM, compartiendo con ello el bus de memoria. Pues bien, AMD adoptará la memoria NVDIMM-P en futuras CPU y APU. Os explicamos cómo la implementarán en su hardware.

Una de las futuras mejoras que vamos a ver tanto en CPU, GPU y en APU es la integración del controlador flash dentro del procesador como ya pasó en su día con el controlador de memoria RAM. Esto en combinación con la interfaz Compute Express Link o CXL, una variante del PCI Express 5.0 en adelante, hará posible la comunicación conjunta tanto con la memoria NAND Flash como de la RAM del sistema. Por lo que en el futuro vamos a tener módulos de memoria que van a integrar la memoria y el almacenamiento en un solo módulo.

Se sabe que tendremos módulos NVDIMM que combinan la memoria DDR5 con memoria NAND FLASH en un solo módulo DIMM. La comunicación con el procesador se podría realizar a través de una interfaz PCIe 5.0. No olvidemos que hace poco Samsung presentó una expansión de memoria DDR5 para un puerto PCIe con interfaz CXL. ¿Es posible que los módulos DDR desaparezcan a favor de interfaces PCIe? Pues AMD ha pensado en esa posibilidad de cara al futuro.

AMD implementará interfaces NVDIMM-P en sus futuros procesadores

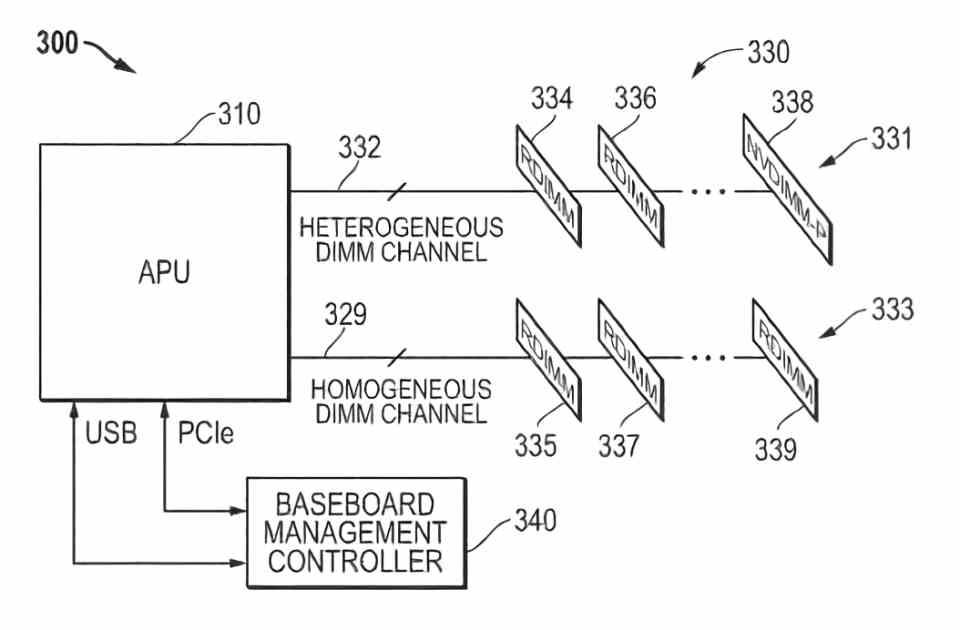

La fuente de esta noticia no es más que la propia AMD, en concreto una patente titulada ERROR REPORTING FOR NON-VOLATILE MEMORY MODULES donde se habla de la implementación de una interfaz de memoria NVDIMM-P para el procesador y de todos los cambios que se han de realizar para ello.

En la descripción de dicha patente podemos leer lo siguiente:

Los sistemas de computación habitualmente utilizan chips de memoria de acceso aleatorio de alta densidad (DRAM) como memoria principal. Muchos de los chips de DRAM que se venden hoy en día son compatibles con varios de los estándares DDR que se promulgan por el Joint Electron Devices Engineering Council (JEDEC). Los controladores de memoria DDR se utilizan para manejar la interfaz entre los diferentes agentes (que acceden a estas memorias) y las DDR DRAM de acuerdo con los estándares DDR publicados.

Una non-volatile dual-inline memory module with persistent storage (“NVDIMM-P”) es un tipo de memoria de almacenamiento que se utiliza en vez de los DIMM DDR estándar, pero que incluye memoria persistente. Sin embargo, estas memorias contienen diferentes tipos de condiciones de error que difieren de las condiciones de error de la DDR. Además, las condiciones de error asociadas con la NVDIMM-P tienen diferentes efectos de error en el sistema operativo que ejecuta procesos que utilizan la memoria que las condiciones de efecto de error asociadas con los DIMM DDR.

La patente nos confirma por tanto que AMD ha desarrollado una forma de utilizar este tipo de módulos de memoria en sus futuros procesadores. Por el momento no sabemos en qué generación lo estrenarán. Pero si utilizamos la lógica está claro que un futuro AMD EPYC 7004 basado en la arquitectura Zen 4 podría ser un buen candidato para el uso de este tipo de memorias.