La futura reducción de los nanómetros pinta oscura para NVIDIA, Intel y AMD

Las grandes fundiciones del planeta están a pleno rendimiento, donde Samsung, TSMC e Intel están ultimando sus procesos litográficos de nueva generación para sus principales clientes, con AMD y NVIDIA en mitad de todo el entramado como gigantes del sector. Los 5 nm en TSMC y Samsung parecen alcanzables, al igual que los 7 nm de Intel, pero ¿qué hay de procesos con menor litografía? Según los expertos el futuro pinta oscuro, al menos de momento.

En la SPIE Advanced Lithography 2019 no son demasiado optimistas

Entre el 24 y 28 de febrero se ha desarrollado el mayor evento de litografía del mundo, donde los mejores expertos en este increíble mundo se han reunido para aprender y compartir los últimos desarrollos en áreas importantes y clave de los procesos litográficos.

La preocupación es global donde parece que EUVL es una leve esperanza, que puede y debe ser un foco de mejoría hasta incluso los 5 nm en fundiciones como TSMC, pero según parece la hoja de ruta para los años venideros podría extenderse hasta en una década como poco, al menos para llegar a 1 nm.

Para entrar en situación, actualmente Samsung ya ha comenzado la producción de dispositivos con EUV a 7 nm, TSMC espera incrementar la producción de sus 7 nm y comenzar en breve con sus 7 nm+ con EUV, aproximadamente en junio, mientras que Intel está en pleno bullicio para lanzar los primeros procesadores a 10 nm de alto rendimiento.

En cambio, GlobalFoundries ni está ni se la espera, sobre todo después de los rumores de venta (o compra, según se mire) por algunos de los gigantes actuales, donde se habla de Samsung como posible destino de la compañía.

En cualquier caso y según los pitch filtrados, parece que Intel seguirá teniendo algo de ventaja en su proceso litográfico debido a su mayor densidad inicial.

Todos los procesos actuales en desarrollo o producción/preproducción han incluido un retraso considerable, del cual ninguna de las tres empresas se libra.

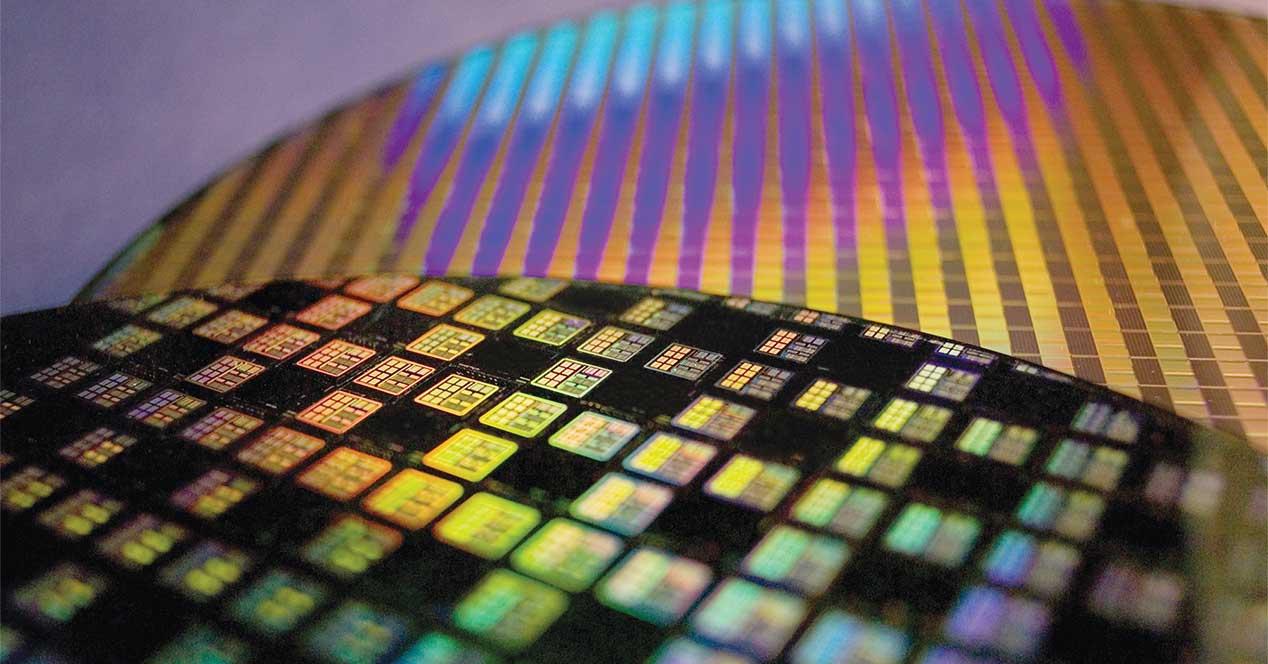

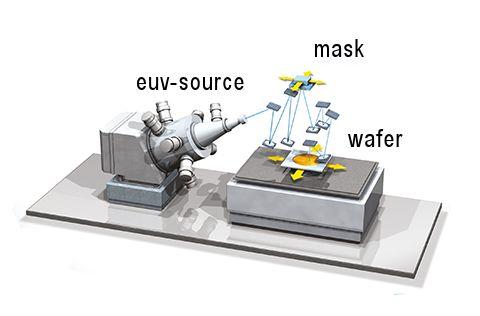

Esto en parte es debido a la ausencia de tecnología que permitiera una longitud de onda de menor tamaño, para así poder grabar las obleas con precisión y tasa de éxito suficientes como para hacer el proceso rentable para la empresa.

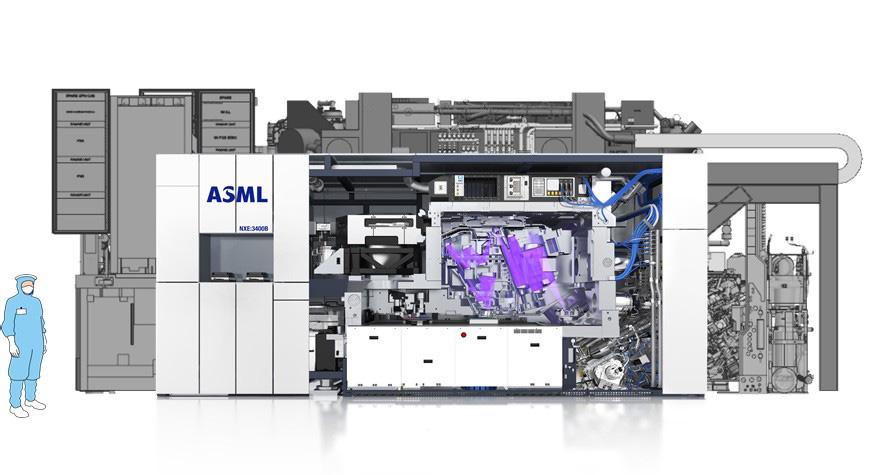

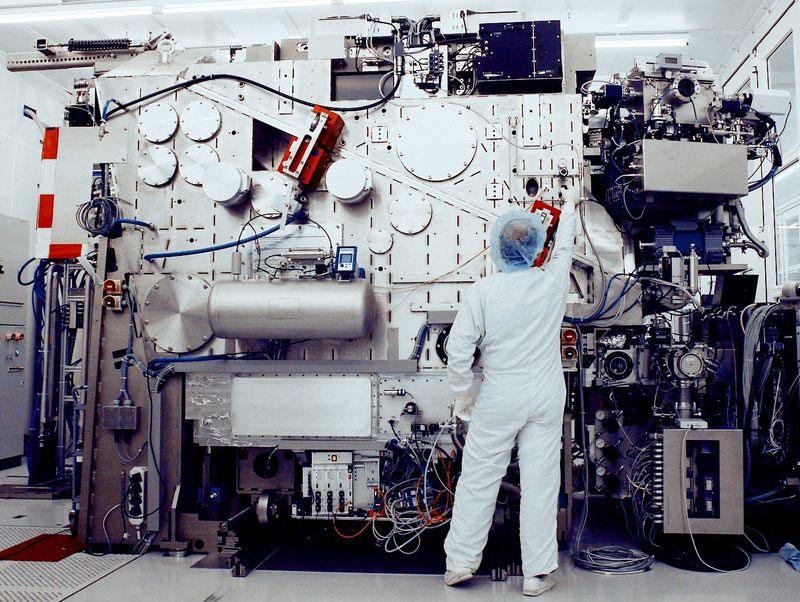

ASML lidera los procesos litográficos gracias a sus equipos de grabado

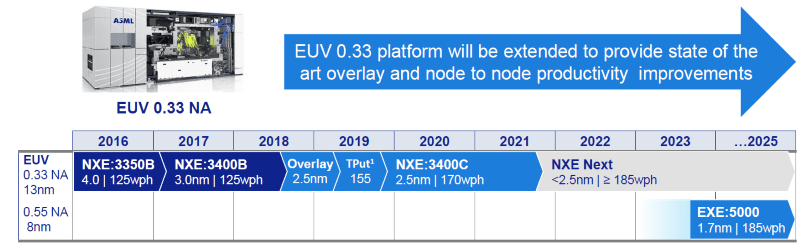

Lo cierto es que ASML es el principal proveedor de maquinaria para grabado de obleas del mundo, donde actualmente pretende servir tanto a Samsung como a TSMC con una actualización de su equipo estrella, el NXE 3400C, el cual promete un rendimiento de 170 obleas por hora con un 90% de efectividad y disponibilidad.

El problema, tal y como muestra el roadmap de ASML, es que seguir reduciendo la longitud de onda de los 13.5 nm que proporcionará EUV y más tarde EUVL va a llevar muchos años, donde podríamos encontrarnos con un escenario parecido a lo vivido actualmente con los 14 nm de Intel.

Para explicar esto hay que entrar en términos más técnicos y en jerga de ingenieros, ya que hay varios procesos importantes a la hora de grabar un chip en una oblea con éxito, pero sobre todo a un menor proceso litográfico.

Fluctuación estocástica y resistencia

Todo se basa en dos parámetros, la fluctuación estocástica y la resistencia. En el primer caso todo se debe al número de fotones que se exponen en un disparo de EUV, ya que los llamados contactos presentan dos posibles fallas desde el punto de vista del apilamiento de matrices y capas en 3D: un puente o la apertura/cierre de estos.

Para explicar esto de forma simple tenemos que imaginar un die fabricado en varias capas a través de un proceso de grabado por luz ultravioleta. Como sabemos, dicho grabado se produce en un número de capas actualmente inviable para seguir por dicho camino sin la utilización de EUV.

Entendiendo esto, un puente es un fallo en el diseño de grabado que se produce cuando dos de esas capas llegan a tocarse o romperse (verticalmente hablando claro).

El hecho de la apertura o cierre de los contactos es un problema de las llamadas «Gate«.

Un chip actual tiene cientos de millones de contactos en su interior grabados a un tamaño de onda concreto. La modificación de ese tamaño de onda permite grabar más contactos por mm2, pero genera más problemas con las Gate, donde pueden fallar quedándose abiertas o cerradas permanentemente.

Cuanto menor tamaño de onda se consigue menor fluctuación estocástica de fotones tendrá el proceso de grabado, y por lo tanto será una grabación más perfecta, más pura, pero al mismo tiempo se genera mayor resistencia a los cambios de estado de las «Gates», debido principalmente a que las moléculas del silicio reaccionan de manera diferente a esos fotones.

En breve, uno de cada mil millones de contactos físicos puede ser malo

Debido a todo lo anterior ya muchos ingenieros como Rob Aitken, ingeniero de ARM, afirman que el número de contactos físicos se irá incrementando conforme se avance, a no ser que los métodos cambien.

Para Aitken el apilamiento de estructuras 3D es el futuro más cercano, ya que la técnica requiere, eso sí, de una nueva microarquitectura.

El motivo es simple, la capacidad de diseño de chips en 3D es actualmente enorme y requiere un nuevo paradigma.

Justamente hablamos de esto hace poco tiempo, en concreto con el nuevo escenario que Intel presentó con Foveros, donde apuesta de forma clara por el apilamiento 3D para salvar, al menos de momento, los problemas derivados del número de matrices y patrones que se usarán a partir de los 5 nm y con vistas a los 3 nm.

El último escollo al que nos enfrentaremos será el propio proceso litográfico en sí, ya que la escalada litográfica tendrá un fin, tal y como llevamos hablando algún tiempo.

Cuando las características del proceso litográfico sean menores que el diámetro de un átomo de silicio, habremos llegado al final del camino, al límite físico que un chip puede ofrecer.

Solo dos posibles salidas ante este problema

Solo existen dos posibles salidas ante el problema que se nos avecina en poco más de una década: cambiar de paradigma y con ello un cambio en el sector, donde el mundo cuántico puede que comience a despegar cuando la industria invierta todo el capital en ello.

O en cambio, encontrar un método que salve el problema de fluctuación estocástica mediante EUVL.

Esto es tremendamente complicado a día de hoy, ya que, por ejemplo, para poder saltar de 14 nm a 7 nm TSMC necesitó un aumento de ocho veces en el tiempo de escritura, donde para colmo la tasa de éxito era baja hasta hace poco.

Cada salto litográfico agrega mayor complejidad al grabado, mayor número de pasadas, mayor tiempo, mayor exposición, mayores contactos a misma superficie y mayor porcentaje de contacto entre matrices.

EUV es una solución paliativa que ha salvado un obstáculo frente al grabado tradicional que Intel usará en sus 10 nm, pero es de esperar que al llegar a los 5 nm suframos de nuevo para seguir reduciendo el tamaño de los transistores.

Si no encontramos una solución en poco más de una década el fin de la evolución litográfica parece inexorable, y con ello la innovación y desarrollo de nuevas tecnologías con más potencia y menor consumo, ya que como hemos dicho, el apilamiento 3D es una solución paliativa para salvar ciertas deficiencias en el grabado y su rentabilidad por oblea.

¿ASML al rescate de la litografía?

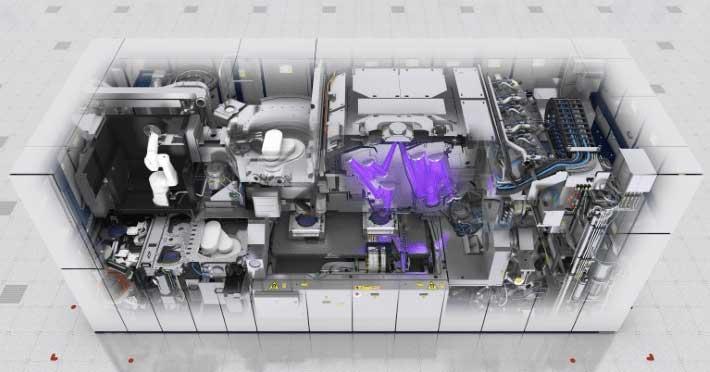

Lo cierto es que desde ASML no son tan negativos ante estos problemas, ya que tienen toda su artillería, ingenieros y capital en la fabricación de una nueva serie de TWINSCAN de nueva generación a los que han denominado EXE:5000.

Dichos equipos van, por lo pronto, con dos años de retraso. En ellos ASML ha introducido de momento varias mejoras, desde una expansión de la capacidad de metrología con su nueva óptica ASML YieldStar y un nuevo y revolucionario haz de electrones múltiples llamado ASML-HMI.

Con ello lo que intentan es aumentar el potencial de la litografía EUV de alta NA (apertura numérica o Numerical aperture).

Actualmente los sistemas EUV de Samsung y TSMC ofrecen 0.33 NA, pero con las medidas anteriormente comentadas ASML espera proyectar un mayor NA en las obleas mediante mayores ángulos, mejorando la resolución y permitiendo la impresión de chips con transistores de menor tamaño.

Según ASML, el nuevo EXE:5000 podría contener un NA de 0.55, aunque según la compañía la tecnología de foto-protección necesitará mejoras adicionales para reducir la defectividad.

De conseguirlo, ASML solventaría el problema hasta su misma base, pero seguiríamos con el mismo paradigma: ¿qué hacer cuando los procesos litográficos sean menores al diámetro de un átomo de silicio?

De momento nadie tiene la respuesta, donde por otro lado es más que probable que tengamos casi dos décadas para investigar y ofrecer una solución real que nos permita seguir avanzando.