Siempre hablamos de los nuevos procesos litográficos y de sus mejoras, aquellas que llevan al hardware al siguiente nivel. Pero no solemos hablar de los problemas que tienen que enfrentar compañías como TSMC o la propia Intel para seguir avanzando e innovando. Ahora que los taiwaneses han alcanzado la producción en masa de sus 5 nm y están a punto de comenzar con los 3 nm, es buen momento para entender los principales obstáculos que han enfrentado.

Un chip determinado tiene que enfrentar una serie de problemas cuando se le introduce en un producto de alto rendimiento. Desde el calor a las vibraciones variadas, pasando por las frecuencias que alcanza, todo se vuelve más y más complejo de trabajar precisamente porque el reducir los transistores y aumentar la densidad del nodo requiere inspeccionar, medir y probar cada chip de una forma más compleja, es decir, cada salto litográfico añade ciertos problemas.

Los 5 nm como sucesor de los 7 nm representan solo algunos cambios importantes

El principal de ellos es que la propia aleta del transistor debe ser más fuerte físicamente hablando. Reducir el tamaño de cada fin y gate requiere una serie de capas mayores en lo vertical si se mantienen los típicos transistores FinFET.

Los fins y las gates se alargan, se hacen más altas, por lo que la cantidad de materiales y su depósito de los mismos es crucial para mantener el flujo de corriente uniforme en las tres paredes de dicha puerta. Podríamos pensar que aumentando la altura se consigue pasar un mayor flujo vertical de corriente en cada transistor, pero lo cierto es que la proporción de anchura y altura es la clave para el aumento de rendimiento del mismo, ya que las proporciones no son equivalentes al rendimiento.

Esto incurre en un problema de control en las fab para asegurar que el proceso de grabado de los transistores es el correcto. Para intentar evitarlo se está recurriendo a la inteligencia artificial mediante aprendizaje automático para detectar ciertos problemas antes de que la oblea haya finalizado ciertos procesos vitales, de manera que con antelación se sepa si es una oblea predispuesta al fallo.

El segundo problema que enfrentan los 5 nm es curioso, ya que es el exceso de datos de la propia oblea y chip. Aquí de nuevo el Deep Learning toma la delantera, ya que es capaz de determinar mediante imágenes de visión artificial y con ciertos algoritmos los problemas y los puntos de interés donde los ingenieros deben centrarse para mejorar el proceso de fabricación del nodo.

Este hecho ha provocado un acortamiento de los plazos de entrega efectivos de este proceso litográfico de 5 nm, ya que gracias al aprendizaje profundo TSMC pudo ver y anticipar donde estaban los problemas más graves sin tener que perder ingentes cantidades de horas a base de pruebas y errores en grabado de las obleas.

Los 3 nm podrían ser el cambio de paradigma para la nueva generación de nodos

Si los 5 nm han obligado a alargar los transistores de manera vertical para poder agruparlos horizontalmente en mayor cantidad y con ello aumentar la densidad del nodo, los 3 nm van a representar cambios más importantes.

Aunque no está confirmado por parte de TSMC, NVIDIA y AMD pueden tener que rediseñar sus arquitecturas para los grabados, puesto que es más que probable que los taiwaneses opten por el camino de Samsung y reemplacen los transistores FinFET por GAA o Gate-all-around.

La intención preventiva no es esta, ya que eso implicaría un cambio drástico, comenzando por las máscaras en blanco y terminando por un nuevo tipo de grabado y lentes. Además, de lo poco que se sabe es que aunque TSMC consiguiese mantener los FinFET una generación más, los nuevos transistores van a requerir nuevos materiales en las obleas, tales como el cobalto o rutenio.

Por si fuese poco, las películas y capas deberán ser más delgadas para favorecer el traspaso eléctrico de la corriente, pero esto implica que serán más difíciles de limpiar, pulir, medir y por supuesto inspeccionar. Por si fuese poco y dándose otro paradigma curioso, una lógica digital de un chip a menor tamaño en sus transistores estos adquieren un comportamiento más análogo.

Nuevos materiales y funcionalidad de cada transistor

Si esto lo sumamos a los nuevos materiales que definirán los fins y las gates, volveremos a encontrar algunos de los problemas de antaño, pero multiplicados en cuanto a dificultad de solventarlos. Fugas de energía, debilidades estructurales, tensiones no medidas y por supuesto una mayor inductancia serán algunos de los problemas que están enfrentando todas las empresas de la industria, no solo TSMC como fabricante de las obleas.

El dato clave va a estar en la funcionalidad de cada transistor. Antiguamente cuando un transistor moría dejaba de funcionar, mismo caso si estaba dañado. Actualmente esto no pasa debido a la fabricación y diseño de los mismos: seguirá funcionando, pero con un menor rendimiento lo cual de expandirse reduce el conjunto de los mismos a un nivel inferior.

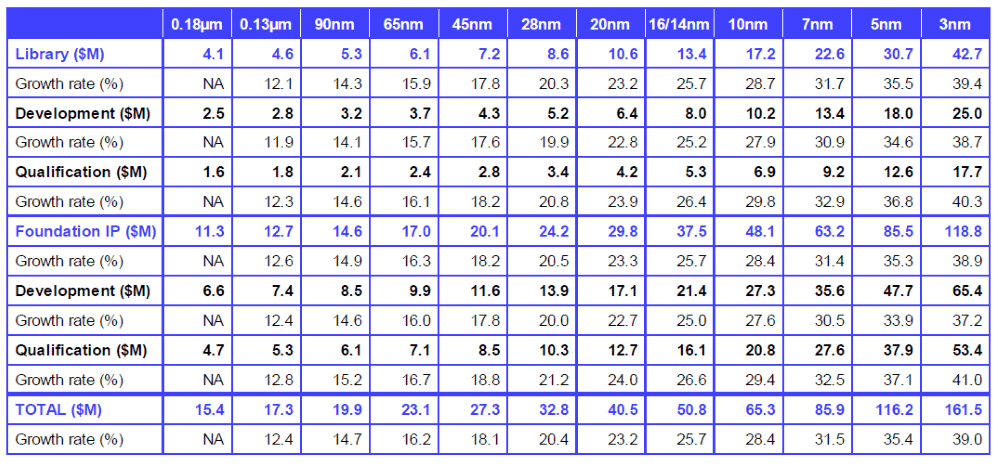

Por ello, la funcionalidad perfecta de los transistores es clave en la industria y supone miles de millones de dólares en investigación, prevención y detección de errores, algo que en los 3 nm va a ser clave si se quiere aumentar el rendimiento de cada chip. Es curioso cómo está virando la industria. La dificultad de un nodo no es tanto conseguir obleas funcionales, sino asegurarse que dichas obleas obtienen la tasa de rendimiento y fiabilidad que se pretenden y para las que fueron diseñadas, ahí está actualmente el reto, porque de nada sirve una oblea con mucha densidad por chip si el rendimiento final de estos está por debajo de su antecesor.

El siguiente reto será el átomo como tal y a partir de ahí se abre un campo increíble donde el silicio quizás solo sea la base de una serie de compuestos moleculares que permitan reducir su tamaño por debajo el átomo, algo realmente increíble.

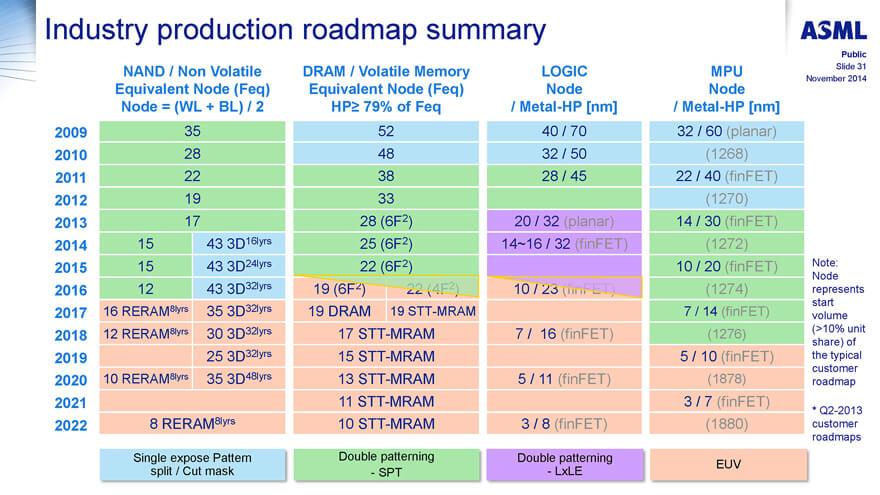

Una carrera suicida en la que es posible que solo queden 1 o 2 fabricantes

Con cada nuevo nodo de fabricación la cantidad de empresas capaces de fabricar el nuevo nodo ha ido disminuyendo, hasta que al final las únicas empresas que hay en el mercado capaces de fabricar los nodos más avanzados se pueden contar con los dedos de una mano. Con el salto a los 7 nm fue Global Foundries la que salto de la carrera de los nanómetros. ¿Cual será la próxima gran fábrica de procesadores que no podrá seguir el ritmo?

TSMC no parece que vaya a tener problemas para llegar a los 3 nm si continua con el mismo ritmo que hasta ahora, es más, todo apunta que será una de las supervivientes que llegarán a dicho nodo.