El mercado apunta a los chiplets, o al menos eso parece. AMD lleva ya algunos años con su disposición basada en MCM e Intel tiene a punto el siguiente paso con tecnologías como Foveros, pero ¿esto es un movimiento que es obligado? ya sabemos sus ventajas, ¿y sus inconvenientes? Hoy veremos lo bueno y lo malo de los chiplets y por qué la industria no ve tan clara esta forma de crear CPUs.

Todos los grandes entre los que se incluyen AMD, Intel, TSMC y Marvell, están trabajando en diferentes enfoques para el mundo de los chiplets, diferentes alternativas que intentan desarrollar diseños más avanzados. Aunque en artículos anteriores tratamos este tema en concreto, hay ciertos puntos que dejamos para esta ocasión, ya que la industria no está tan segura de que los chiplets sean el camino a seguir.

Falta de ecosistema, estándares, tiempo y costes de desarrollo

No es oro todo lo que reluce y si bien AMD es de las pocas que están lanzando productos reales al mercado basados en chiplets, no está siendo precisamente fácil hacerlo. El problema es que no hay un ecosistema, no hay estándares fijos que la industria pueda seguir para con ello reducir los tiempos de creación y costes de desarrollo.

Cada compañía está enfrentando, más o menos, sus problemas de forma individual, unitaria, pero ninguna de ellas por separado tiene todas las piezas para formar el puzzle. En cambio y de forma bastante curiosa, todas enfrentan casi los mismos problemas:

- Intentan ofrecer chiplets óptimos y con conexiones cada vez mejores y más rápidas que puedan escalar a diferentes productos.

- Necesitan tecnologías de terceros en mayor o menor medida.

- Falta de soporte en los diseños de los esquemas de interconexión entre dies.

- Necesitan IPs correctas con capacidad de fabricación.

Esto está provocando que, por ejemplo, Intel siga su camino basado en monodie para sus CPUs, algo que veremos durante bastantes años. AMD ha sido pionera, pero está pagando amplios costes porque depende de terceros y estos a su vez de empresas especializadas para ciertas técnicas que tienen que desarrollarse en exclusiva, aumentando los costos generales.

Para unir todas estas piezas se necesitan herramientas EDA, ya que son diferentes arquitecturas y productos, interfaces físicas y lógicas a unir e información clasificada de varias compañías para lanzar un único producto. Además, algunos componentes clave pueden estar no disponibles como tal, lo que agudiza el problema.

La industria tiene que compartir diferentes IP si quiere avanzar con los chiplets

![]()

No hay más ciego que el que no quiere ver. Un dicho que parece no estar gustando a ciertos sectores de la fabricación de IPs para las grandes compañías. La inversión está hecha y el camino tiene que ser el compartir al menos una serie de interfaces estándar para la integración de los chiplets, algo que va a perjudicarles seriamente en lo económico.

El ejemplo a seguir es simple, los SSD NVMe, SATA o mismamente la DRAM. Usan una misma interfaz, de manera que las distintas partes no necesitan conocer los detalles de las otras puesto que saben a que ceñirse y como tiene que ser el diseño de los PCB, las conexiones y los chips.

Ahorran costes, tiempo, optimizan balances financieros, producen mucho más y mejor, pero lo más importante es que todas las empresas compiten en las mismas condiciones fomentando la propia competitividad del sector.

En este aspecto y como no podía ser de otra forma ante tal caos, las grandes empresas están desarrollando la base de estos estándares tan necesarios, tecnologías de interconexión con interfaces abiertas para que las empresas se unan a su causa.

Tanto es así que actualmente la disputa va a estar entre cuatro aspirantes al título: AIB, BoW, OpenHBI y XRS, donde además, el ODSA está desarrollando por su parte el llamado Chiplet Design Exchange o CDX, un formato abierto de intercambio seguro de información que conserve la confidencialidad y que mantenga flujos de trabajo e información para los prototipos.

Con él en mente, se intenta organizar a las distintas interfaces para comenzar a crear un sistema heterogéneo confidencial que logre diseñar poco a poco chiplets de forma más sencilla y en base al estándar que termine imponiéndose. Puede darse el caso de que no hay un solo ganador, ya que la industria necesita innovar al menos en dos sentidos, pero por lo menos sería el primer paso para tener un objetivo común para todos.

La creación de los chips y sus interconexiones también requiere de unificación de criterios

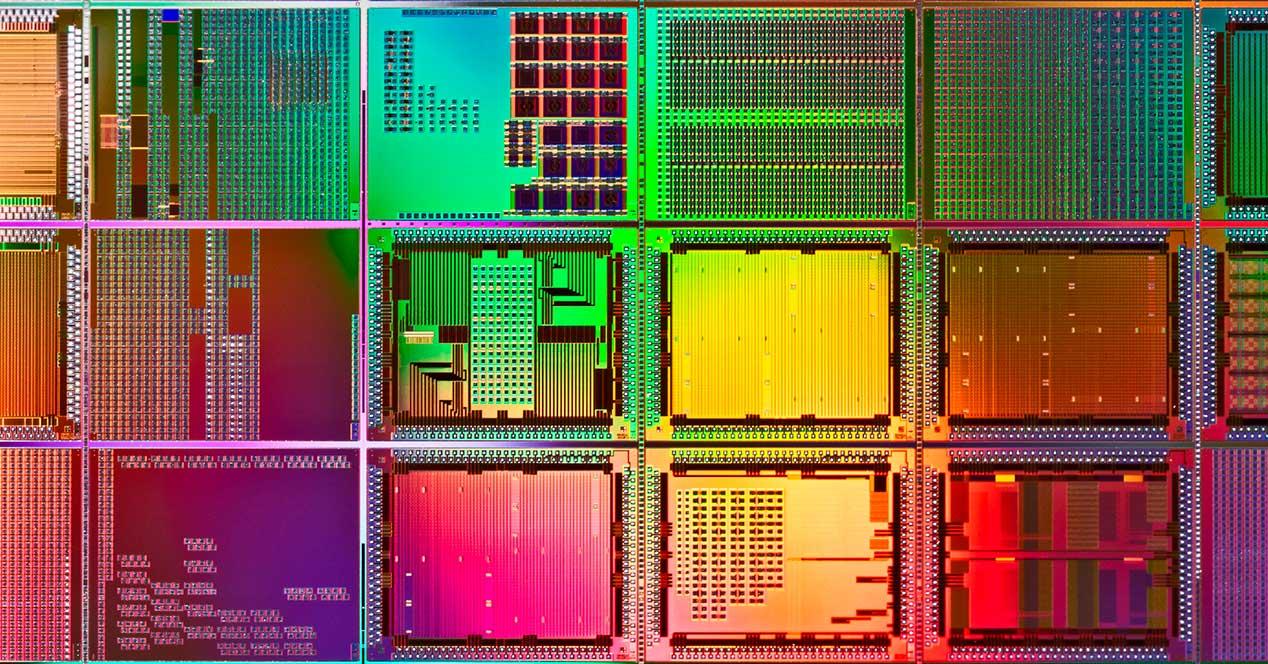

Si el rompecabezas ya era complicado de resolver, hay que tener en cuenta que los diseños de las interconexiones (aka protuberancias o microbumps) tampoco están definidos como estándar. Cada compañía crea sus bumps y sus empaques, por lo que al no haber una estandarización en esto se requieren herramientas específicas para las comprobación, creación y supervisión de las obleas, tanto para los chips como para los interposer.

Los pasos son casi todos automatizados, donde las obleas pasan varias horas de pruebas, testeos y supervisión con contenidos eléctricos, físicos y visuales. Como era de esperar, las interconexiones mediante microbumps son mucho mayores en tamaño físico en los chiplets que en los die monolíticos, donde pueden alcanzar desde los 25 micrómetros hasta los 40 micrómetros.

Para hacernos una idea, y cogiendo una oblea típica de 300 mm, comprobar cada conexión de microbumps es como localizar la cabeza de un alfiler en un campo de fútbol, según asegura la vicepresidenta de FormFactor. La precisión es increíble y esto supone que sin un estándar los costes van a seguir creciendo para todos, ya que las nuevas microbumps se acercan a los 10 micrómetros, y las pruebas no van a parar de subir de precio por la inmensa precisión que necesitan para sus correspondientes pruebas.

Por lo tanto y en resumen, ¿es una ventaja o una desventaja seguir el camino de los chiplets? Está muy bien que veamos el mar desde la orilla y nos impacte cada lanzamiento o tecnología que diseñan tanto Intel como AMD. Pero bajo el agua el sector no lo tiene tan claro y aunque los pasos a seguir se van definiendo, los de Swan por ejemplo no van a dejar las CPU monolíticas de lado hasta que la industria entera pueda tener una serie de estándares a seguir.

AMD va a tener que asumir el peso de todo lo dicho y de la mano de TSMC, donde como ya hemos comentado más de una vez, los precios de sus procesadores tendrán que subir antes o después para seguir siendo rentables y sobre todo, aumentar el margen de beneficios. No va a ser un camino de rosas para ninguno de los dos gigantes, Intel tiene EMIB, Foveros, AIB y Co-EMIB, TSMC en desarrollo con System on Integrated Chip (SoIC) y AMD intenta cuadrar las piezas para sus nuevas arquitecturas en base a varias empresas que suministran lo necesario para estos chiplets.

Si alguno pensaba que esto era coser y cantar, estaba muy equivocado. El futuro no es negro, pero requiere acuerdos a largo plazo y pérdidas que todos tendrán que asumir.