La arquitectura Zen 3, la cual es utilizada por los AMD Ryzen 5000, tanto en escritorio como en algunos procesadores de la gama de portátiles, es en estos momentos la arquitectura de CPU más potente y avanzada del mercado. ¿Pero qué secretos esconde en su interior para alcanzar ese rendimiento?

Independientemente de si estamos hablando de una CPU basada en chiplets o de un procesador monolítico, los cambios que vamos a describir son generales para todos los procesadores de AMD basados en Zen 3.

Los núcleos de la arquitectura AMD Zen 3

Con tal de entender el porqué de los cambios en cuanto a rendimiento respecto en Zen 2 respecto a Zen 3 hemos de entender de antemano que el aumento del 19% en el IPC es producto de colocar ambos procesadores bajo una prueba o varias pruebas de rendimiento y sacar una media de rendimiento de ambas arquitecturas.

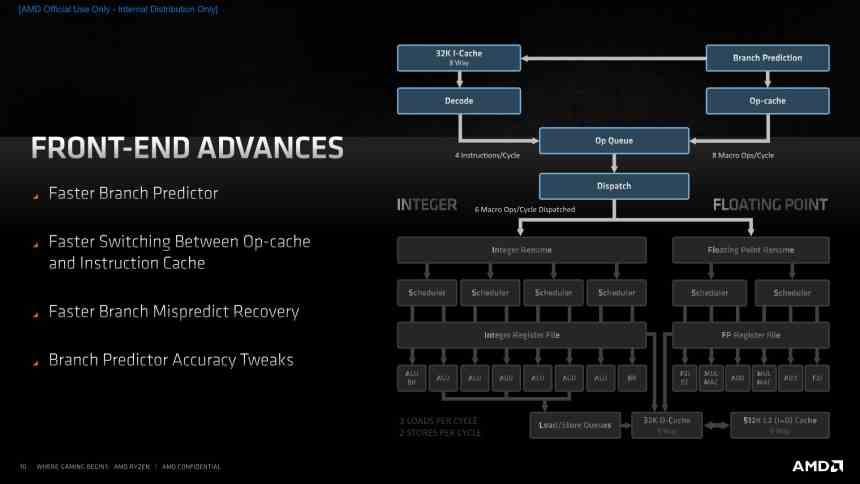

A simple vista Zen 3 puede parecer una versión levemente mejorada de Zen 2, ya que los cambios se encuentran en partes del procesador que suelen ser invisibles a la hora de hablar del rendimiento de un procesador, estos cambios se han hecho especialmente en la unidad de control o Front-end del procesador.

Mejoras en el Front-end de los núcleos Zen 3

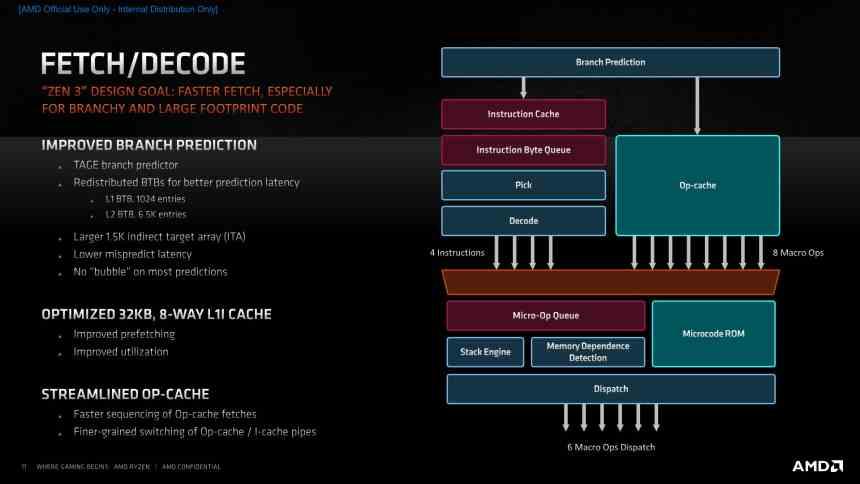

Entre las novedades en el Front-End del procesador, el componente que más destaca es la nueva unidad de predicción de saltos, Branch predictor, la cual ha sido mejorada para que pueda predecir más ramas por ciclo de reloj, para ello se han hecho una serie de cambios en el procesador, como es un rediseño del Branch Prediction Buffer BTB, el cual se sitúa tanto en la caché L1, ya que la cantidad de entradas ha aumentado de las 512 a las 1024, como en la caché L2 ha disminuido de las 7K a las 6.5K entradas respecto a Zen 2.

La nueva unidad de predicción de saltos reduce la cantidad de ciclos perdidos cuando el procesador hace una predicción fallida, evitando así que los núcleos se encuentren mucho más tiempo parados cuando falla la unidad de predicción de saltos.

Por otro lado. no podemos olvidar que los procesadores con arquitectura Zen 3 utilizan el set de registros e instrucciones x86-64, lo que significa que estamos ante una ISA del tipo CISC. Una de las ventajas que tienen los sets de registros e instrucciones CISC es que agrupan varias instrucciones simples en una sola compleja, lo cual ahorra en el espacio del código y la energía a la hora de leer este desde la RAM.

Desgraciadamente tienen la desventaja que son muy difíciles de segmentar de cara a crear un pipeline, es por ello que las instrucciones complejas se han de descodificar en instrucciones internas más simples llamadas uops o micro-operaciones, es decir, es necesario descodificar las instrucciones x86-64 en un tipo de instrucciones más simples con tal de permitir segmentarlas más fácilmente y poder implementar un pipeline.

En los procesadores RISC la cantidad de bytes por instrucción es siempre el mismo, pero en una ISA como la x86-64 los hay de diferentes tamaños, lo que hace sumamente compleja realizar la decodificación de las diferentes instrucciones y en algunas instrucciones en concreto la cantidad de ciclos para decodificar una instrucción es demasiado alto. Es por ello que se hace necesario la implementación de un tipo de cache que permite realizar el trabajo de aceleración más rápido, la llamada uop cache, la cual reduce también la energía consumida durante la etapa de descodificación de las instrucciones.

No sabemos en qué grado ha mejorado AMD la uop cache y la comunicación de la misma, pero es una de las piezas clave de cara a mejorar el rendimiento en procesadores x86-64 y uno de los puntos que AMD menciona que ha mejorado respecto a Zen 2.

Las unidades de ejecución en Zen 3

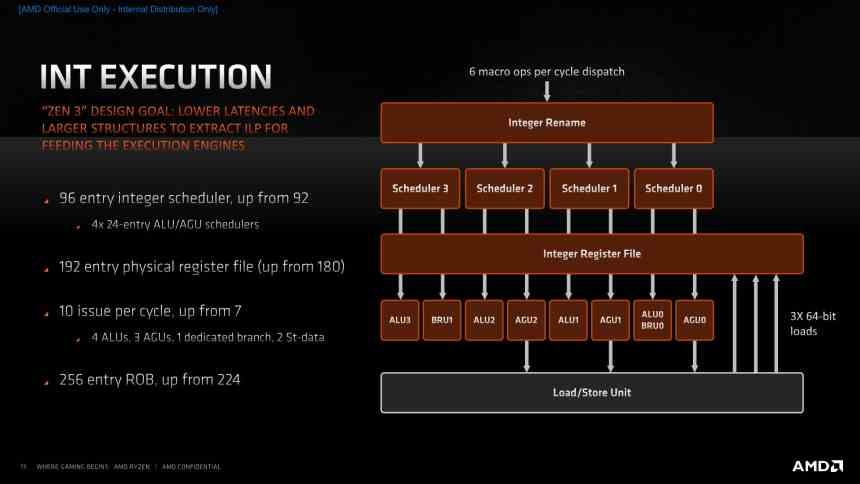

.A la hora de enviar instrucciones, Zen 3 sigue teniendo una unidad de Dispatch que envía 6 Macro-Ops por ciclo a las unidades de ejecución, por lo que el IPC máximo por núcleo se mantiene en 6 y en teoría no ha aumentado. Como curiosidad, el Front-End del procesador está equipado para enviar 8 instrucciones de manera simultánea, lo que da entender que es posible que en una futura iteración de la arquitectura Zen podríamos ver un aumento de rendimiento a través de aumentar la cantidad de unidades de ejecución, pero en Zen 3 se utiliza para

Pero aumentar la cantidad de unidades de ejecución no es la única forma de aumentar la cantidad de instrucciones por ciclo simultáneas que puede ejecutar un procesador. Ya que uno de los problemas con los que se enfrentan los arquitectos encargados del diseño de un procesador es la cantidad de recursos disponibles para construir la arquitectura al completo, esto lleva que muchas veces que haya diferentes instrucciones que comparten un mismo camino a la hora de ejecutarse.

Si dos instrucciones que están funcionando en paralelo utilizan el mismo camino hasta que estas son resueltas entonces se produce una contención donde una de las instrucciones acaba por enlentecer la ejecución de la otra, debido a que hay una parte en el pipeline que comparten otras, lo cual acaba afectando negativamente a la cantidad de instrucciones por ciclo y con ello el rendimiento del procesador.

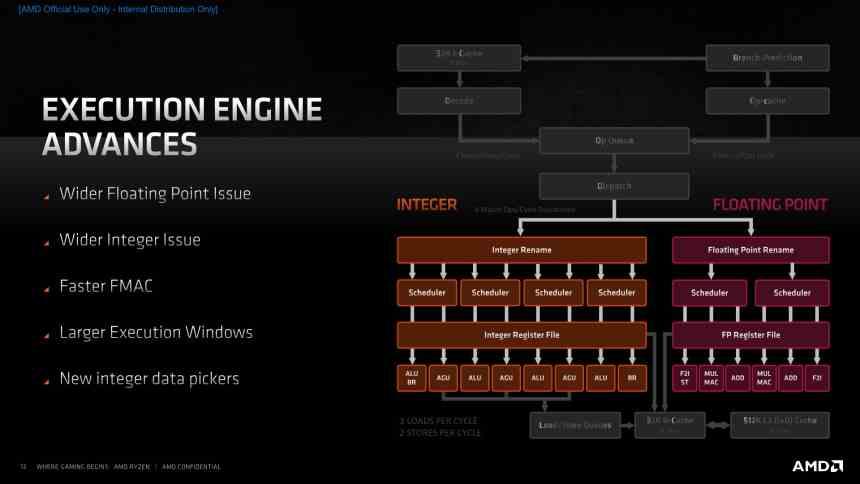

La idea de añadir nuevos caminos para que no haya conflictos a la hora de ejecutar ciertas instrucciones importante de cara a aumentar el IPC real de una arquitectura. Es el caso de las unidades de enteros del Zen 3 donde se ha ampliado la cantidad de caminos que pueden seguir las instrucciones que hacen uso de la unidad de enteros de 7 a 10 con tal de evitar la contención entre instrucciones.

Otros posibles cambios son el hecho de rediseñar el funcionamiento interno de ciertas instrucciones, haciendo que tarden menos ciclos en ejecutarse, como es el caso de la instrucción FMAC en las unidades de coma flotante que ha pasado de tener una latencia de 5 ciclos de reloj a solo 4 ciclos de reloj.

El otro tipo de unidad que AMD ha mejorado en Zen 3 son las llamadas Load/Store, encargadas de realizar la carga y almacenamiento de los datos desde y hacia fuera del procesador. Las unidades Load pueden cargar hasta 3 datos o instrucciones de manera simultánea cada una, por lo que ha habido un incremento del 50% respecto a Zen 2, mientras que las unidades de almacenamiento han pasado de 1 a 2 con 64 slots para almacenamiento.

El nuevo CCX con 8 núcleos

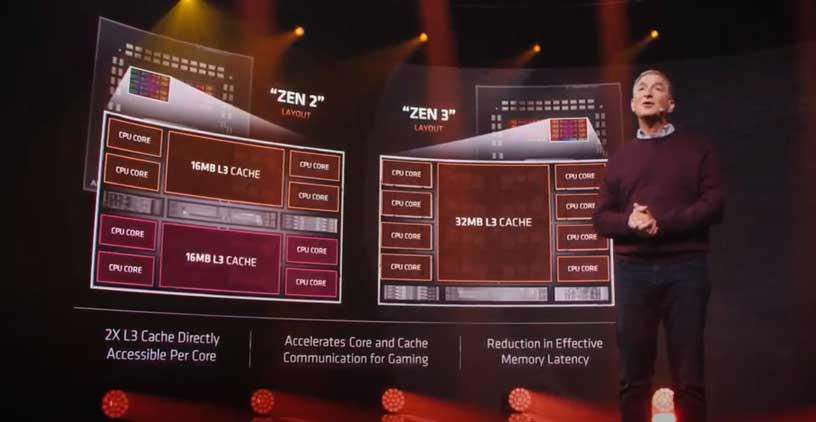

AMD ha reorganizado por completo el CCX por primera vez en las arquitecturas Zen, en vez de estar construido alrededor de 4 núcleos ahora lo está alrededor de 8 núcleos, lo que suponen cambios, especialmente en la cache L3, la cual ahora se encuentra unificada y compartida no por 4 sino por 8 núcleos.

La Cache L3 en las arquitecturas Zen es una Victim Cache, esto significa que adopta las líneas de cache descartadas por la cache L2 en su interior, esto significa que la cache L3 no participa en la demanda y captación de datos e instrucciones desde la memoria. Por lo que la ventaja a la hora de utilizar 8 núcleos está de cara a comunicar núcleos que antes se encontraban en diferentes CCX, la comunicación en ese aspecto ha mejorado.

Hay que tener en cuenta que nos podemos encontrar con varios hilos de ejecución que interoperen entre sí, si la distancia de comunicación entre los diferentes núcleos que ejecutan una misma instrucción aumenta, entonces el tiempo de ejecución también. Da igual que un núcleo sea más rápido que el otro ya que el más lento enlentecerá al más rápido. Es por ello que AMD ha unificado los 8 núcleos en un solo CCX, con tal de evitar las latencias por la interoperabilidad entre núcleos.

Pocos cambios en el Northbridge del procesador

En comparación con Zen 2, los cambios respecto al Northbridge, o Scalable Data Fabric según la jerga de AMD, son pocos.

- En el caso de los Ryzen 5000 para escritorio, basados en chiplets, los cambios respecto al IOD de los Ryzen 3000 son casi nulos, excepto en el soporte de memorias DDR4 más rápidas que las que soporta Zen 2, así como una mejor optimización en cuento al consumo energético.

- Lo mismo se puede decir de los SoCs monolíticos basados en Zen 3, excepto por el nuevo CCX, el resto del procesador es el mismo que los que están basados en Zen 2.

En realidad, deberíamos ver un nuevo SDF o IOD con la llegada de la memoria DDR5 y nuevos estándares de E/S como es el PCIe 5.0, pero esto debería llegar al mismo tiempo que AMD lance la arquitectura Zen 4 o puede ser que nos encontremos con una serie Ryzen 6000 con un nuevo IOD, pero haciendo uso de núcleos Zen 3, pero eso solo nos lo puede decir AMD.