El Intel Architecture Day de este año está dando mucho de qué hablar, y es que además de presentar en sociedad las características de sus GPU gaming dedicadas «Alchemist« o hablar de su arquitectura de GPU para aceleradores de servidores, la marca también ha dado datos de su próxima generación de procesadores Xeon, conocida como Sapphire Rapids, y más concretamente ha hablado de cómo gestionará la memoria HBM + DDR5… y lo hace de una manera que recuerda «demasiado» a la primera generación AMD EPYC.

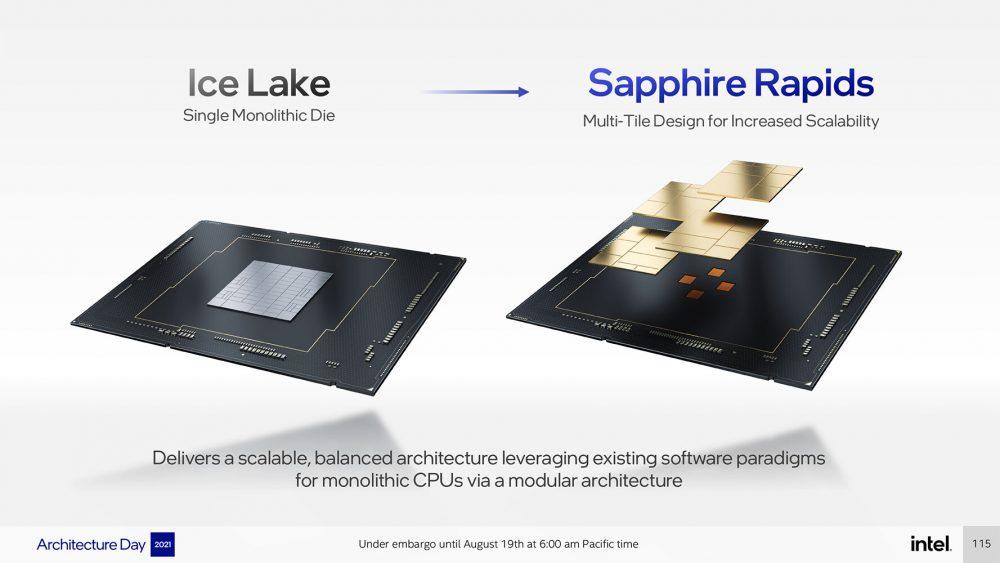

Los próximos procesadores Xeon «Sapphire Rapids» de Intel presentan una topología de interfaz de memoria que se parece mucho a la de los AMD EPYC «Rome» de primera generación, con un diseño modular con varios chips en el procesador. En 2017, los procesadores Xeon «Skylake-SP» tenían una matriz monolítica, pero esa era ya ha pasado a la historia y parece que los chips con varios tiles son el futuro de la computación moderna.

La topología de memoria de Intel Sapphire Rapids, con HBM + DDR5

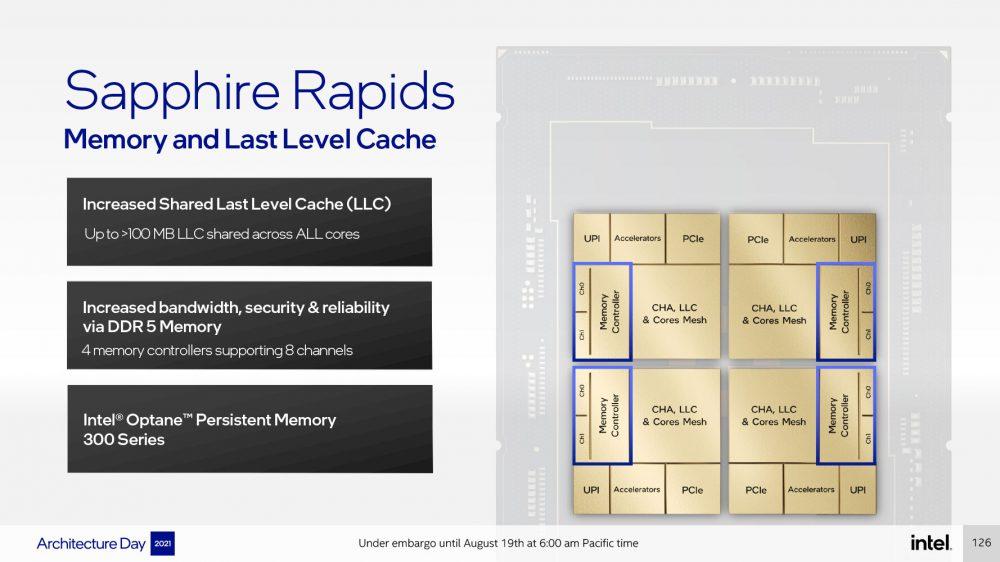

A pesar de estar distribuidos en múltiples mosaicos de controladores de memoria, Intel describió la interfaz de memoria DDR4 de 6 canales como una ventaja sobre EPYC «Rome»; el primer procesador empresarial basado en Zen de AMD era un módulo de varios chips de cuatro matrices «Zeppelin» de 14 nm y 8 núcleos, cada uno con una interfaz de memoria DDR4 de 2 canales que se sumaba a la E/S de 8 canales del procesador. Al igual que Sapphire Rapids, el núcleo de la CPU de cualquiera de los 4 die tiene acceso a la memoria y E/S controladas por cualquier otro die, ya que los cuatro están conectados en red a través de Infinity Fabric en una configuración que, esencialmente, se parece a «4P en un palo».

Con Sapphire Rapids, Intel está adoptando un enfoque sospechosamente parecido: tiene cuatro mosaicos de cómputo (matrices) en lugar de una matriz monolítica, que según Intel ayuda con la escalabilidad en ambas direcciones; cada uno de los cuatro mosaicos de cómputo tiene una interfaz de memoria DDR5 de 2 canales o HBM de 1024 bits, que se suma a la E/S total de DDR5 de 8 canales del procesador.

Intel dice que los núcleos de CPU de cada mosaico tienen el mismo acceso a la memoria, la caché de último nivel y las E/S controladas por cualquier die. La comunicación entre mosaicos se maneja mediante medios físicos EMIB (cableado de paso de golpe de 55 micrones); UPI 2.0 constituye la interconexión entre sockets, y cada uno de los cuatro mosaicos de cómputo tiene 24 enlaces UPI 2.0 que operan a 16 GT/s.

Intel no ha detallado cómo se presenta la memoria al sistema operativo o la jerarquía NUMA, y sin embargo gran parte del esfuerzo de ingeniería de Intel parece estar enfocado en hacer que esta E/S de memoria inconexa funcione como si «Sapphire Rapids» fuera un die monolítico. La compañía afirma que «un ancho de banda transversal elevado y de baja latencia constante es un denominador común en todo el SoC».

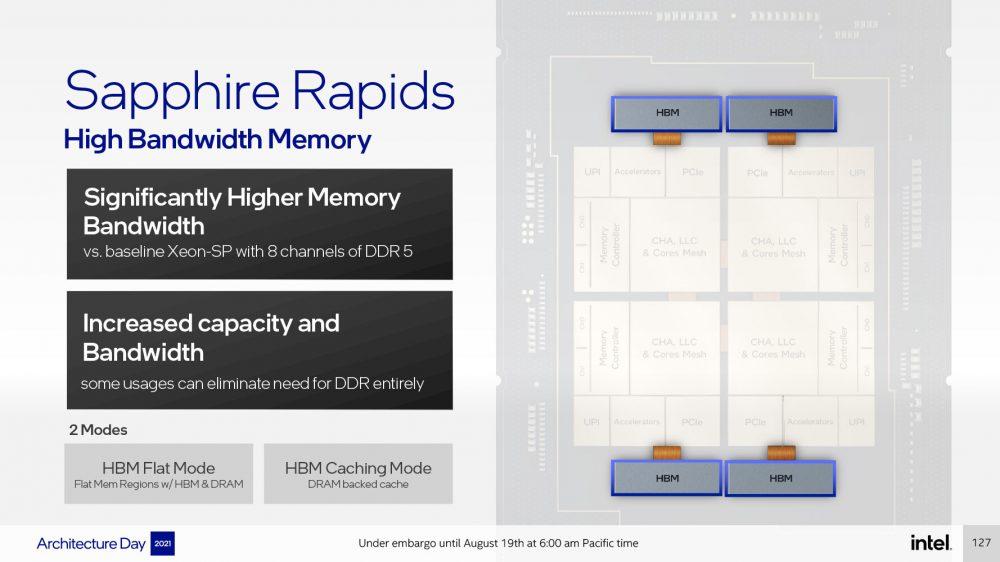

Otro aspecto interesante de los procesadores Xeon «Sapphire Rapids» es la compatibilidad con HBM, que podría cambiar las reglas del juego para el procesador en los mercados de computación de alta densidad y HPC. Los modelos específicos de procesadores Xeon Sapphire Rapids podrían venir, por lo tanto, con HBM en el mismo die del procesador.

Esta memoria se puede utilizar como caché sacrificable para las cachés en la matriz de los mosaicos de cómputo, mejorando enormemente el subsistema de memoria, trabajar exclusivamente como una memoria principal independiente, o bien incluso funcionar como memoria principal sin niveles junto a la RAM DDR5 con regiones de memoria planas en el sistema. Intel se refiere a estos como modos HBM + DDR5 visibles por software y HBM + DDR5 transparentes al software.