La palabra chiplet hace unos años nos sonaba ridícula, pero a día de hoy se ha convertido en un futuro seguro. Especialmente por el hecho que trae consigo una reducción de costes y rompe con las limitaciones del sistema monolíticos en cuanto a costes y tamaño. Por lo que es completamente normal que la industria terminará desarrollando un conector universal entre chiplets al que han bautizado como UCIe.

Con el aumento de los costes en la producción de procesadores la adopción de los chiplets para construir con varios chips lo que antes se hacía con uno solo es una realidad. A nivel de PC todos y cada uno de los grandes diseñadores de hardware han lanzado ya o tienen a la vuelta de la esquina una arquitectura construida de dicha manera. Por lo que tarde o temprano tenían que ponerse de acuerdo para la creación de un conector universal que permitiese comunicar los chiplets de las diferentes marcas entre sí.

La Industria lanzá el Universal Chiplet Interconnect Express

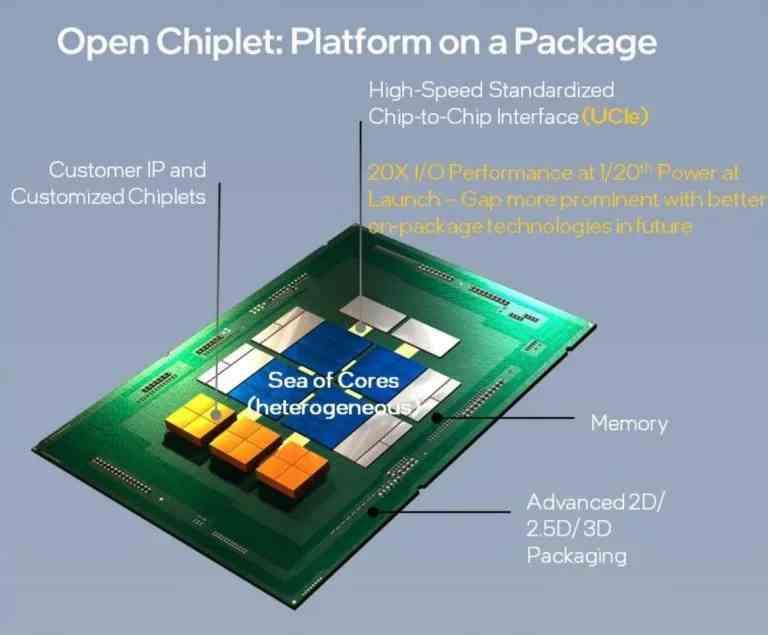

Las tres grandes fundiciones del mundo (TSMC, Intel y Samsung) junto a una serie de socios tecnológicos cómo ARM, Google, Meta, Microsoft y Qualcomm han lanzado un nuevo estándar. El cual consiste en una interfaz de comunicación a la que han bautizado como UCIe o Universal Chiplet Interconnect Express. La cual sirve para intercomunicar los diferentes chiplets montados en un sustrato común. Es decir, un procesador que en vez de estar compuesto por una sola pieza lo está por varias intercomunicadas entre sí.

El nuevo estándar UCIe se basa en el PCI Express con Compute Express Link y entre otras cosas permitirá crear chiplets compuestos por piezas de un solo fabricante, si no que podremos ver arquitecturas donde se combinen no solo elementos con diferentes procesos de fabricación, sino también de proveedores distintos. Lo cual cambia por completo el paradigma actual, ya que hasta el momento las soluciones de este tipo suelen centrarse en soluciones de un mismo fabricante al no existir hasta el momento un estándar universal.

En todo caso la existencia del nuevo estándar no es algo que nos deba sorprender, especialmente por el hecho que las colaboraciones entre fundiciones para la creación de las diferentes piezas de una misma CPU, GPU o APU serán cada vez más comunes. El ejemplo perfecto de ello lo tenemos en las colaboraciones entre Intel y TSMC para los futuros proyectos de la primera.

¿Cuáles son las características del UCIe?

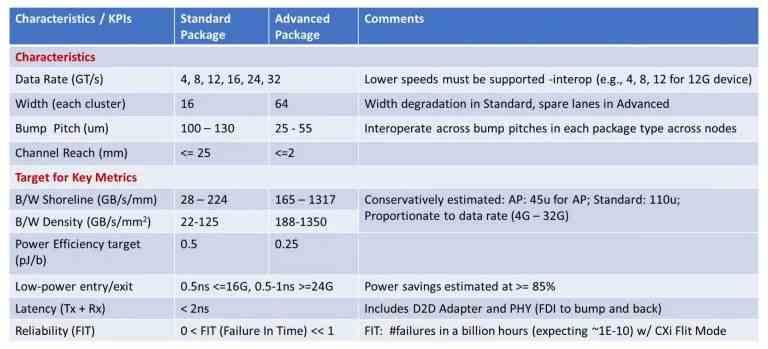

Por el momento el estándar no es definitivo, pero han lanzado una serie de especificaciones iniciales en forma de la versión 1.0 del estándar. La cual viene con dos tipos de interconexiones distintas. No olvidemos que estas hacen referencia a interconexiones en vertical de cada uno de los chiplets respecto al interposer que es el sustrato de comunicación sobre el que van montados para transmitir la señal y, por tanto, los datos. Esto les permite alcanzar anchos de banda por encima del terabyte por segundo a unos niveles de consumo de hasta 0,25 pJ por bit transmitido.

Traducido a algo que se pueda entender en lenguaje convencional se ha de tener en cuenta que la velocidad de transferencia hacía la RAM tradicional en la actualidad suele estar entre los 6 y 8 pJ/bit de media dependiendo del tipo de memoria utilizada. El bajo consumo es una de las claves de este tipo de interconexiones, las cuales están pensadas para trasmitir grandes cantidades de anchos de banda entre los diferentes componentes. Lo cual es clave para CPU compuestas por decenas de núcleos en el mercado servidor, así como las GPU compuestas por chiplets.