El próximo estándar PCIe 6.0, programado para «salir» en 2021, ha logrado esta semana alcanzar un nuevo hito en su desarrollo ya que el PCI-SIG ha lanzado la versión 0.7 de la especificación bajo el nombre de «borrador completo«, lo que significa que la tecnología ya se ha definido y sus especificaciones se han validado utilizando chips de prueba. Te contamos todas las novedades y características que aportará a los PCs del futuro.

A pesar de que los PCs actuales todavía siguen utilizando interfaces PCIe 3.0 y 4.0, desde hace ya tiempo se está desarrollando la sexta iteración de esta tecnología. Que la especificación PCIe 6.0 ya se encuentre como borrador completo significa en esencia que la tecnología ya está lista y es funcional, por lo que solo es cuestión de tiempo hasta que lancen la versión final y se lance al mercado, según las previsiones en el próximo año 2021.

PCIe 6.0, ocho veces más rápido que el PCIe de tu placa base

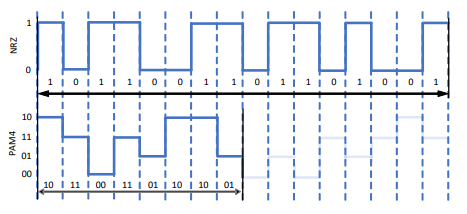

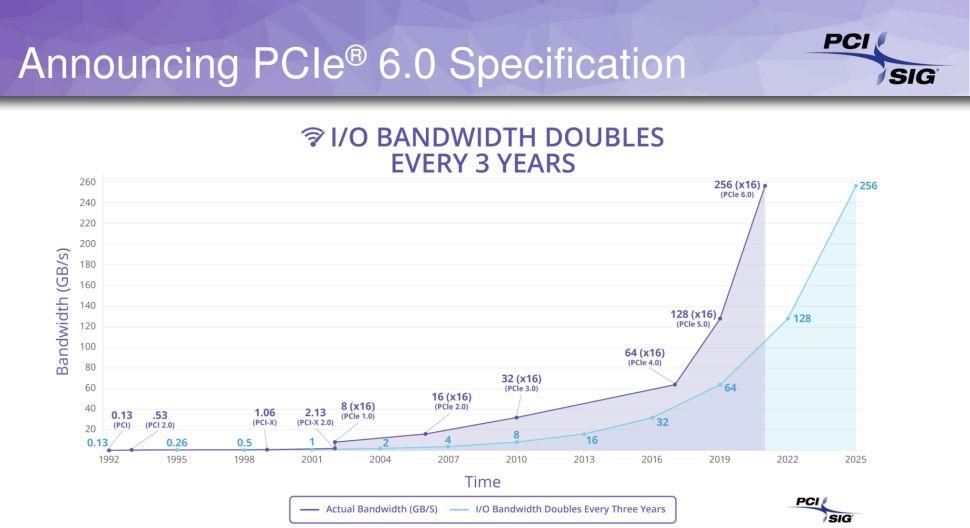

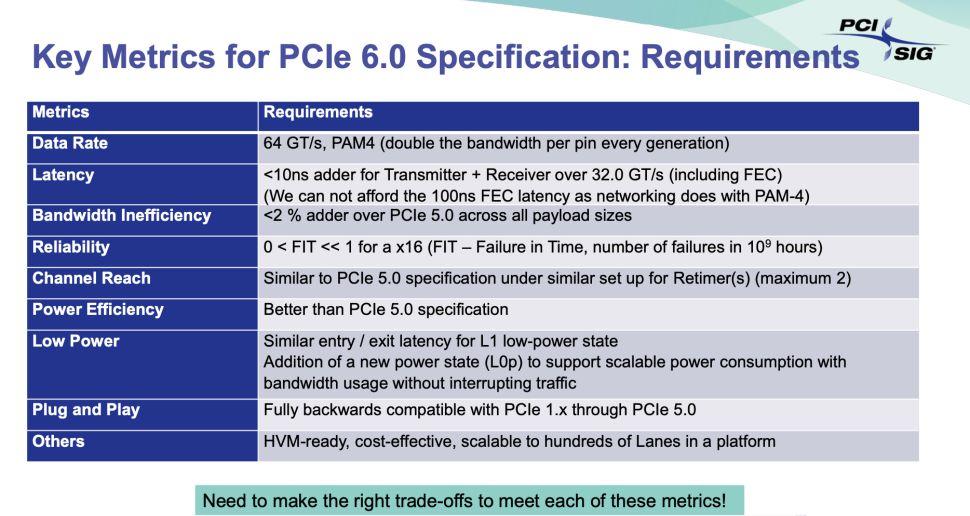

PCIe 6.0 vuelve a duplicar la tasa máxima de transferencia de datos, que ahora será de 64 GT/s por pin frente a los 32 GT/s de PCIe 5.0 o a los 16 GT/s de PCIe 4.0. En un intento por aumentar la velocidad de transferencia de datos y ancho de banda, la nueva interfaz ha adoptado PAM4 (modulación de amplitud de pulso con señalización de cuatro niveles), que también se utiliza en tecnologías de red de gama alta como InfiniBand o en la memoria gráfica GDDR6X.

Además, PCIe 6.0 utiliza corrección de errores de reenvío (FEC) de baja latencia para garantizar una alta eficiencia en la transmisión de datos. En general, PCIe 6.0 supone un gran paso adelante para esta interfaz, pero dado que introduce bastantes innovaciones técnicas los fabricantes deberán acelerar su desarrollo si quieren que llegue a tiempo al mercado (al menos «a tiempo» según sus previsiones, que eran 2021).

El lanzamiento de la versión 0.7 del borrador de PCI-Express 6.0 es particularmente importante dado que tras ésta ya no se podrán añadir nuevas características; esto es así porque las especificaciones eléctricas de la tecnología ya se han validado utilizando chips de prueba totalmente funcionales. De hecho, en esta etapa ya hay varias compañías que pueden tener implementaciones reales del bus de datos listas (pero no por ello necesariamente anunciadas todavía).

Los pasos del proceso de especificación

Cada una de las versiones o pasos del proceso de especificación tienen un significado muy importante, entre los que destacan cinco puntos principalmente:

- Versión 0.3: el concepto. Este borrador describe los objetivos globales de la tecnología y describe cómo se debe llegar a ellos. Para PCIe 6.0, precisamente se definieron los 64 GT/s de ancho de banda, el uso de PAM4 y FEC.

- Versión 0.5: el primer borrador. Aquí ya se deben haber logrado los objetivos dispuestos en el borrador 0.3, y también se incluyen los aspectos de arquitectura y requisitos.

- Versión 0.7: el borrador completo. En este punto, que es donde estamos ahora mismo, se definen los métodos y requisitos funcionales necesarios para lograr los objetivos y, lo que es más, las especificaciones eléctricas deben de haberse validado con chips reales. En este punto los miembros de PCI-SIG ya pueden proponer las primeras versiones de la siguiente interfaz.

- Versión 0.9: el borrador final. En este punto ya se están realizando análisis internos en PCI-SIG para desarrollar sus patentes. No se permiten más cambios.

- Versión 1.0: el lanzamiento. A partir de esta versión los cambios y mejoras tienen que ir a través de nueva documentación y cambios de ingeniería (ECNs).

Con respecto a PCIe 6.0, la versión 0..5 se publicó en el mes de febrero del presente año, hace unos ocho meses. Si todo va como tienen planeado, la nueva tecnología se finalizará hacia la segunda mitad del año 2021, pero esto no significa que empecemos a ver los primeros productos que la incorporen tan pronto, sino que tendremos que esperar a que los fabricantes puedan empezar a implementarla en su hardware.

Por ejemplo, el PCI-SIG publicó la versión 1.0 de PCI-Express 5.0 a finales de mayo de 2019, pero las primeras plataformas que soportarán esta tecnología por parte de Intel y AMD no llegarán al mercado hasta finales de 2021. A este ritmo, esto significa que si PCI-SIG lanza la versión 1.0 de PCI-Express 6.0 a finales de 2021 significa que veremos los primeros equipos en incorporarla entre 2023 y 2024.