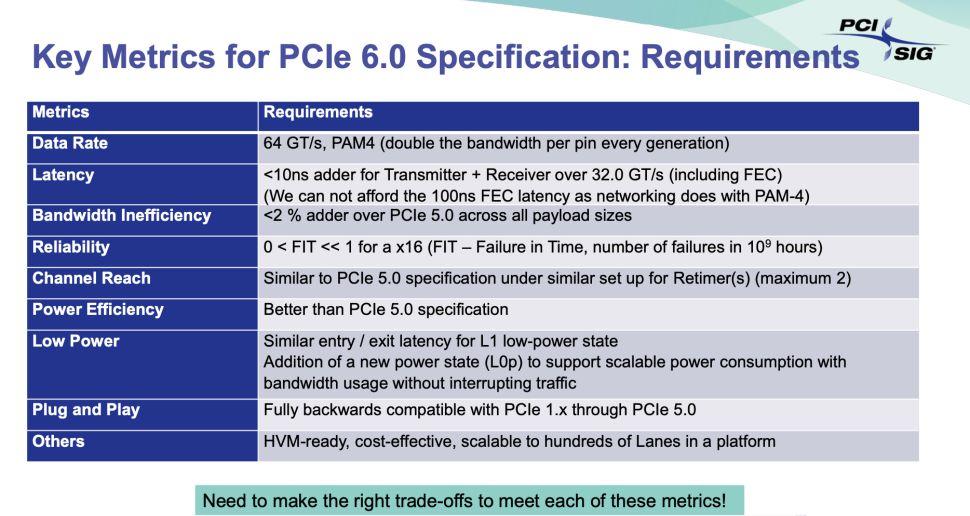

La especificación PCIe 6.0 ya está entre nosotros en sus primeros borradores y como tal, hay bastantes novedades, las cuales ya tratamos en un artículo sobre esta nueva versión del bus. Pero a diferencia de otras hay una característica que ha tenido que ser incluida y que marcará el devenir de las placas base y su paso de la versión 5.0 a esta nueva 6.0, porque, aunque esta última sea compatible, la primera no va a serlo con ella debido a una característica llamada Forward Error Correction o FEC.

¿Por qué ha sido tan complicado desarrollar este nuevo estándar? ¿por qué se ha tardado tanto tiempo en general y tan poco desde su versión 5.0? Bueno, es que las mejoras son más que amplias, ya que actualmente estamos en PCIe 4.0 y hablamos de cuadriplicar su velocidad en el mismo ancho de líneas x16. Por lógica, PCI-SIG ha tenido que implementar una serie de mejoras que garanticen la entrega de datos, donde entre ellas está PAM 4 y FEC, pero, ¿qué es esta última y cómo funciona en este bus en concreto?

Forward Error Correction o FEC, una tecnología necesaria para PCIe 6.0

Aunque ya hemos hablado de PAM 4 como decimos, no se entiende FEC sin esta. PAM 4 lleva algunos años entre los ingenieros de redes, donde en los grandes centros de datos ha sido el santo grial para salvar infraestructuras o actualizarlas, entre otras tecnologías.

Pero no se queda ahí, ya que ha sido introducida en el bus PCIe por motivos obvios de modulación de las ondas y por supuesto, por lograr un mayor ancho de banda por cada Hz disponible. Aun con sus ventajas también tiene desventajas que deben ser paliadas, como su señal más frágil, por ello y siendo el motivo real de su implementación, el PCI-SIG incluyó el llamado Forward Error Correction o FEC.

Como su propio nombre indica, FEC no es más que un medio para corregir errores en el envío y recepción de una señal entre distintos enlaces u Host, donde logra proporcionar un flujo constate de datos con corrección de errores incluido.

Lo que consigue es que se pase de una señal que puede ser crítica en cuanto a la integridad de los datos a una señal estable y sin errores, lo cual garantiza el correcto funcionamiento del equipo y sus componentes.

El problema de esta tecnología es su alta latencia

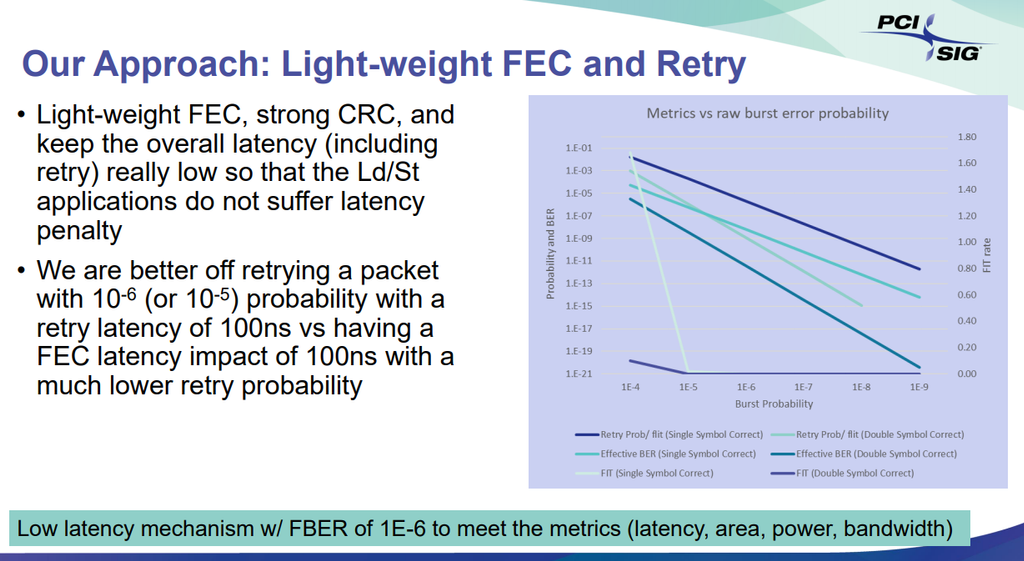

Pero no todo lo que reluce es oro. FEC de por sí y por su naturaleza de corregir los errores encontrados al más puro estilo CRC no es apto como tal para un bus como PCIe y menos en su versión 6.0 con 128 Gb/s, para nada.

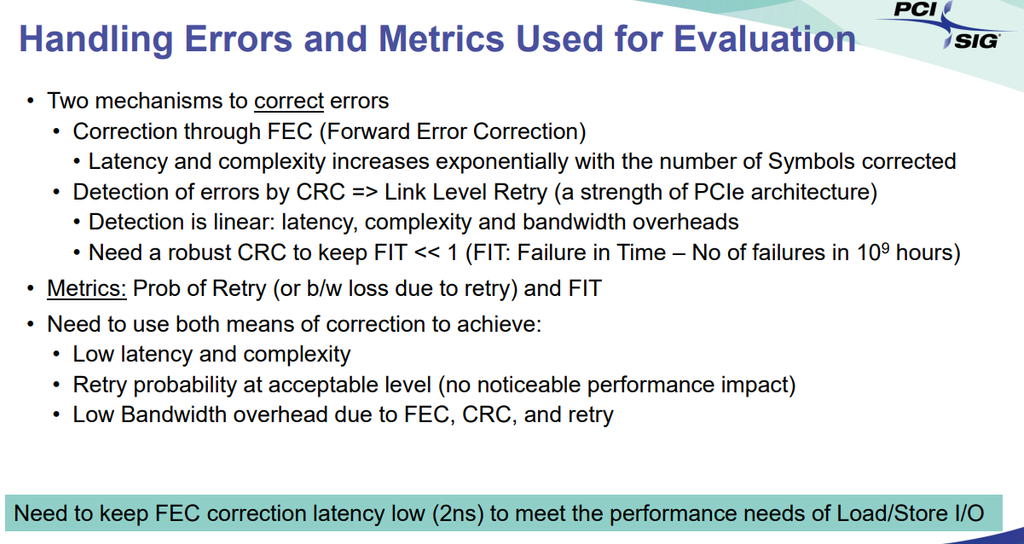

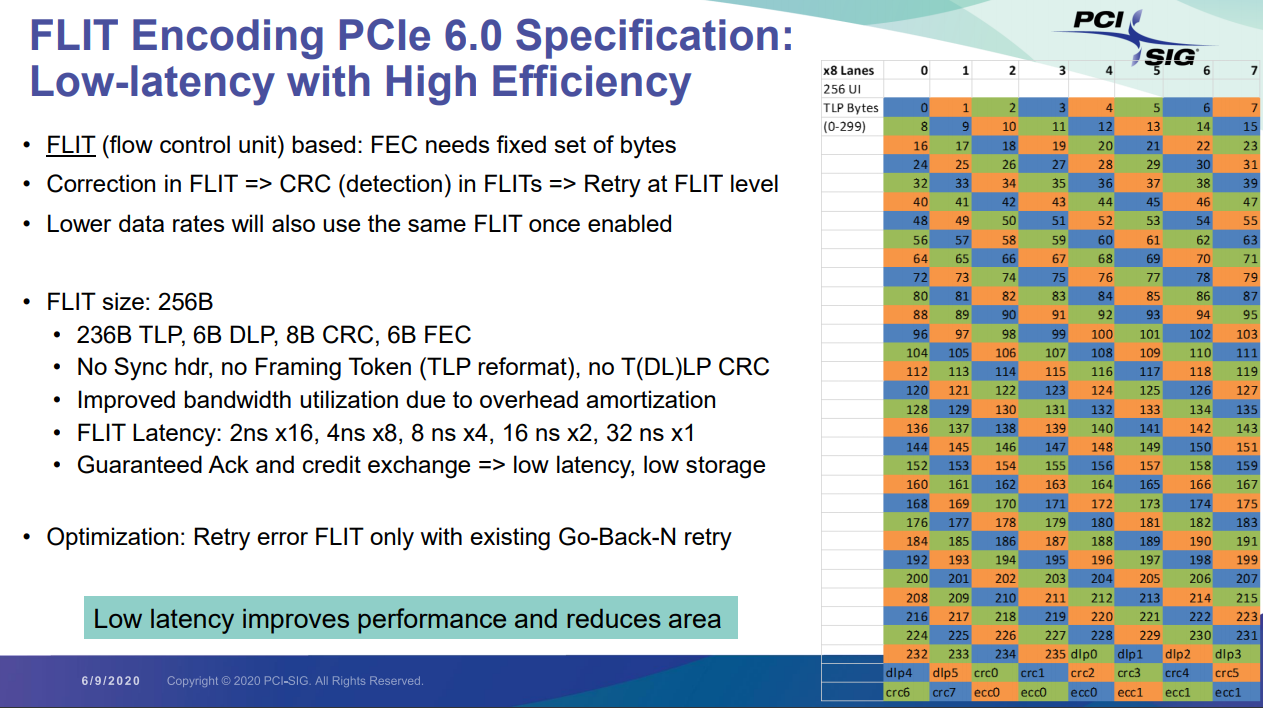

El problema que tiene FEC es que introduce latencia al bus, por lo que la tasa de entrega de paquetes se reduce y puede generar un delay no querido. Por ello, la tecnología PCIe 6.0 utiliza un método único para lograr una baja latencia a través de una combinación de una tasa de error de primer bit (FBER en 10-6) combinado con un FEC ligero de baja latencia para completar la corrección inicial.

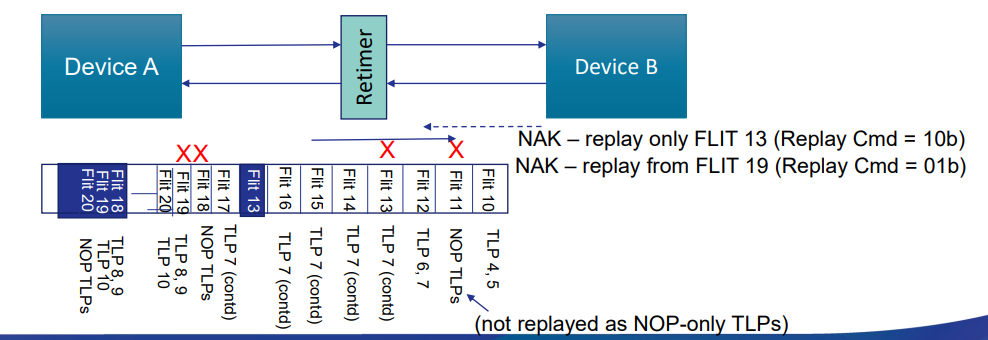

Pero eso sí, FEC puede corregir errores, pero para ello debe conocer la ubicación exacta y la magnitud del error para realizar las correspondientes elecciones. ¿Por qué? muy sencillo, el objetivo era pagar una penalización de latencia cercana a cero (cero es imposible) y luego confiar en un CRC muy robusto para la detección, combinado con una reproducción rápida del nivel de enlace para manejar cualquier error que el FEC no pudiera corregir (no es infalible y por ello se necesita CRC).

En cambio, si la velocidad baja de los 128 Gb/s en PCIe 6.0, es posible que FEC se pueda omitir, algo que generará menor latencia al sistema.

¿Qué pasará si FEC no puede corregir los errores? Pues que es el momento de que entre CRC generando un NAK, pero disparará la latencia al ser de ida y vuelta para comprobar los datos hasta los 100 ns.

Queda claro que el uso de FEC está justificado, no es perfecto, pero es el mejor método para generar la menor latencia posible teniendo corrección de errores, algo totalmente necesario para algo tan delicado como el paso de datos de CPU, memoria y GPU.