Desde hace ya bastante tiempo, en PC se utiliza el estándar PCI-Express para la interconexión de dispositivos, si bien es cierto que en la informática moderna su uso es casi exclusivo para conectar tarjetas gráficas y dispositivos de estado sólido a la placa base. Desde hace poco, la especificación PCI-Express 6.0 (también conocida simplemente como PCIe 6.0) está entre nosotros, así que en este artículo te vamos a explicar todos sus entresijos, novedades y qué mejoras trae con respecto a la quinta generación.

Como ya supondréis, la numeración «PCI-Express 6.0» se refiere a que estamos ante la sexta generación de esta interfaz, y esto significa que hay cinco generaciones predecesoras. Con cada nueva generación se implementan una serie de mejoras, y aunque por norma general la que recordamos todos es que «tiene más rendimiento», en realidad hay muchas otras características a tener en cuenta. Pero empecemos desde el principio…

¿Qué es PCI-Express?

PCI Express viene de las siglas en inglés Peripheral Component Interconnect Express, es decir, se trata de una interfaz de interconexión «exprés» de periféricos. A este respecto hemos de aclarar dos de estos términos:

- Periféricos: en PC, solemos pensar que los periféricos son el teclado, el ratón y los auriculares, pero cuando hablamos de hardware, en realidad se considera periférico a cualquier dispositivo que podemos poner y quitar, como puede ser la tarjeta gráfica o el SSD. Precisamente, y como hemos dicho antes, estos dos dispositivos periféricos son los más utilizados con esta interfaz.

- Interconexión: que hablemos de interconexión y no de conexión implica que la comunicación entre las dos partes es bidireccional, es decir, no se trata de un dispositivo que envía datos al otro como podría ser la tarjeta gráfica hacia el monitor, sino que ambos se comunican entre sí en los dos sentidos.

Por lo tanto, ya tenemos claro que PCI-Express no es sino una interfaz de interconexión; está desarrollada por el PCI-SIG, cuya existencia podríamos definir a grandes rasgos como un consorcio de fabricantes y diseñadores que se ponen de acuerdo para crear una interfaz con ciertos requisitos, de manera que sus dispositivos puedan funcionar en tándem y, precisamente, comunicarse entre sí siguiendo estos requisitos.

Esta interfaz se desarrolla desde el año 2003 hasta nuestros días, y comenzó como una evolución de los estándares AGP y PCI. La versión PCIe 1.0, presentada en 2003, era bastante simple pero ya representó grandes mejoras con respecto a AGP y PCI, pues contaba con una capacidad de transferencia de datos de 2,5 GT/s (GigaTransfers por segundo) y de 250 MB/s por cada vía de datos.

Si comparamos esto con el PCIe 5.0 actual, capaz de manejar 32 GT/s y 3.938 MB/s por vía de datos, desde luego las cosas han cambiado bastante. Pero esperad, que ahora llega PCI-Express 6.0 para volver a mejorar lo presente.

PCI-Express 6.0: especificaciones técnicas

| Velocidad de datos | 64 GT/s (el doble que PCIe 5.0) |

|---|---|

| Formato | PAM-4 con codificación por unidad de control de flujo (FLIT) |

| Alcance del canal | Provisión de SNR reducida en 9 dB |

| Retrocompatibilidad | Sí |

| Tasa de error de bits | 0.000001 |

| Dúplex | Completo |

Como es habitual cada vez que sale una nueva generación de la interfaz PCI-Express, la 6.0 ofrece literalmente el doble de ancho de banda que PCIe 5.0, es decir, 32 GT/s. Seguramente seáis conscientes de que, cuando hablamos de los zócalos PCIe de las placas base en PC, lo hacemos con un multiplicador, como por ejemplo PCIe 5.0 x16 que es el que actualmente usan las tarjetas gráficas. Esto es así porque, para que nos entendamos, cuentan con varios «carriles» que funcionan en paralelo, por lo que el ancho de banda se puede multiplicar.

Así, podemos encontrar interfaces PCIe de 1, 4, 8 y 16 carriles enviando datos en paralelo, y con PCIe 6.0 esto da como resultado un flujo de datos de hasta 256 GB/s (aunque en los SSD de formato M.2 esto es de 64 GB/s como máximo). Cuidado, porque hablamos del ancho de banda sumado en ambos sentidos, es decir, de lectura y escritura simultáneamente.

Retrocompatibilidad

La interfaz PCI Express ha sido siempre compatible hacia atrás con versiones anteriores del protocolo, lo que significa que podemos conectar una tarjeta PCI Express 1.0 en un slot PCI Express 6.0 y funcionará. Esto se llama retrocompatibilidad, y es gracias a que la disposición de los pines siempre ha sido el mismo en todas las versiones de la interfaz.

Ojo, porque esto es un arma de doble filo también, ya que para aumentar el ancho de banda no se pueden colocar pines adicionales y, por tanto, se ha de aumentar la velocidad de reloj a la que funciona la interfaz. Dicho de otra manera los bombeos de datos por segundo para transmitir los datos son más rápidos para generar mayor caudal, algo que puede tener inconvenientes como un mayor consumo y una mayor generación de calor.

¿El problema con PCI Express 6.0? A medida que aumentamos la velocidad de reloj de una interfaz, esta se va volviendo a la vez más inestable, y después de seis generaciones han tenido que hacer algunos cambios debido a la alta velocidad a la que funciona la interfaz de manera tradicional. El problema estriba en que para transmitir 256 GB/s en una interfaz Full Dúplex, la cual permite transmitir 1 bit por cada dirección simultáneamente, necesitamos que la velocidad de la interfaz suba hasta 128 GHz y a esas velocidades la integridad de la señal se ve seriamente comprometida.

Esto ha obligado a adoptar una serie de medidas para hacer posible el salto al PCI Express 6.0, empezando por la codificación, que es lo siguiente que os vamos a explicar.

La codificación PAM4 en PCIe 6.0

¿Cómo sabe una interfaz externa o interna de un chip si el valor es un 1 o un 0 (recordad que estamos en sistema binario)? En realidad es sencillo: dependiendo del voltaje al que se transmite la información. Los sistemas binarios se basan en el uso de dos voltajes con la suficiente distancia entre ellos para que la bajada o subida de voltaje haga que el receptor de la señal no se confunda.

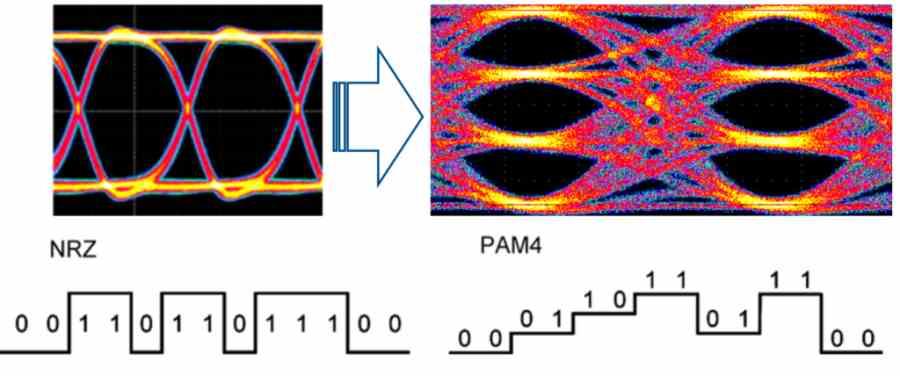

¿Qué tiene que ver esto con el PCI Express 6.0? Dado que no podemos aumentar el ancho de banda porque la señal se distorsiona, y tampoco el número de pines porque entonces no tendríamos retrocompatibilidad, se ha de buscar una solución alternativa. Al final, lo han encontrado utilizando la codificación llamada PAM4 (Pulse Amplitude Modulation 4), la cual ya hemos visto en las memorias GDDR6X.

Este tipo de codificación no se basa en dos valores como el sistema binario, sino en un total de cuatro valores distintos posibles de voltaje por cada uno de los pines. De esta manera, podemos codificar los valores 00, 01, 10 y 11 en cada pin: cuatro valores en total, en vez de los dos valores clásicos que serían 0 o 1.

Esta solución evita el tener que aumentar el ancho de banda y los pines, pero nos adelanta que en el PCI Express 7.0 ya no será posible desde los métodos convencionales. Quizás veamos el uso de fotónica y de interfaces ópticas, pero con las mejoras del PCI Express 6.0 recién salidas del horno, mejor tener paciencia con su sucesor.

PCI-Express 6.0 ya no se comunica… igual

El salto a PAM4 también ha cambiado la forma en la que la interfaz PCI Express 6.0 envía sus paquetes, pese a que es compatible con las generaciones anteriores, que hacen uso del anterior sistema llamado PAM2 o NRZ. La realidad es que el formato PAM4 no soporta el sistema de paquetes anterior y, por tanto, el protocolo de comunicación ha cambiado debido a ello.

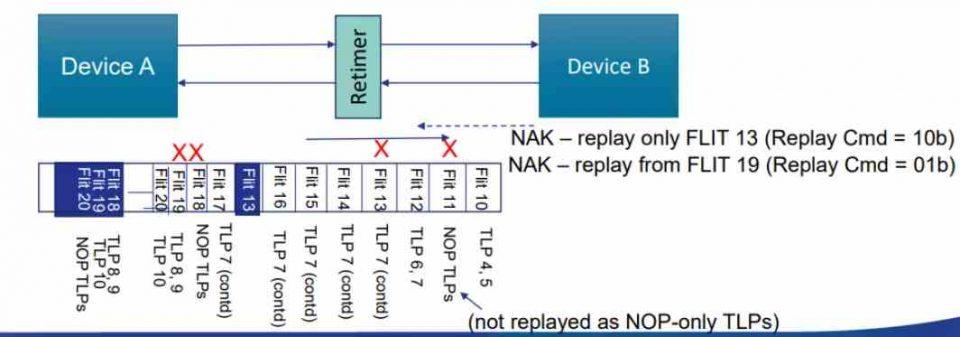

Antes os hemos mencionado que la alta velocidad de PCI-Express 6.0 puede provocar inestabilidad, y con ello vienen los errores, motivo por el que también ha sido necesario integrar un nuevo protocolo de corrección de errores llamado Forward Error Correction, o simplemente FEC, y que podéis ver representado en el diagrama de arriba. La desventaja es que esto ha añadido otro problema, y es que se ha aumentado notablemente la latencia al tener que pasar cada paquete de datos a través del sistema de corrección de errores.

Para paliar esto en el estándar PCI Express 6.0 se utiliza un tipo de paquete llamado FLIT. Un paquete no es más que un conjunto de bits con un destino en concreto. ¿La latencia de envío de cada FLIT? Depende de la cantidad de líneas de la interfaz, pero cada paquete tiene una latencia de solo 2 ns en un PCI Express 6.0 de 16 líneas, pero llega hasta los 32 ns en una interfaz con una sola línea.

El FEC solamente trabaja con tamaños fijos, y es por ello que el FLIT tiene un tamaño de 256 bytes por envío. Cada paquete o TLP puede tener un tamaño que va de los 0 bytes a los 4096 bytes y, por tanto, cada paquete puede estar compuesto por varios FLITS.

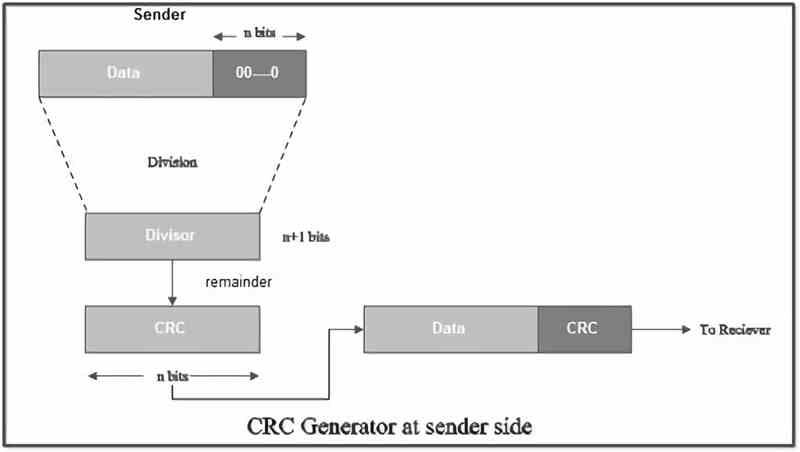

Y aquí es donde entra la comprobación de redundancia cíclica, conocida como CRC en inglés por sus siglas «Cyclic Redundancy Check». Se trata de un sistema de corrección de errores en el código que se usa normalmente en unidades de almacenamiento y en redes digitales, y que se ha integrado dentro del estándar PCI-Express 6.0 para comprobar que los datos transmitidos de extremo a extremo mantienen su integridad y ni un solo bit se ha visto cambiado en el proceso.

Esto se consigue con una serie de cálculos polinomiales realizados por una serie de unidades especializadas para ello que se incluyen con la interfaz. Esto es algo que tiene sentido con la enorme cantidad de datos que se van a transmitir y supone un ahorro especialmente en el caso de los futuros fabricantes de SSD que no van a tener que añadir esta funcionalidad en sus unidades, ya que viene de serie en la propia interfaz.

El modo de bajo consumo en PCI-Express 6.0

Para terminar, es interesante destacar que PCI-Express 6.0 añade un nuevo estado de bajo consumo bautizado como L0P. Este modo le permite a la interfaz recortar su consumo energético cuando el flujo de datos que se envía está por debajo de su máximo. Para ello, es capaz de modificar la velocidad de reloj a la que necesite el dispositivo conectado para los momentos puntuales en los que los datos a transmitir se encuentran en menor volumen.

Este mecanismo se encuentra estrechamente relacionado con las nuevas tecnologías introducidas en la sexta versión del PCIe 6, por lo que solo se podrá utilizar con dispositivos compatibles con esta generación de la interfaz (dicho de otra manera, para el modo de bajo consumo LoP no hay retrocompatibilidad, solo funcionará con dispositivos que tengan compatibilidad nativa con PCIe 6.0).