Con el anuncio durante esta semana de los primeros Apple Macintosh basados en procesadores con ISA ARM, después de haber anunciado la transición por parte de Apple hace unos meses, el tema ARM vs x86 ha aparecido y la pregunta de porque no hay CPUs con ISA x86 en dispositivos de bajo consumo ha vuelto a aparecer. ¿Pero cuáles son los motivos y los mitos alrededor de este tema?

Si alguna vez te has preguntado por qué no se ven smartphones, tablets y todo tipo de dispositivos que utilizan procesadores x86 con un consumo por debajo de los 10 W e incluso de los 5 W. Entonces deja que te digamos que no es por desinterés de Intel o AMD, sino que existen una serie de motivos para ello, una serie de barreras insalvables que tienen que ver con la naturaleza de la arquitectura x86.

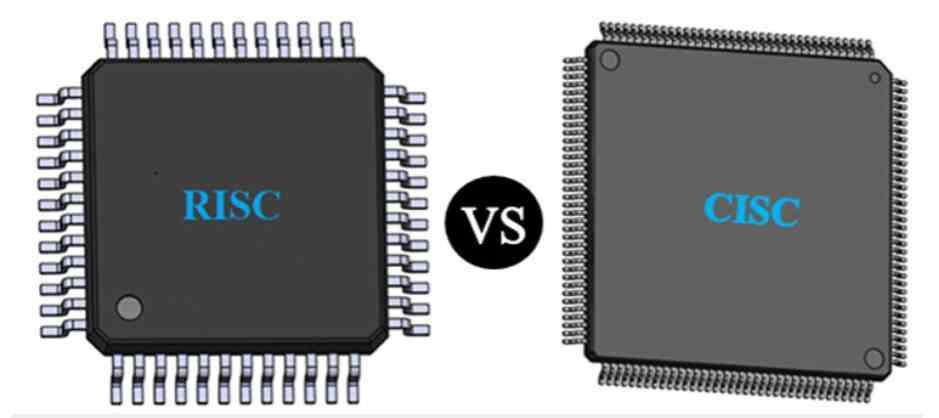

ARM vs x86 o CISC vs RISC

ARM son las siglas de Advanced RISC Machines, mientras que toda CPU basada en x86 se dice que tiene un set de instrucciones del tipo CISC. ¿Pero qué significa esto? RISC son las siglas de Reduced Instruction Set Computing o Computación con un conjunto de instrucciones reducido, mientras que CISC son las siglas de Complex Instruction Set Computing, Por lo tanto, es una forma de clasificar los conjuntos de instrucciones utilizados por los diferentes procesadores.

La principal diferencia es que debido a que RISC tiene un conjunto de instrucciones reducido, acaba siendo necesario el uso de varias instrucciones más simples para ejecutar una más compleja, mientras que en el caso de una unidad CISC muchas instrucciones complejas se puedan realizar en una sola instrucción, por lo que las unidades CISC ahorran espacio en lo que a la cantidad de memoria se refiere.

Por ejemplo, el código máquina de una suma en RISC sería el siguiente:

- Almacena el primer operando en el registro acumulador

- Carga el segundo operando y realiza la suma.

- Almacena el resultado en el registro acumulador.

En cambio, en un procesador CISC:

- Suma el primer y segundo operando.

Por lo que respecto al código máquina, un binario RISC tiene son más instrucciones y por tanto ocupa mucha más memoria, mientras que en el binario CISC el código es mucho más ligero.

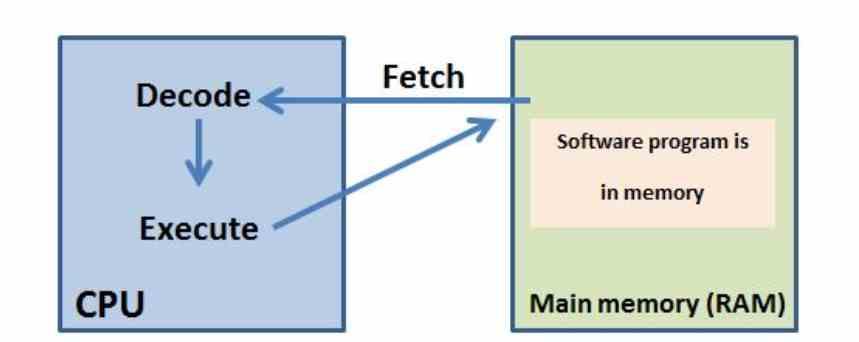

El ciclo de instrucción de los procesadores

Todo procesador, independientemente de si es CISC o RISC tiene que pasar por cuatro etapas distintas que son:

• Fetch: La siguiente instrucción es captada en memoria.

• Decode: La instrucción es decodificada y preparada para su ejecución.

• Execute: La instrucción es ejecutada por una de las unidades de ejecución de la CPU. y ell resultado de la instrucción es escrito en el banco de memoria o registro correspondiente.

En los procesadores RISC una instrucción que ejecuta la CPU equivale a una instrucción del código binario, mientras que en los CISC una instrucción en código máquina se puede descomponer en varias microinstrucciones, lo que significa que la unidad de Decode de los procesadores CISC es mucho más compleja y es otro de los factores más importantes de cara a que los x86 tengan un mayor consumo.

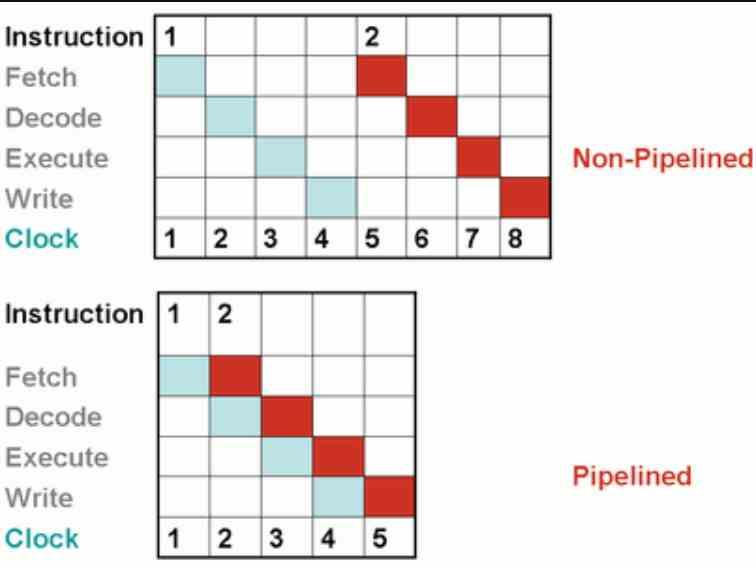

Segmentación en x86 vs ARM

Una de las particularidades que tienen todas las CPUs desde principios de los años 90 es la segmentación, consistente en que en vez de esperar a que una instrucción se ejecute al completo en el procesador para dar paso a la siguiente, estas se van adelantando por cada etapa del ciclo de instrucción, la cual puede estar dividida en varias subetapas cada una de ellas.

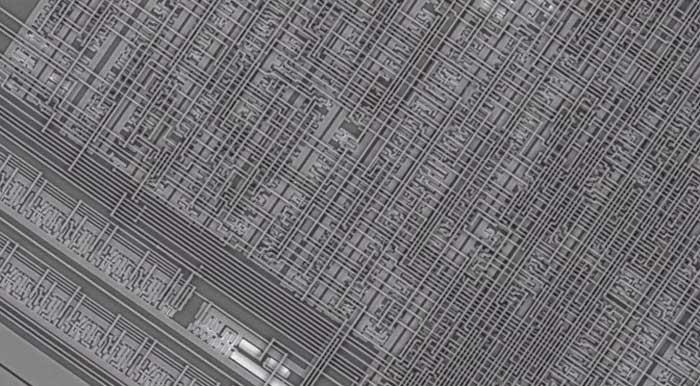

Dado que los procesadores RISC tienen una correlación directa entre la cantidad de instrucciones en el código binario y las que ejecuta la CPU es muy fácil segmentar las instrucciones en varias etapas. Pero en un x86 es sumamente difícil, ya que la segmentación se hace sobre las microinstrucciones generadas durante la etapa Decode, lo que supone aún más circuitería adicional funcionando y consumiendo energía de manera continua.

No solo eso, sino que mientras por ejemplo los opcodes de cada instrucción en ARM son de tamaño fijo en el caso de los x86 son variables, lo que hace mucho más complejo la decodificación de instrucciones en microinstrucciones en el caso de los procesadores x86.

Menos registros equivalen a una menor eficiencia energética

La ISA x86 dispone en su interior de muchos menos registros que otras ISAS, esto hace que muchas instrucciones se tengan que realizar sobre la memoria, o las caches, lo que provoca que estás acaben consumiendo mucha más energía a la hora de ejecutarse. Este es un problema clásico de la arquitectura x86 y no por el hecho de ser una arquitectura CISC.

Para entenderlo hay que tener en cuenta el consumo energético de cada operación depende de la distancia entre el dato y el procesador.

x86 vs ARM en dispositivos de muy bajo consumo.

Intel lo intento hace ya unos años con el fallido procesador Intel Medfield.

Es más, una de las posibilidades que se han barajado es la creación de una CPU mixta, la cual consiste en un x86 que internamente decodifique sus instrucciones en instrucciones ARM y permita una total compatibilidad entre ambas ISAS, lo cual sería el procesador definitivo.

Pero tristemente ni a ARM ni a tampoco a Intel y AMD, especialmente estas últimas, les interesa realizar este procesador mixto ya que para hacer que funcione en ambos modos sería muy dificil de conseguir, aparte que la decodificación de instrucciones x86 seguiría siendo un problema, por lo que tendríamos un procesador que solo podría funcionar de un modo y donde la mayoría de la circuiría estaría desaprovechada.