El escalado en los nodos de fabricación de chips es algo necesario para que la tecnología avance, especialmente en términos de eficiencia, pero al mismo tiempo se aumenta la dificultad de fabricación y se incrementan los problemas. En este artículo vamos a echar un vistazo a estos problemas, que básicamente son los que están impidiendo que se avance más deprisa en cuanto a la reducción de los nodos de fabricación.

João Geada, jefe de ingeniería en Ansys, concedió hace poco una entrevista para debatir sobre los problemas de producción que se generan al reducir la litografía en los nodos de fabricación, y en este artículo os vamos a ofrecer su punto de vista al respecto de éstos.

La ley de Moore en los nodos de fabricación

El primer transistor se fabricó a finales de la década de los 60, y los primeros circuitos integrados de Intel no llegaron hasta 1970. Desde entonces, se ha estado duplicando la cantidad de transistores que contienen los chips cada 18 meses, tal y como dice la Ley de Moore, pero estamos en un punto en el que ya están encontrando bastantes problemas para poder seguir cumpliendo esta premisa.

Según Geada, llevan ya tiempo recurriendo a «trucos» para poder mantener viva esta ley, pero todavía les quedan muchos más en la manga para poder seguir haciéndolo. La mayoría de las fundiciones tienen ya algún tipo de plan para llegar a los 3 nm e incluso nodos de fabricación más pequeños, aunque los números en realidad no significan mucho en estos días, solo son una aproximación de la densidad que se puede lograr.

Los nodos de fabricación heterogéneos, ¿son el futuro?

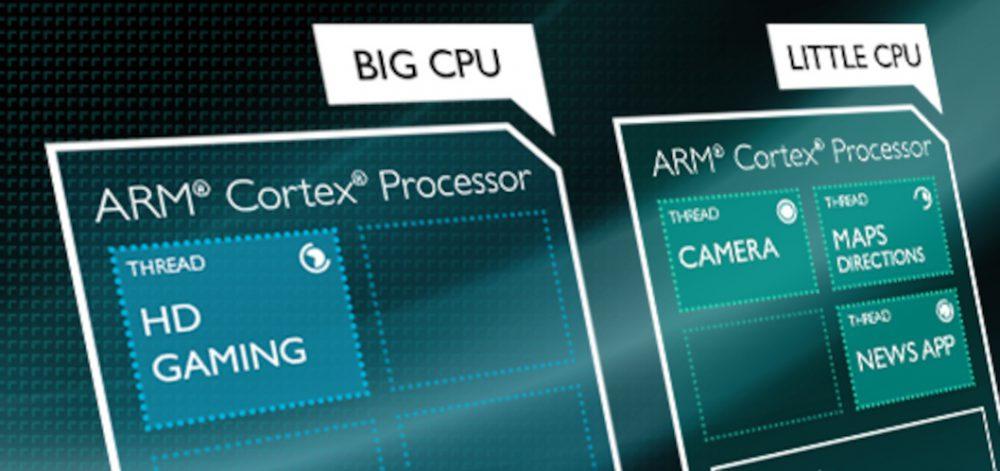

En los últimos tiempos parece que todos los principales fabricantes están orientando sus diseños a los procesadores con arquitectura heterogénea (núcleos «grandes» y «pequeños»). En general, la heterogeneidad está regresando en múltiples dimensiones a medida que se avanza hacia geometrías más pequeñas en los nodos de fabricación, pero esto a la vez hace que cada vez sea más caro fabricar una oblea.

Una de las cosas que impulsaba la Ley de Moore es que el coste por transistor estaba disminuyendo, pero en la actualidad no solo no ha bajado sino que parece que se ha estancado. Por lo tanto, el integrar más transistores en un chip implica que el coste es mucho mayor, algo que parece que está impulsando esta heterogeneidad en la fabricación de chips ya que de esta manera no es necesario desarrollar nodos más pequeños. De hecho, a veces no es necesario trabajar con silicio para ello, pues utilizar variantes de arseniuro de galio o germanio de silicio dan mejor resultado.

Esto significa que el que ahora los fabricantes estén optando por procesadores heterogéneos tiene que ver con los costes de fabricación y con la no necesidad de utilizar litografías más pequeñas, aprovechando por su puesto al mismo tiempo las ventajas que este tipo de arquitectura ofrece.

Por otro lado, según Geada habrá silicios especializados para hacer frente a las necesidades específicas, como el 5G de onda milimétrica que ahora está en boca de todos. El hecho es que según sus palabras, no se necesita el alto coste de un nodo de litografía diminuta para lograr cubrir muchas de las necesidades que tiene la tecnología de hoy en día.

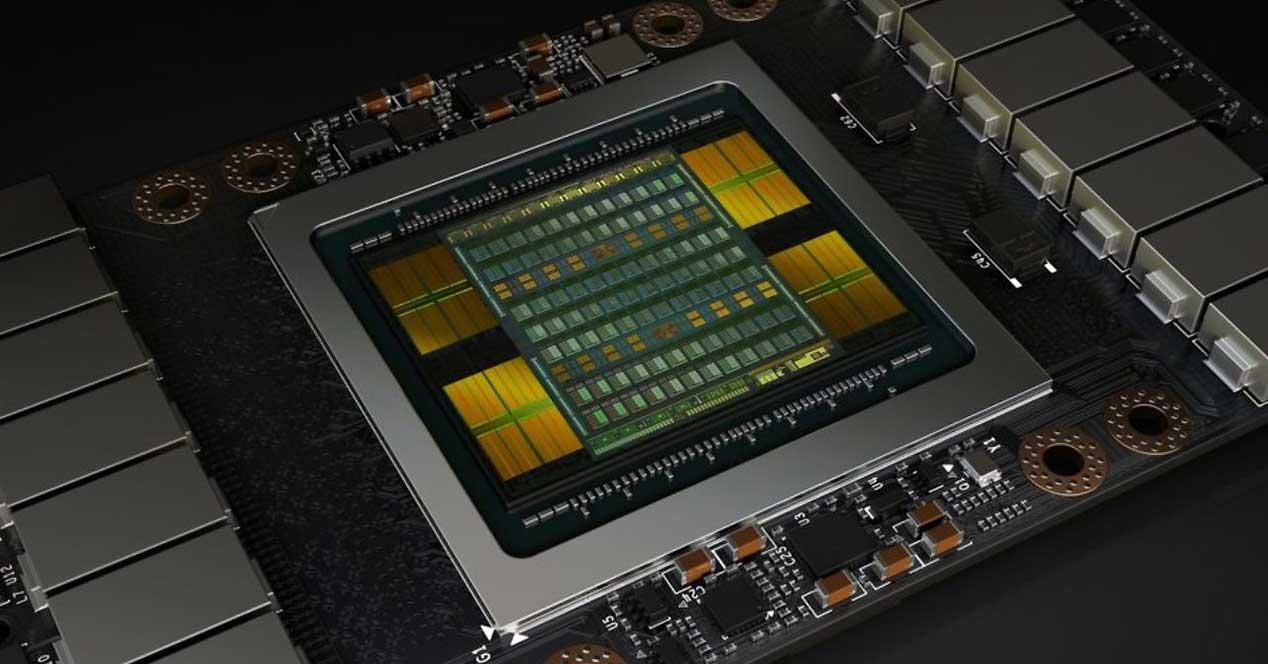

Procesadores de varios die y a 3 nm

Básicamente, cada subsistema se especializa en las cosas que hace bien. Por lo tanto, según Geada los 3 nm son ideales para la densidad de cálculo y potencia que se requiere en los procesadores modernos de hoy en día. Se puede incorporar una gran cantidad de potencia de cálculo localizada utilizando muchísimos transistores (los que permite este nodo tan diminuto), pero es mucho más eficiente si se crea un procesador con varios die, cada uno especializado en una cosa. Eficiente, al menos, en términos de coste.

Por este motivo varios fabricantes están ideando sistemas que ya no solo tienen un die, sino que están apilados para propósitos particulares. Ahora hay todo un ecosistema en torno a la memoria de gran ancho de banda, la cual están adaptando porque ya no pueden darse el lujo de instalarla fuera del propio die, algo que aumenta su latencia.

La velocidad perdida por culpa de las distancias de los componentes siempre ha sido una preocupación para los ingenieros. El rendimiento, en muchos aspectos, está limitado por el tamaño físico, y hoy en día se está volviendo un quebradero de cabeza por los requisitos de potencia y rendimiento que tienen hoy en día los sistemas que requiere la tecnología. Por lo tanto, siempre que sea posible, toda esta infraestructura se migrará hacia dentro, lo más cercana posible al procesador. Por ello, se están empezando a ver procesadores mucho más complicados donde se integra todo en uno a través de algún tipo de técnica 3D-IC.

¿Y qué pasa con los chiplets?

Durante un tiempo se ha hablado de los chiplets como una solución a todos los problemas actuales en cuanto a la reducción de los nodos de fabricación. Según Geada, todavía no estamos en ese punto porque queda muchísimo por desarrollar para que sea factible el utilizarlo en los productos cotidianos. En la práctica, el simple hecho de colocar más transistores en un área física más pequeña ha traído consigo una serie de consecuencias no deseadas.

Uno de ellos es la caída de voltaje causada por el intercambio de información entre dos componentes. Cuantos más hay, más acusada es esta caída, así que el incorporar cada vez más transistores y como cada vez el voltaje es más bajo, obliga a utilizar mayores intensidades de corriente para compensar. Y, dado que las fuentes de alimentación son capaces de suministrar una cantidad finita de intensidad de corriente, esto en el futuro puede llegar a ser un problema.

Tan pronto como se migró a FinFET esta historia dejó de tener sentido técnico porque los componentes fueron «ahogados» por un tercer factor, que es el efecto de otras partes del sistema en la conmutación interna de área local. El problema sigue estando, pero ahora es más complicado de analizar.

Integrar la memoria en el procesador, ¿genera problemas?

En pos de reducir la latencia y mejorar la eficiencia, últimamente se tiende mucho a acercar la memoria del sistema lo más posible al procesador, hasta el punto de que potencialmente se habla de integrar el procesador en la memoria y no al revés. Dado que la memoria es bastante sensible al calor, esto potencialmente puede llegar a ser un problema en nodos de fabricación modernos.

Según Geada, los ingenieros tienen que simular toda la física de un componente al mismo tiempo cuando lo diseñan, y necesitan técnicas con suficiente rendimiento para analizar suficientes modos de operación e interacciones para determinar si el sistema realmente funcionará como se espera. Definitivamente, hay un efecto térmico y hay que analizarlo, pero no solo por el calor que genera, sino por el estrés térmico consecuencia de ello.