El Custom Express Link o CXL es uno de los protocolos de comunicación entre periféricos que es una extensión del PCI Express, pero añade coherencia con la memoria principal. Su versión 2.0 fue presentada recientemente y es por ello que os hacemos un resumen de este protocolo y que novedades aporta.

Durante años se ha perseguido la creación de una interconexión que permitiese el acceso coherente a la RAM no solamente a nivel de los múltiples núcleos de un procesador, sino también por parte del resto de componentes que acompañan a este en el PC incluyendo los periféricos de E/S.

El enésimo estándar con el que persiguen conseguir este objetivo es el llamado CXL o Compute Express Link, el cual ha sido adoptado por casi todos los actores principales de la industria, lo que indica que nos estamos moviendo hacía su implementación de manera masiva.

¿Qué tiene de especial el CXL?

Han habido varios intentos para crear una interfaz coherente de comunicación para los periféricos ha existido desde hace años y se han propuesto varios estándares.

Por ejemplo AMD hace unos años promociono lo que ellos llamaron HSA pero cayo en el olvido debido a la falta de apoyo por parte de Intel, en el caso del CXL tenemos un estándar que tiene el apoyo tanto de Intel como de AMD, lo que asegura que todos los procesadores y placas base del futuro van a tener soporte.

Pero la clave es que CXL no es un protocolo nuevo sino que es una mejora sobre el PCI Express, no es más que darle coherencia de memoria, o también llamada coherencia de caché, con el procesador del sistema a todos los dispositivos que se encuentran conectados al puerto PCI Express y lo veremos por primera vez en la versión 5.0 del protocolo.

PCI Express Bridge

Todos los dispositivos que utilizan el puerto PCIe para conectarse a nuestro PC tienen las líneas conectadas a un dispositivo llamado PCI Express Bridge, el cual es la interfaz de E/S que sirve de puente entre el Southbridge o gestor de los periféricos de E/S y los diferentes dispositivos PCI Express.

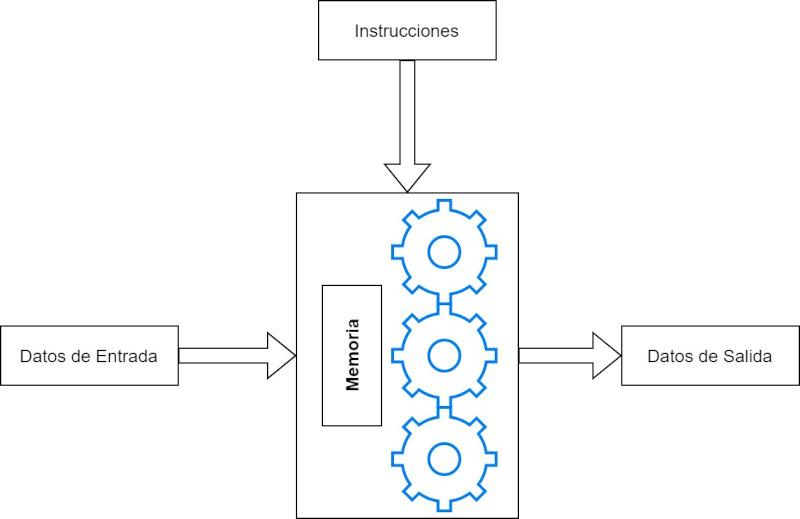

El problema a la hora de comunicar el procesador con los diferentes periféricos es que por lo general cada uno de elementos de E/S tienen su propio espacio de direccionamiento en la memoria y se necesita una pieza de hardware intermedia para traducir los envíos y recepciones de datos desde y hacia los periféricos.

Este es el motivo por el cual en un SoC cuando se quiere que la GPU tenga acceso al espacio coherente de la CPU esta no es conectada como un periférico a través de los puertos PCi Express sino que es conectada de manera directa al Southbridge.

Un protocolo de comunicación para la era de los aceleradores

Los aceleradores son procesadores de apoyo que realizan una tarea o un conjunto de tareas concretas de mejor manera que un procesador, ya sea consumiendo mucho menos y/o realizando dichas tareas en menos tiempo. Es por ello que los procesadores en vez de hacer ciertas tareas lo que hacen es pedirles a los aceleradores que las hagan y devuelvan el resultado o una confirmación que el acelerador ha realizado el trabajo el resultado del mismo.

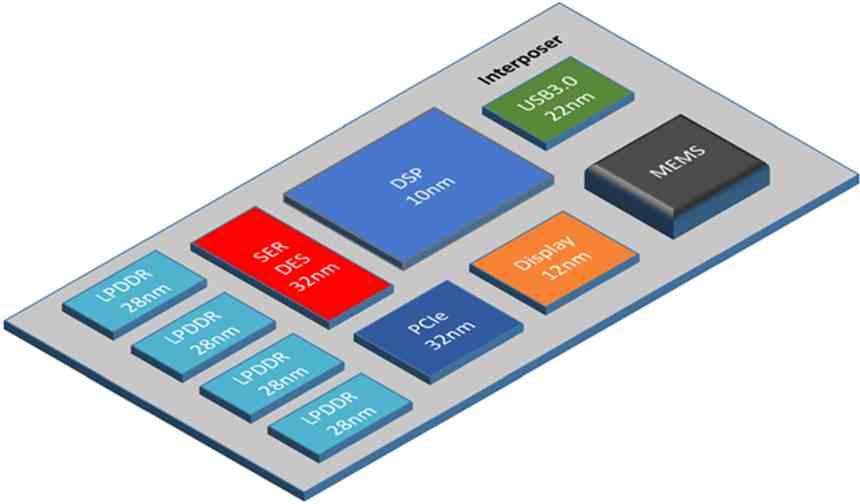

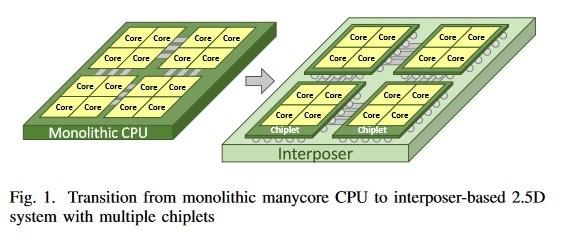

Donde esto es sumamente importante es de cara a configuraciones MCM heterogéneas o configuraciones con chiplets que combinan en un mismo interposer varios procesadores de diferente naturaleza pero compartiendo el mismo pozo de memoria física, lo que va a permitir integrar aceleradores adicionales sin cambiar el resto de los componentes del MCM.

Pero de cara a los Data Centers del futuro vamos a ver varios de estos MCM conectados entre sí de manera cruzada formando un solo sistema, es en este punto donde es importante que todos los dispositivos de E/S se puedan conectar entre sí.

Lo que tenemos ahora en el caso de protocolos como el Infinity Fabric de AMD es que podemos comunicar varios núcleos de la CPU entre sí, pero necesitan que el acceso a los periféricos este centralizado para que todas compartan el mismo acceso ya que si cada procesador tuviese su interfaz de E/S lo tendría sumamente difícil para utilizar los periféricos de E/S asignados a otro procesador en el MCM.

El CXL lo que permite es que los aceleradores y periféricos de E/S situados en diferentes chiplets del mismo procesador se puedan comunicar entre si y no solo con los elementos dentro de un mismo chiplet sino entre varios chiplets de manera transparente, permitiendo que todos la misma visión de la memoria del sistema.

Mientras que el CXL 1.1 va a ser integrado en algunas implementaciones del PCI Express 5.0, siendo el Intel Xeon Sapphire Rapids el primero en integrarlo, aún no tenemos fecha para la versión 2.0 del protocolo pero si que tenemos información sobre las grandes novedades que a

Switches en CXL 2.0

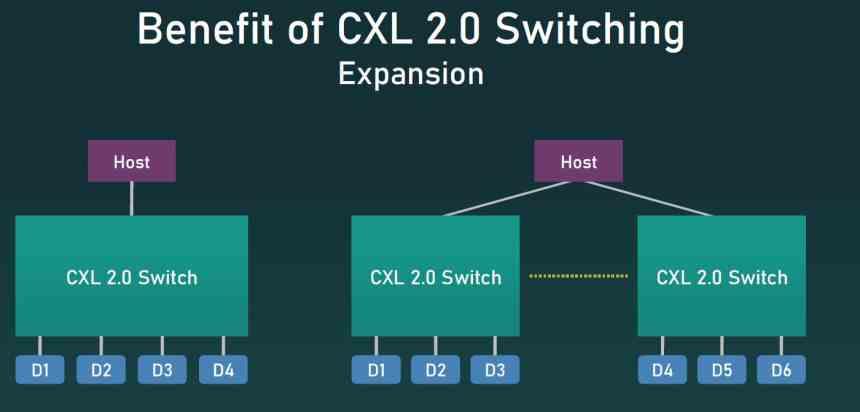

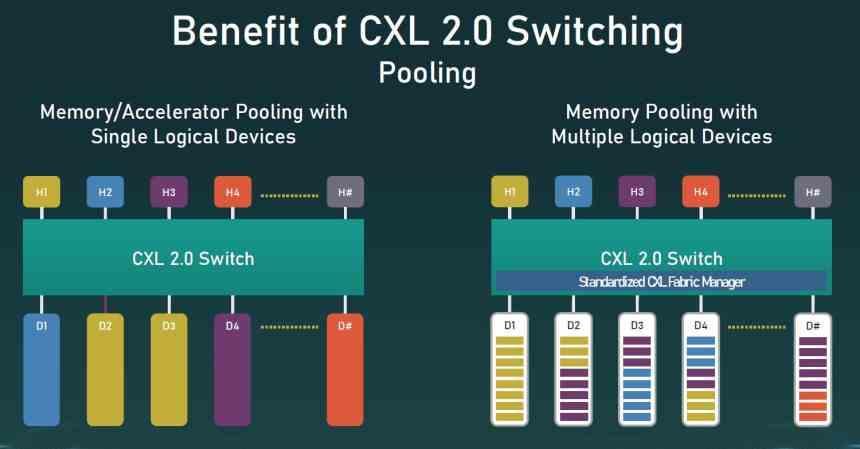

Una de las novedades que se han añadido en la versión 2.0 del CXL son los llamados CXL Switches, los cuales tienen la misma aplicación que los switches del PCI Express.

Los Switches simplemente nos permiten asignar los puertos PCIe del sistema a diferentes dispositivos de E/S, por lo que podemos asignar controlador PCIe de 24 líneas de la siguiente manera: 16 puertos para la gráfica, 4 para el chipset y 4 para un NVMe.

Pero también son importantes para comunicar los periféricos entre si de manera directa, la trampa de los switches del PCIe es que las líneas PCIe no solamente se pueden utilizar para comunicar la CPU con los periféricos sino también entre sí, por ejemplo podemos hacer que la gráfica acceda a un disco sólido conectado a otro puerto PCIe.

Esta capacidad no se encontraba en la versión 1.1 del protocolo CXL pero si en la versión 2.0.

Memoria Persistente en CXL 2.0

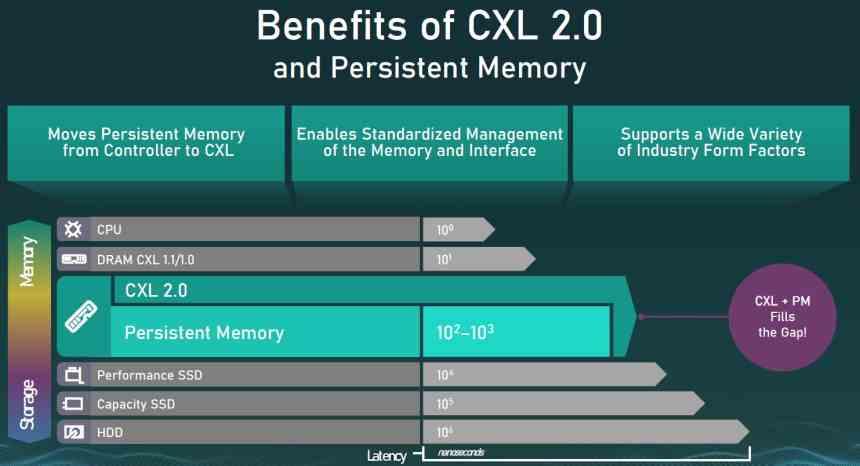

Otro de los elementos más importantes dentro del mundo de los Data Centers es la memoria persistente estamos hablando de memoria que sería casi tan rápida como la DRAM pero que almacenaría los datos de memoria persistente como la NAND Flash.

Un ejemplo de este tipo de memoria sería la 3D Xpoint que fue vendida hasta hace relativamente poco por Intel bajo el nombre Optane. Con el uso de interfaces CXL para acceder a este tipo de memorias se hace posible que varios procesadores puedan acceder a este tipo de memoria en vez de hacerlo uno solo.

Cifrado y Descifrado en CXL 2,0

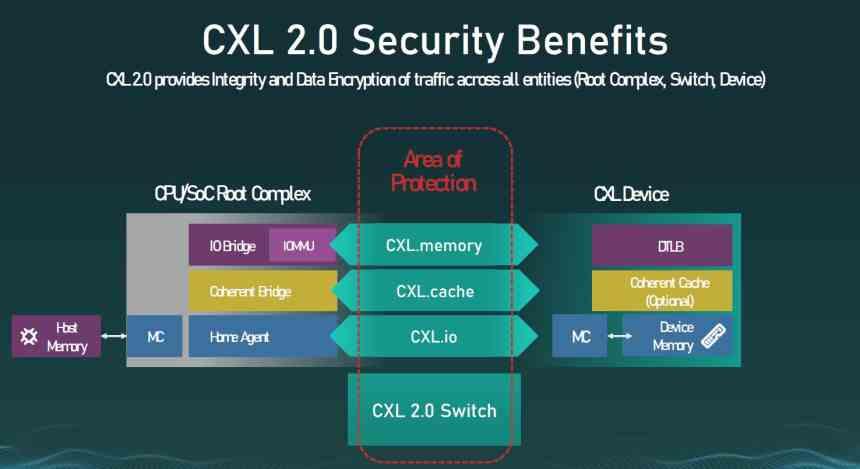

Otra de las novedades en el protocolo CXL 2.0 es el añadido de hardware para el cifrado y descifrado de datos en las interfaces CXL.

Estos aceleradores toman los datos de entrada y salida y acaban aplicando un algoritmo a tiempo real para decodificar los datos al vuelo, lo que permite que solamente el hardware con la rutina de descifrado adecuada pueda cifrar y descifrar los datos.

Esto no solamente se puede utilizar para almacenar datos sino también para aplicar algoritmos a través de estos aceleradores de compresión y/o descompresión de datos con tal de aumentar la cantidad de datos efectivos que son enviados a través del bus.