La cacé vertical fue una de las grandes novedades arquitecturales que AMD presento el año pasado y que ha introducido en sus CPU Ryzen 5800X3D para escritorio y Milán-X para servidores. No obstante, hasta el momento era una incógnita en muchos puntos como la comunicación con el procesador. Pues bien, han dado nuevos detalles del funcionamiento de la V-Cache en el ISSCC 2022, veamos cuáles son.

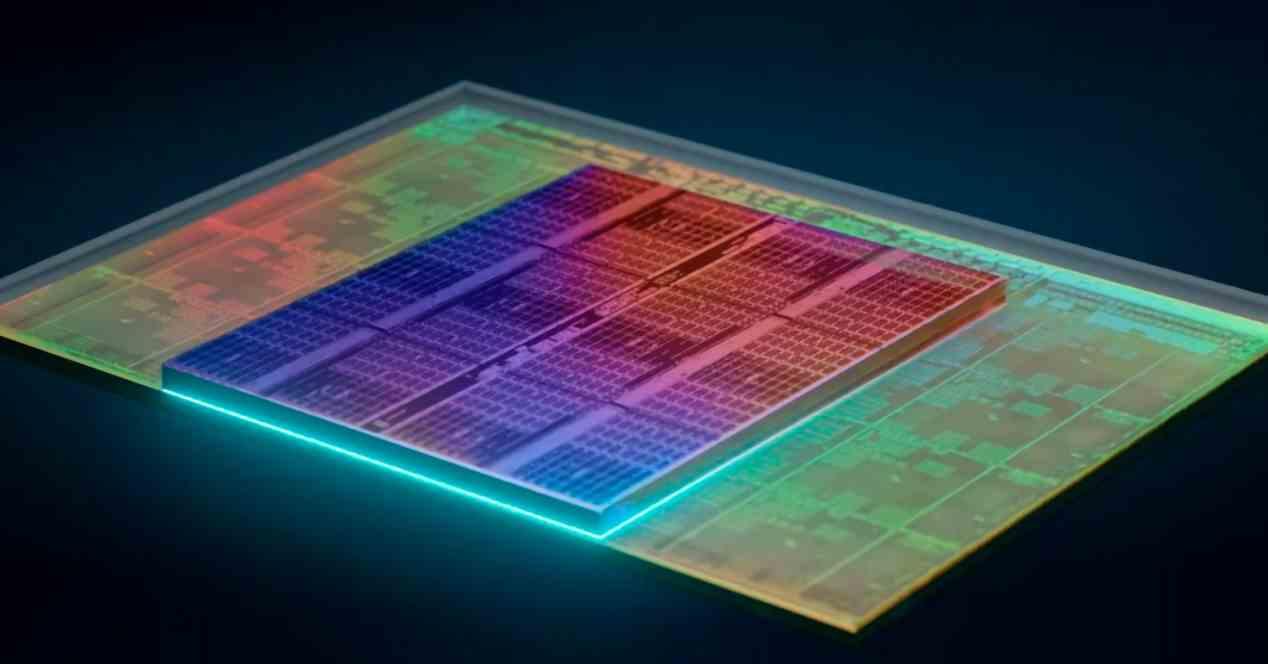

A medida que el abismo entre los procesadores y la memoria es cada vez más grande, los arquitectos de nuevos procesadores han de buscar la forma de que esto no se convierta en un cuello de botella en el rendimiento. ¿La solución de AMD? Aumentar la caché L3 de su procesadores Zen 3, pero de manera en que el tamaño del procesador no aumente. ¿Cómo? Creando un chip aparte, apilarlo sobre el procesador y desarrollar un sistema de comunicación para intercomunicar verticalmente a ambos que resulte lo suficientemente rápido como para que pueda funcionar como una caché. El objetivo de ello es fácil, el rendimiento de una instrucción depende lo que tarde en encontrar los datos y los encontrará antes en la caché que no en la memoria principal. Por desgracia el espacio para memoria dentro de un procesador es limitado.

Nuevos detalles de la V-Cache de AMD en el ISSCC 2022

Aprovechando la celebración de la ya clásica conferencia acerca de arquitecturas de hardware en la que las diferentes compañías hablan de sus logros e hitos en el pasado año. AMD ha aprovechado el evento dea la ISSCC en 2022 para dar nuevos detalles de su V-Cache. Los cuales desconocíamos hasta el momento y hacen referencia a la forma en la que la SRAM de comunica verticalmente con el CCD Chiplet Zen 3, pero antes de ello hemos de hacer un repaso a la topología de comunicación,

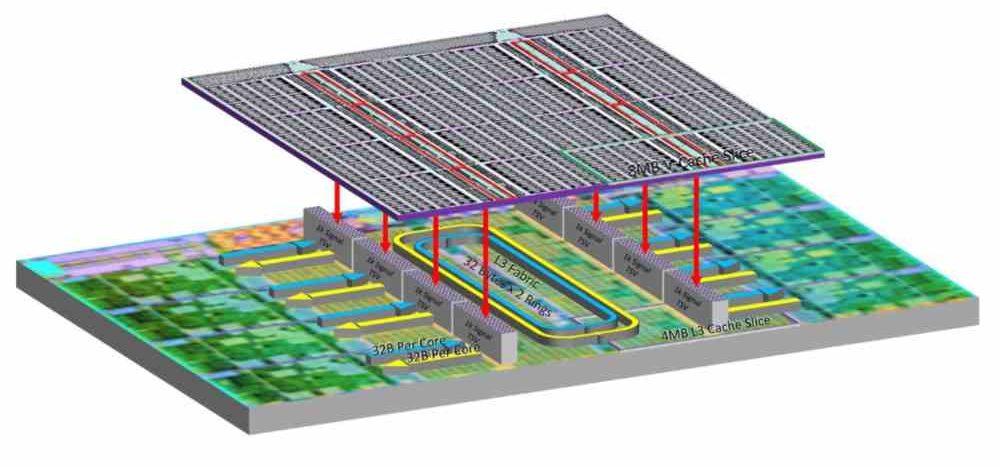

Mientras que un CCD Chiplet en Zen 2 hace uso de un crossbar para intercomunicar los 4 núcleos entre sí, el aumento a 8 núcleos en Zen 3 obligo a AMD a hacer uso de una topología en anillo para la comunicación entre los diferentes cores entre sí y con la caché compartida de último nivel, la cual es la de tercer nivel.

Pues bien, para comunicarse con la V-Cache, cada núcleo tiene un total de 1024 pines en vertical haciendo uso de intercomunicaciones TSV, esto significa que por cada ciclo se transmiten 8.192 bits con un ancho de banda total de 2 TB/s en modo Full Dúplex y, por tanto, en ambas direcciones al mismo tiempo. Lo que significa que la velocidad de reloj de la interfaz de comunicación es de 0,977 GHz. Todo ello a través de un enlace de cobre donde no es necesaria la soldadura.

Nuevas celdas de SRAM utilizadas

En cuanto al tipo de SRAM utilizada en la V-Cache, esta es diferente a la utilizada en el CCD Chiplet. Dado que AMD para la SRAM en la V-Cache hace uso de celdas de memoria de alta densidad (HD)) en lugar de las celdas de bits de alta corriente (HC). Lo que da cómo resultado un ahorro en energía por transferencia de datos del 14% y es un 24% en cuanto a tamaño respecto a la capacidad.

Más allá de Zen 3D

La presentación sobre la V-Cache en la ISSCC 2022 nos ha dejado bien clara una cosa: vamos a ver una versión de Zen 4 con V-Cache. Aunque no ha sido anunciada de manera oficial, sí que sabemos que la topología interna de comunicación será la misma que su antecesor y, por tanto, no habrá problemas en crear una versión con caché vertical.

Ya hablando de cosas más oscuras, se rumorea que la Infinity Cache en RDNA 3 irá en un chip aparte junto al controlador de memoria en forma de memoria apilada, lo que coincide en descripción a lo que es la V-Cache. Al menos si hacemos caso a las patentes de la propia AMD. Ahora que sabemos que la V-Cache dispone de una interfaz que escala con la cantidad de clientes ya sabemos cómo puede escala en sistemas complejos.