Debido al aumento de costes traídos con las nuevas tecnologías de fabricación de chips, se hace necesario separar un chip en varios distintos. Lo cual permite utilizar fabricaciones más baratas en ciertas partes del procesador. Sin embargo, dichas interfaces han de estar comunicadas entre sí y hasta hace relativamente poco no existía un estándar para ello. Hace unas semanas se presentó el UCIe o Universal Chiplet Interconnect Express para ello. Este permitirá que varios chips distintos existan en un mismo empaquetado. Pues bien, Intel ha dejado caer nueva información sobre el estándar.

El UCIe es un estándar que se presentó el pasado mes de marzo. Se trata de una interfaz para intercomunicar lo que llamamos chiplets entre sí y que tiene el apoyo de empresas como Intel, TSMC, ARM, Qualcomm, Samsung y Microsoft. Por lo que estamos ante un estándar que veremos en muchos sistemas en el futuro. Pues bien, hemos podido saber nuevos detalles del mismo

¿Qué es el UCIe?

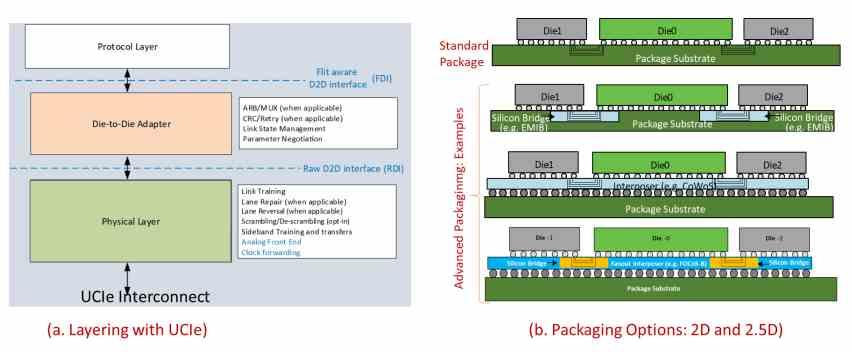

Para entender lo que esta interfaz hemos de pensar que se trata de comportamiento muy similar al PCI Express. En el caso que nos ocupa, la diferencia es que en este caso no es para conectar tarjetas gráficas, sino chips entre sí encima de un mismo sustrato o interposer. Permitiendo con ello que diferentes chips con distintas funciones y naturaleza se encuentren bajo el mismo encapsulado. Hasta el momento el único procesador de esta naturaleza eran los Ryzen de AMD, los cuales usan la interfaz Infinity Fabric. La cual si bien es una versión con soporte para coherencia de memoria del HyperTransport, no deja de ser propietaria de AMD. Por lo que hacía falta un estándar que permitiese chiplets con tecnologías de varias marcas y no de una sola.

Pues bien, Intel ha dado nueva información sobre la primera generación de este estándar. La cual tendrá la capacidad de transmitir entre 12 y 16 gigabits por segundo de información por pin de contacto. Por lo que hablamos por el momento de anchos de banda equivalentes al PCI Express 4.0. Sin embargo, con el uso de un cableado mucho más corto. Lo que supone una reducción importante en el consumo energético, entre 10 y 20 veces. Sin embargo, esta no es la principal ventaja del nuevo estándar UCIe

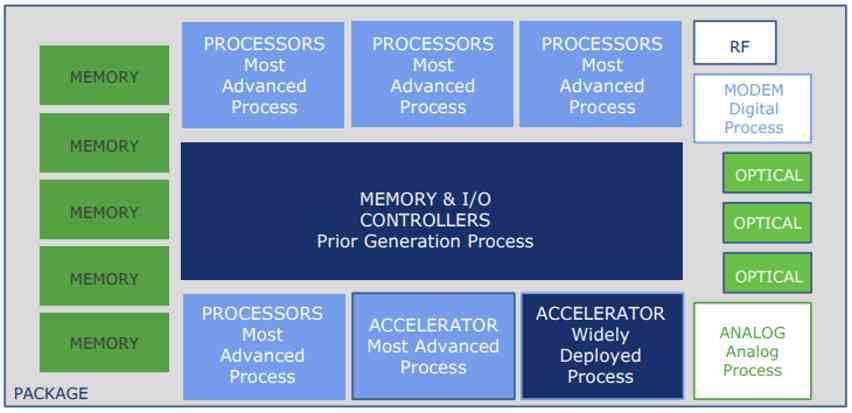

La otra ventaja es que será posible colocar bajo un mismo sustrato común chips de marcas distintas. Como por ejemplo un procesador de Intel y una gráfica de NVIDIA. Para tenerlo todo bajo el mismo encapsulado. Aunque no será la norma, sí que abre la capacidad para procesadores a medida para ciertas soluciones concretas. Además, el UCIe no es una solución centrada en un solo fabricante de chips. Ya que es compatible con soluciones de Intel EMIB y TSMC CoWoS.

Soporte para mecanismos de memoria coherente

Además, el UCIe tendrá soporte para el Compute Express Link y el Coherent Hub Interface. Lo cual permitirá la creación de sistemas heterogéneos, pero totalmente coherentes en cuanto a memoria. Esto es crucial, puesto que permitirá el uso de un único pozo de memoria RAM para todo el sistema. Lo cual es frecuente en los sistemas empotrados a día de hoy y especialmente es soluciones de bajo coste y de poco consumo energético donde los diferentes componentes comparten el mismo pozo de memoria.