La confirmación de que habrá modelos de los Intel Xeon Sapphire Rapids con memoria HBM2e con tal de acelerar la ejecución de algoritmos de aprendizaje profundo significa el uso por primera vez una CPU x86 de este tipo de memoria. En cambio, AMD ha optado por la V-Cache como forma de aumentar su rendimiento. ¿Por qué AMD no utiliza la HBM2e en sus CPU?

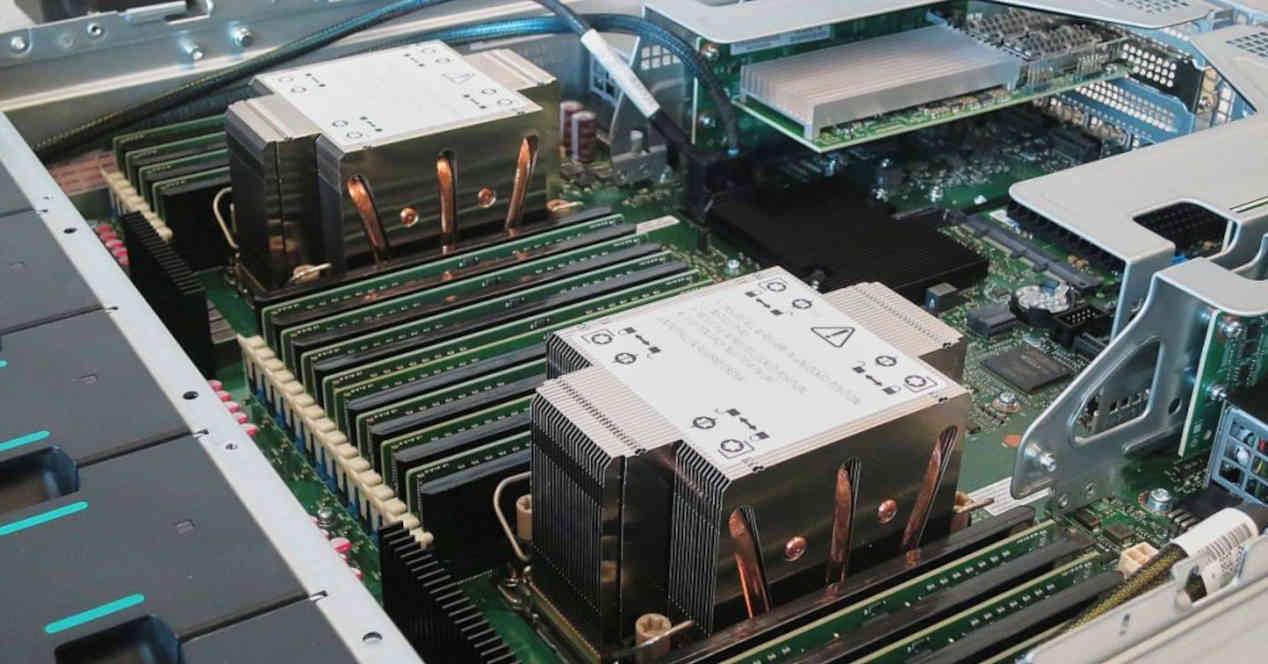

No es ningún secreto que uno de los puntos más importantes de cara al rendimiento en una CPU es su interacción con la memoria RAM, aunque bien es cierto que no todos los procesos que se ejecutan tienen los mismos requisitos en cuanto a necesidades de ancho de banda y latencia, de cara al mercado de la computación de alto rendimiento sí que es importante.

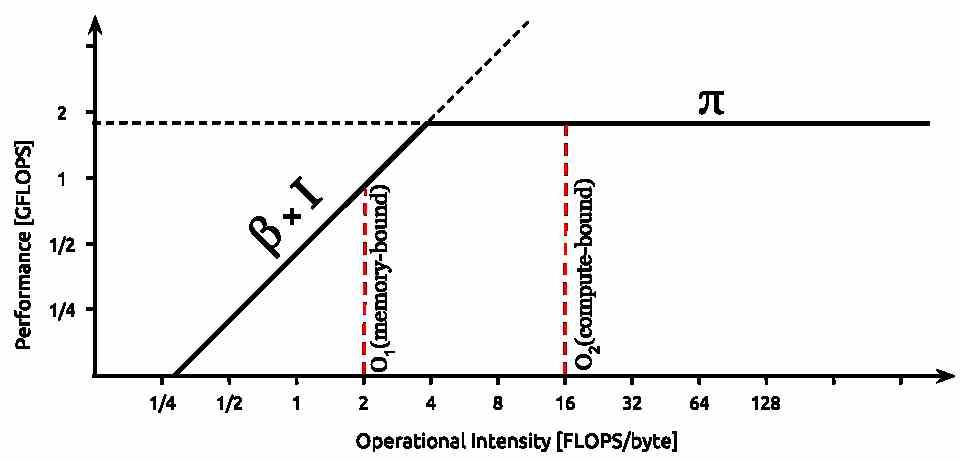

El modelo Roofline

Para entender la relación entre el uso de la memoria y los diferentes algoritmos hemos de hablar del llamado modelo Roofline y se basa en medir la intensidad aritmética de un algoritmo. La cual de mide dividiendo la cantidad de operaciones en coma flotante necesarias para ejecutarlo por la cantidad bytes de ancho de banda de la memoria RAM.

Es aquí donde entramos en las dos soluciones posibles para los algoritmos que requieren un alta intensidad aritmética y por tanto un alto ancho de banda, las cuales son:

- El uso de memoria RAM de alto ancho de banda, siendo la HBM2E la más indicada por su baja latencia y alto ancho de banda. Esta solución es utilizada por la CPU Fujitsu A64FX basada en la ISA ARM, así como el futuro Xeon Sapphire Rapids de Intel.

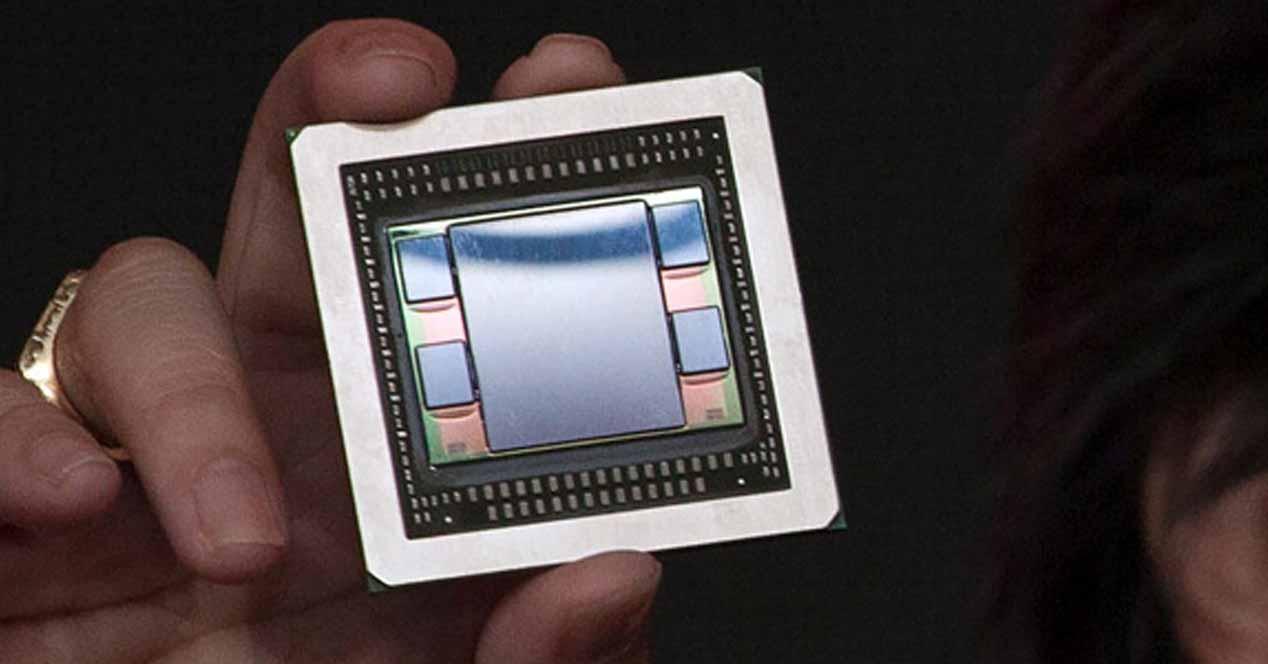

- El aumento considerable de la caché de último nivel, la cual es la más cercana a la RAM y la que tiene mayor tamaño. En el caso de AMD esto se consigue colocando un chip de SRAM a través de vías de silicio o TSV al que han bautizado como V-Cache.

El objetivo por tanto no es más que el flujo de datos se mantenga lo suficientemente alto para así sacar el máximo rendimiento posible.

¿Por qué no hay CPU de AMD que usen HBM2E?

Habréis observado que no existe ningún procesador EPYC ni Threadripper que haga uso de memoria HBM2E en el mapa de ruta, esto es debido a que AMD ha decidido optar por la V-Cache con tal de otorgarle una mayor intensidad aritmética a ciertos algoritmos que se suelen ejecutar en el mundo de la computación de alto rendimiento y es muy probable que veamos futuras CPU no con una sola pila de memoria SRAM como V-Cache sino varias.

No obstante, ambas ideas se pueden combinar entre sí, por un lado, una estructura 3DIC y por el otro una 2.5DIC con un interposer por debajo. Por lo que no podemos descartar que AMD haga uso de memoria HBM2E en el futuro a nivel de servidor, pero no lo podemos asegurar desde el momento en que no se encuentra en su roadmap.

El hecho de crear una CPU que haga uso de un interposer encarece enormemente su fabricación, ya que son pocos los clientes que utilizan estas soluciones especializadas. Además, que el añadir más pasos en el proceso de fabricación encarece todavía más los costes y si le añadimos la cara memoria HBM2E pues al final resulta mucho más barata la solución de AMD. En todo caso, creemos que Intel hará lo mismo en sus futuras CPU, ya que tiene la tecnología Foveros para ello.