Los que nos seguís a diario seguro que estaréis viviendo una especie de dejavú y es lógico. Hace meses ya dimos el primer rumor acerca de la implementación por parte de AMD de una mejora en la llamada SMT. Hasta ahora tanto Intel como los de Lisa Su han mantenido el rato de dos hilos por núcleo, pero eso podría cambiar según las nuevas filtraciones con Zen 4.

Tal y como vimos en el artículo correspondiente y en base al rumor que por aquellos meses daba la vuelta al mundo, AMD podría estar trabajando en una mejora de su arquitectura para duplicar el número de hilos por cada núcleo físico.

Esto es algo que IBM ha llevado al extremo y que Intel ni siquiera se plantea a día de hoy, y como en aquel entonces, nuevos rumores y filtraciones apuntan hacia esta mejora, la cual llegaría en Zen 4.

Mejor escalabilidad por SMT para maximizar el rendimiento por hilo

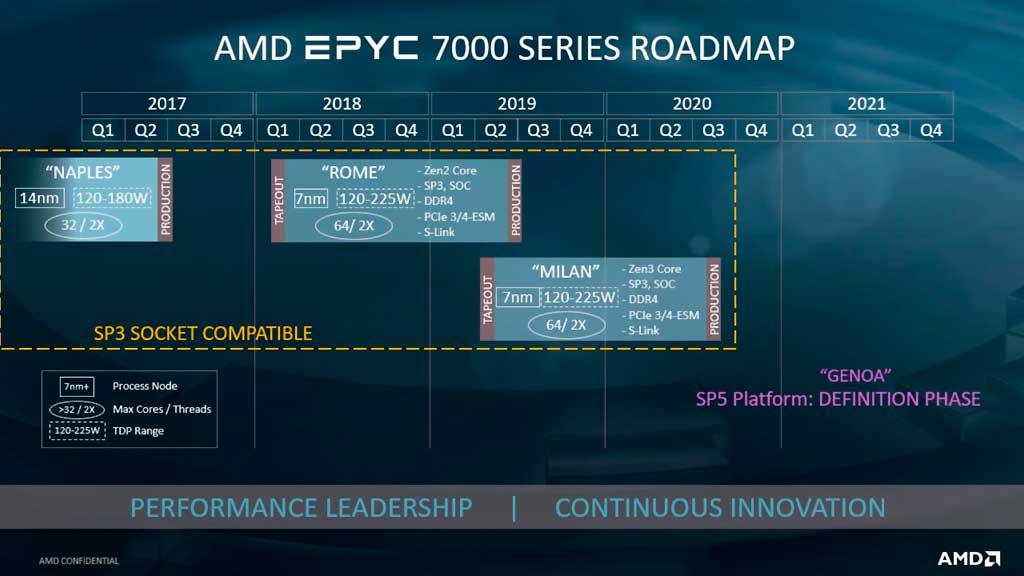

Hoy sabemos de donde salieron aquellos rumores sobre la implementación de esta posible mejora en la arquitectura Zen. Al parecer, una vieja hoja de ruta interna de AMD especifica varios detalles interesantes que ahora sabemos que no serán así, pero que al mismo tiempo muestran algunas mejoras que sí sabemos que terminarán llegando.

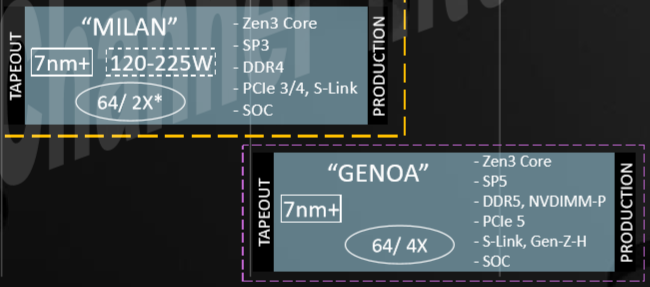

Por aquel entonces, como muestra la diapositiva, se habló de Zen 3 como posible arquitectura que incluyese dicha mejora y aunque no se especificó nada más, podemos entender el porqué de dichas afirmaciones.

La diapositiva muestra al menos dos errores, Zen 3 y 7 nm+. Ya sabemos que Genoa como arquitectura principal llegará bajo Zen 4 a 5 nm con TSMC en el socket SP5 con DDR5 y PCIe 5 allá por 2022. La diapositiva tiene que ser por tanto bastante más antigua y seguramente AMD no pensaba por aquel entonces que TSMC pudiese apretar tanto el acelerador al igual que su equipo de ingenieros.

Se mantendrían los 64 núcleos, pero con cuatro hilos por cada uno de ellos (SMT 4)

No está claro si AMD mantendrá el número de núcleos máximos en 64 a pesar de contar con los 5 nm, los cuales suponen otro salto en densidad y frecuencias. Podría tener sentido visto desde el punto de vista de la eficiencia, y es que ni Intel ni AMD han dado al salto a SMT 4 precisamente por el derroche de energía que se necesita para hacerlo funcionar a altas frecuencias.

Mantener el número de núcleos y doblar el número de hilos manteniendo el consumo puede ser otra técnica perfectamente factible a la espera que una nueva bajada del proceso litográfico, ya que no olvidemos que tanto DDR5 como PCIe 5.0 requerirán un mayor número de pines en el socket.

Igualmente, coged esta información con pinzas como en aquella ocasión, ya que solo podemos estar seguros de que Zen 4 llegará en 5 nm en dicha fecha y coincidirá por tanto con el asentamiento de la DDR5 y PCIe 5.0, aparte de Gen-Z.

No olvidemos que al compartir arquitectura con los procesadores de escritorio, si SMT 4 llega a Genoa debería llegar también para el usuario común con los Ryzen 5000, algo que no tendría demasiado sentido, puesto que lo que necesita AMD es mayor frecuencia para competir con Intel en gaming, ya que en multinúcleo está un paso por delante.