Uno de los puntos más importantes a la hora de crear nuevos procesadores, no solo está en el diseño de nuevas unidades de cálculo, sino también de nuevas formas de empaquetado y de interconexión entre los diferentes elementos. Hace unos meses AMD habló de su V-Cache por primera vez, consistente en apilar una SRAM como LLC en un Zen 3. En el Hot Chips en AMD han dado nuevos detalles de su V-Cache.

Durante estos días se está celebrando el Hot Chips, un simposio donde varios de los fabricantes y diseñadores del sector del hardware presentan sus últimos avances tecnológicos. La diferencia del Hot Chips respecto a otros eventos es que no se trata de una conferencia comercial y por tanto no estamos en una feria, sino que se trata de un evento dirigido a ingenieros y a entusiastas del hardware donde se explican los últimos avances tecnológicos, cuál es su motivación y cómo funcionan. Como es el caso de la V-Caché de la que AMD ha dado nuevos detalles.

AMD da nuevos detalles de su V-Caché para los Zen 3

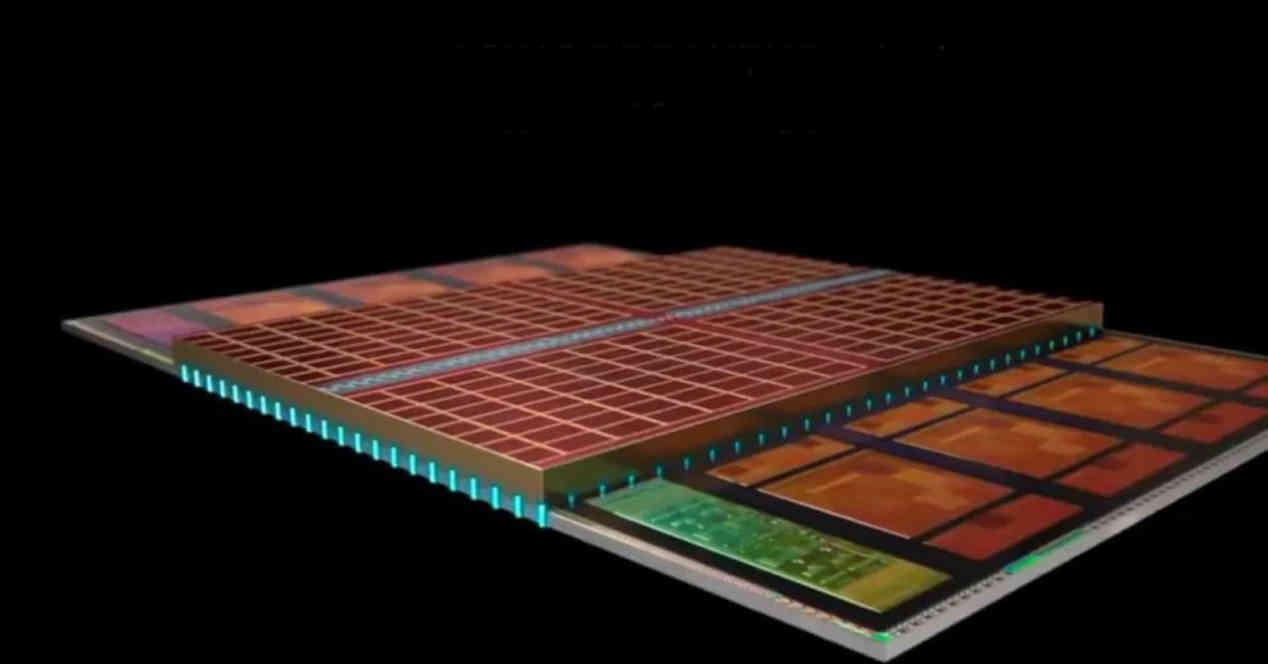

Hace unos meses, AMD nos sorprendió a todos con algo que no esperábamos. El añadido de un chip de memoria SRAM encima del Chiplet CCD de los Zen 3, sobre el que aprendimos que ya estaba diseñado para ello desde el principio. La idea no es otra que la de ampliar la capacidad de la caché L3 que es compartida por todos los núcleos Zen 3 dentro del chiplet CCD y con ello el rendimiento.

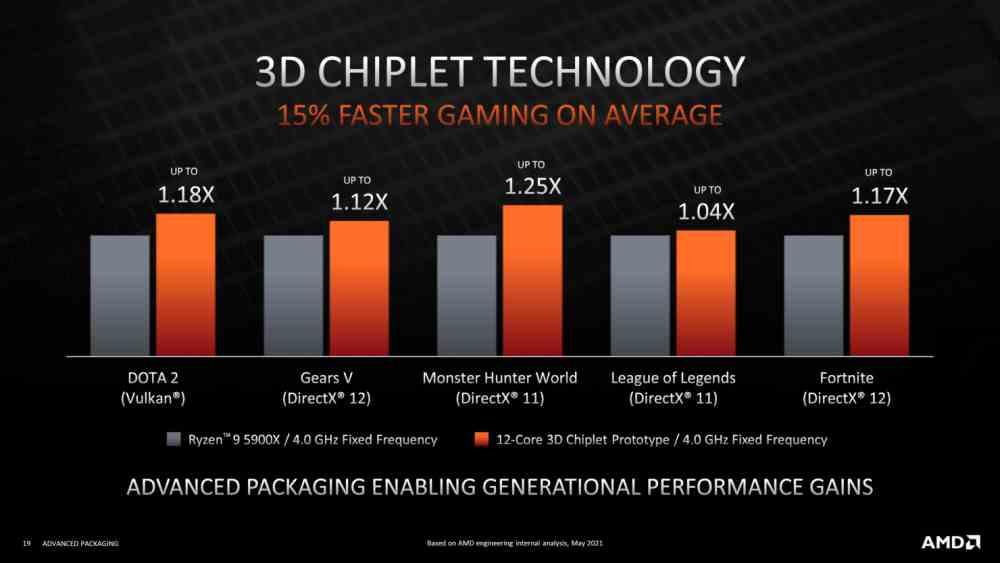

El motivo del aumento de rendimiento es muy simple, con ello la cantidad de datos que se encuentra en caché aumenta. Lo que hace que los accesos a la RAM para acceder a los datos se reduzcan al haber más datos en la caché de último nivel y con ello aumente el rendimiento hasta un 15% sin llegar a cambiar el resto del chip.

¿Cuál es la nueva información que nos ha dado AMD sobre su V-Cache? Pues la forma en la que lo han conseguido, y es que han utilizado varios microbumps para comunicar el módulo de SRAM con el CCD, mientras que el cableado son las clásicas vías a través de silicio o TSV. La interconexión en vertical del CCD Chiplet con la SRAM adicional se ha realizado con interconexión dialectrica-dialectrica con unión directa de cobre a cobre. Dicho tipo de interconexión ha sido desarrollada en conjunto con TSMC.

Los microbumps utilizados para la interconexión son de 9 micrómetros de tamaño, 10% más pequeños que los que Intel utilizó en Foveros para Lakefield. Se ha de tener en cuenta que la clave para las interconexiones 3D en vertical es la cantidad de interconexiones, ya que la estrategia para aumentar el ancho de banda entre las dos partes es no aumentar la velocidad de reloj de cada interconexión, sino la cantidad de las mismas con tal de mantener el consumo por la transmisión de datos lo más bajo posible.

La V-Caché solo es el principio nos avisa AMD

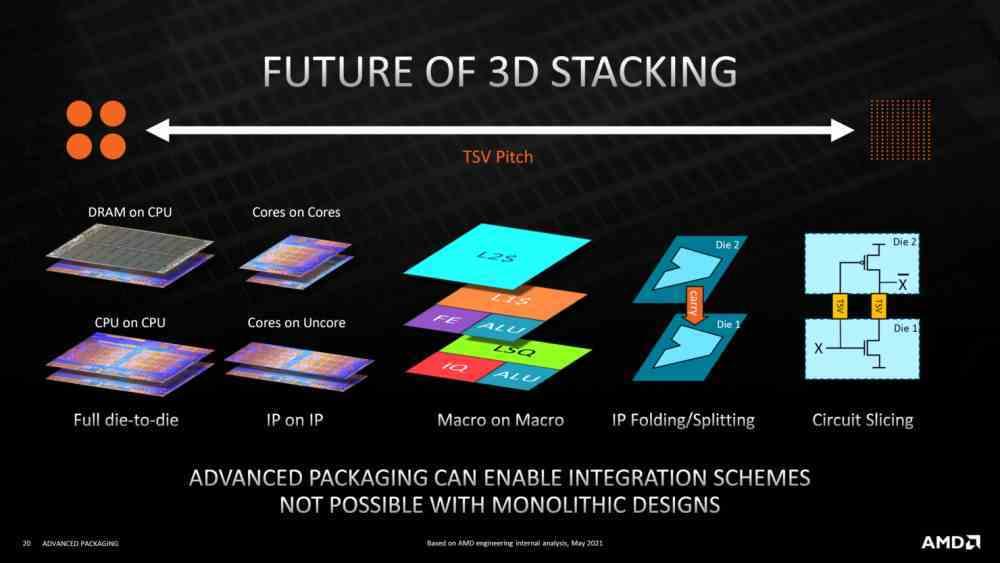

No es ningún secreto que el futuro pasa por la integración 3DIC de los chips, tanto de lógica como de memoria. La demostración de ello es que estamos viendo configuraciones no-monolíticas que son del tipo 3DIC o 2.5DIC en los diferentes diseños en desarrollo de los distintos fabricantes.

Por el momento tenemos solamente casos de memorias apiladas como la V-NAND o la HBM en sus diferentes sabores y pronto tendremos lógica y memoria. Pero en el futuro cercano es posible que veamos por parte de AMD configuraciones donde IOD y los Chiplets estén uno encima del otro. Lo cual no nos coge por sorpresa, es algo que se veía venir, la diferencia es que ahora AMD acaba de confirmar que está trabajando en ello.

Por lo que es más que posible que futuras CPU como por ejemplo las basadas en AMD Zen 4, no solamente puede que utilicen V-Caché sino que puede que las veamos en una configuración 3DIC o de otro tipo diferente no solo a los clásicos procesadores monolíticos de una sola pieza, sino también distinto a la configuración de chiplets 2.5DIC que hemos visto en los AMD Ryzen 3000 y Ryzen 5000.