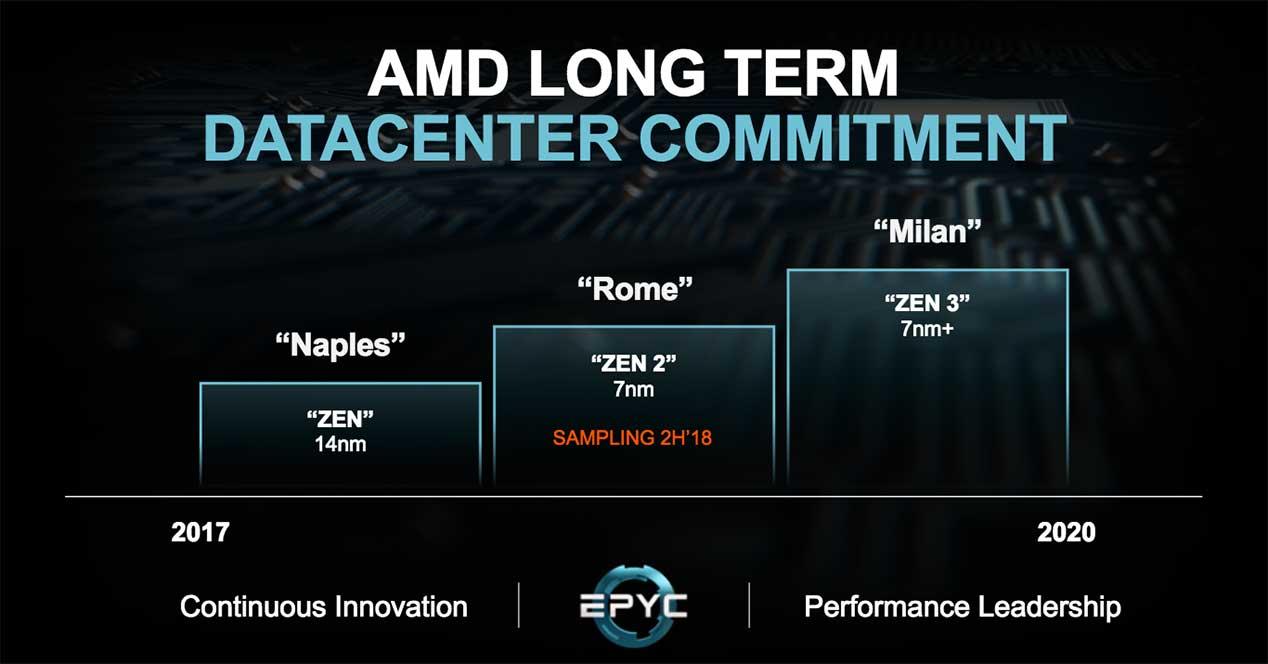

La semana pasada vimos como Intel presentaba su revolucionaria arquitectura Lakefield, donde mediante un diseño de varias capas lograba conectar tanto núcleos de alto rendimiento con bajo rendimiento y memoria RAM dentro de un mismo encapsulado. Hoy conocemos que AMD puede estar trabajando en un diseño en parte similar para sus nuevos procesadores EPYC Milán, los cuales llegarían con memoria HBM en forma de complemento a los dies.

AMD EPYC Milán sería una nueva revolución

Hace ya muchos meses hablamos largo y tendido sobre el futuro de AMD e Intel y si, efectivamente, la disposición MCM era el camino a seguir por ambos fabricantes. Hoy tenemos una respuesta tan clara como contundente y podríamos estar hablando de otro cambio de paradigma en apenas 5 años desde que MCM comenzase hasta que termine como concepto vetusto.

Centrándonos en AMD, al parecer los de Lisa Su están trabajando en un diseño MCM con hasta 15 dies/chiplets, donde ahora al parecer su construcción e implementación hará que cambie de nuevo su definición para pasar a llamarse Tile.

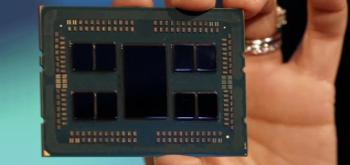

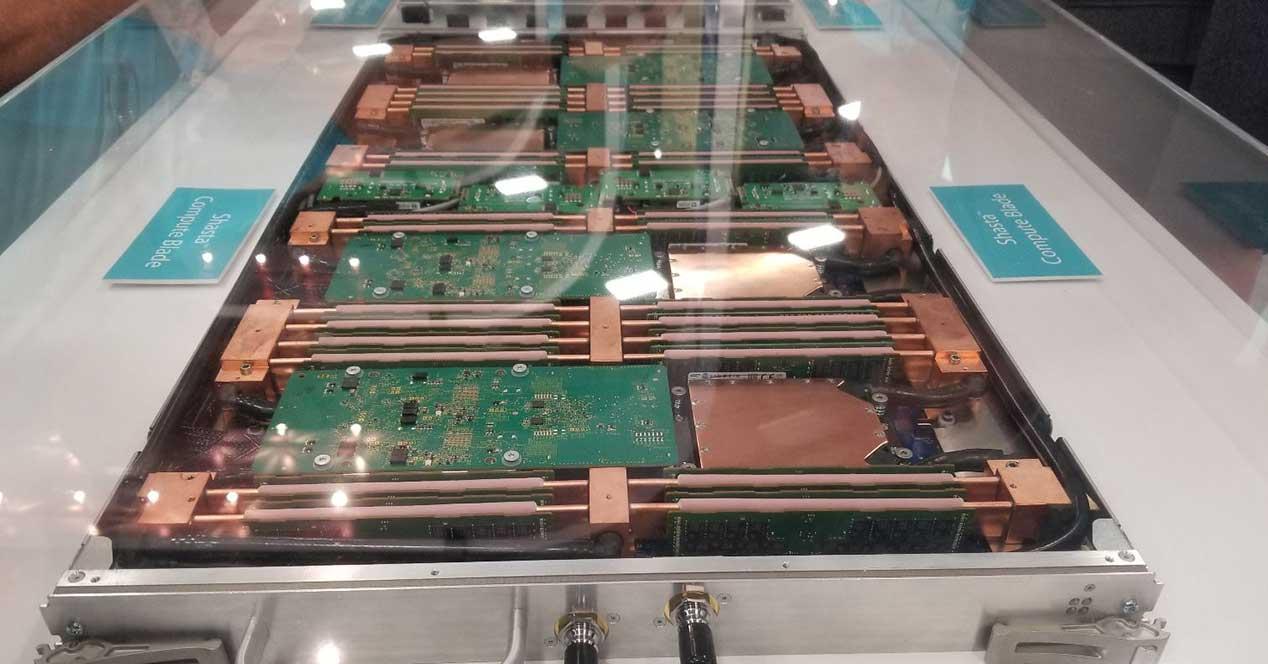

AMD EPYC Rome llegará en breve al mercado con 9 chiplets en total, un diseño MCM totalmente modular que engloba 8 Tile/chiplets donde se encuentran los núcleos y un die a modo de I/O que gestiona las entradas y salidas (entre otras cosas) de información hacia todos y cada uno de los 64 núcleos que portará la versión completa.

Lo que hoy se desvela es que AMD habría llegado al límite teórico dentro de la propia arquitectura, ya que no se podría agregar más núcleos en Zen 2 bajo los 7 nm de TSMC, es decir, no podrían agregarse más Chiplest/Tile en un supuesto procesador con mayor potencia.

El nuevo diseño para Milán rompería parcialmente esa barrera, agregando como hemos dicho hasta 15 Tiles, donde al parecer de nuevo AMD repetirá con un I/O central, lo que deja 14 de estos Tile/Chiplets disponibles, pero con una gran novedad entre ellos.

Los 8 canales de RAM DDR4 de Rome solo podrían trabajar con 10 chiplets

Otra de las limitaciones que AMD tiene con Rome es que el número máximo de núcleos disponibles para los 8 canales de RAM DDR4 se eleva hasta 80, lo que quiere decir que con la configuración actual y los 7 nm de TSMC solo podría trabajar con 10 chiplets simultáneamente.

Se desconoce si esto es debido a limitaciones propias del I/O o simplemente a diseño interno del PCB, donde las conexiones de Infinity Fabric tienen un gran peso dentro del chip. Pero entonces ¿por qué AMD estaría trabajando en un diseño con 15 Tile/Chiplets?

Según se filtra, el resto de chiplets estarían disponibles para implementar memoria HBM en el mismo encapsulado, lo cual es perfectamente razonable si se tiene problemas de conexión o ancho de banda con la lenta DDR4. Esto nos dejaría unas posibles configuraciones para Milán bastante novedosas: 8 Chiplets + 6 Tiles de HBM +1 I/O, o bien, 10 Chiplets + 4 Tiles HBM + 1 I/O.

La configuración más óptima sería la primera por simple arquitectura, el problema es que esto no supondría un estímulo para el mercado de servidores que anhelan más núcleos con mismo o menor consumo para aumentar su potencia.

La inclusión de HBM como una especie de caché intermedia, si el tamaño de la misma es óptimo, reduciría el acceso directo a la RAM, pudiendo reducir los tiempos de acceso y latencia, eliminando en parte el cuello de botella actual con DDR4.

Esto es un gran paso adelante, tal y como representa Lakefield, salvo que Milán está orientado al alto rendimiento.