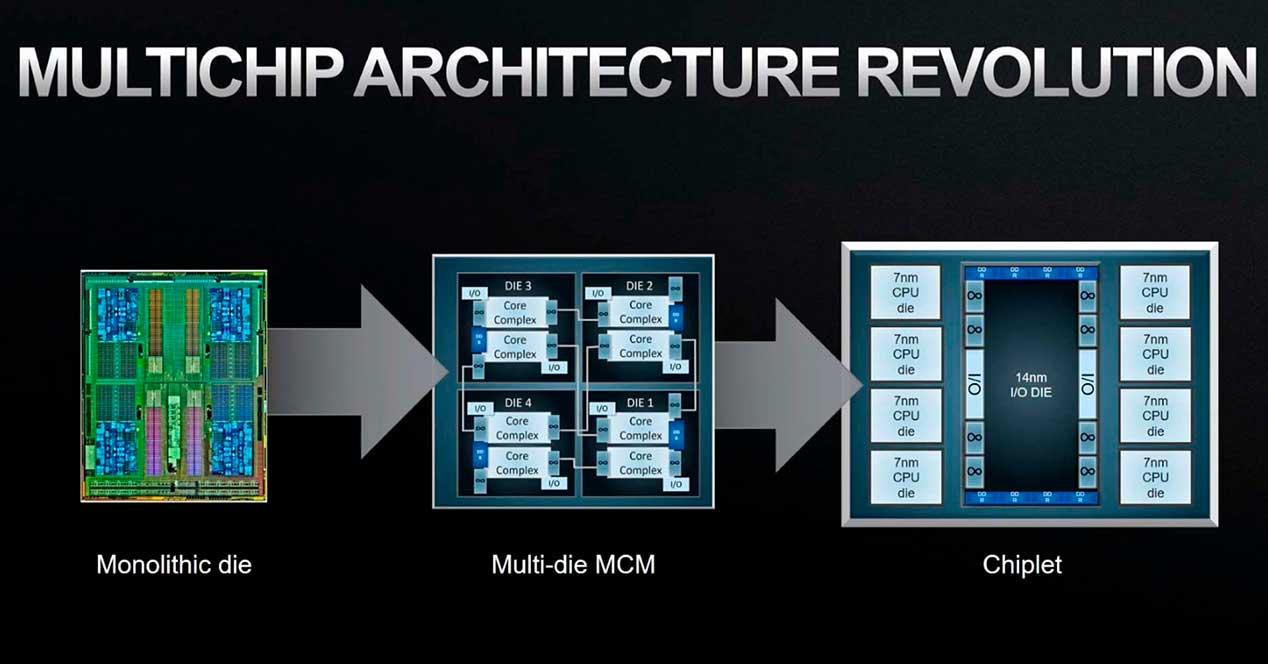

Toda la industria, hasta la propia Intel, aplaudió la introducción de la arquitectura Zen por parte de AMD al mercado de consumo y servidores, pero donde todo han sido fortalezas ahora están empezando a verse las flaquezas. Intel ha seguido con su arquitectura monolítica, sabedor de donde se estaba metiendo AMD. Por primera vez en la historia, ambas compañías van a tener que trabajar codo con codo para impulsar un nuevo enfoque de CPU, ¿qué está pasando?

Mientras todos aplaudíamos y nos maravillamos con la arquitectura Zen a base de chiplets, donde versión tras versión se ha llegado a una mejora notable del rendimiento, la realidad es que en términos de IPC parece que se está llegando a un límite que Intel no parece conocer con su arquitectura monolítica.

Por otro lado, Intel se encuentra en la tesitura de que les está costando seguir el ritmo en cuanto a número de núcleos frente a AMD. Esta situación va a dar paso a algo nunca antes visto en esta industria y donde se van a sumar a su causa otros dos gigantes más: TSMC y DoD (el departamento de defensa de Estados Unidos).

Los chiplets son el futuro, pero no a este precio

AMD dio con la tecla, pero tiene un problema muy grave en el futuro más inminente: los diseños de las CPU se están volviendo cada vez más complejos y esto está dejando unos costes de I+D que no paran de aumentar.

Si a esto le sumamos el hecho de los precios contenidos de sus procesadores, no es de extrañar que la ecuación comience a fallar más pronto que tarde. No en vano, ya hemos hablado de que AMD tendrá que subir precios en sus nuevas arquitecturas y productos, y es que están abandonando la senda del costo por la de la rentabilidad como empresa.

Esto no parece ser suficiente de aquí a ciertos años vista y junto con Intel, TSMC y DoD, se está barajando la idea de sentar precedente con diversos estándares de industria que permitan una homogeneidad en los procesadores y al mismo tiempo no coarte el I+D de cada compañía.

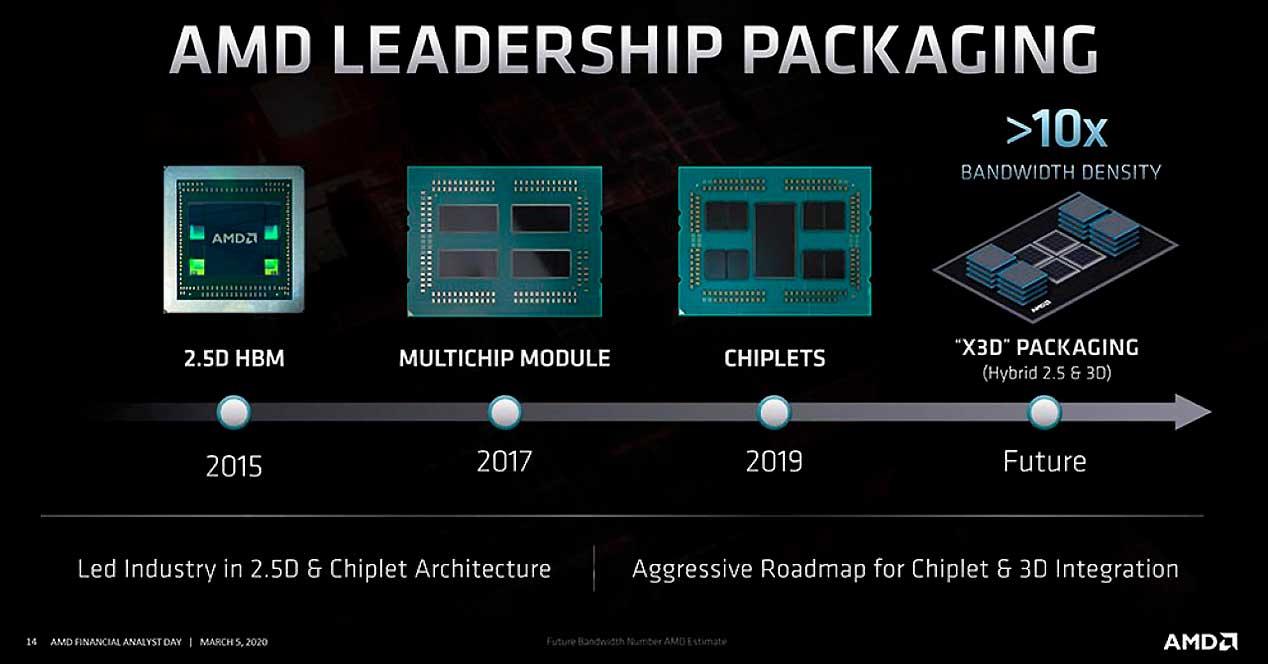

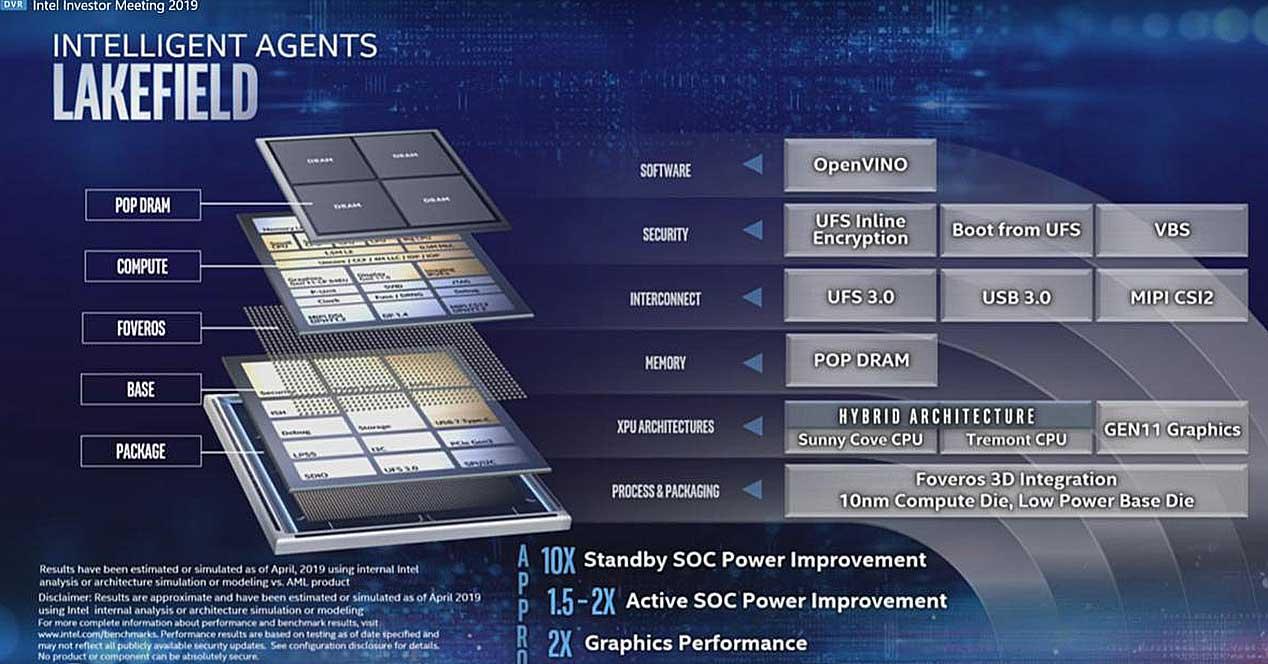

Aunque AMD lo dejó entrever en una presentación, los costes que están asumiendo ellos e Intel con Foveros son astronómicos, lo que unido a los procesos litográficos más avanzados como los que diseña TSMC están propiciando una escalabilidad de precios que dentro de poco tiempo no será asumible ni por las empresas.

Package 2.5D, 3D, metodologías de arquitectura e interposers

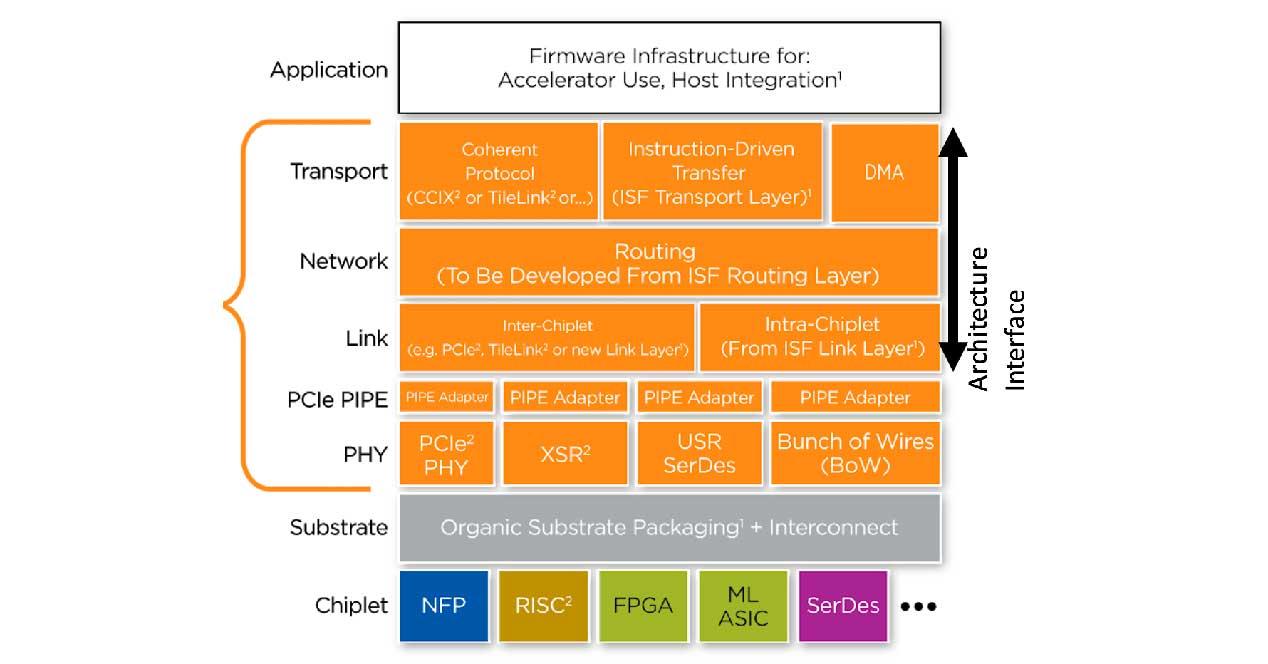

Con esto en mente, el futuro pasa por la unificación de criterios como estamos viendo desde el año pasado con tecnologías como CXL. No va a ser suficiente que cada uno de los protagonistas vaya por libre en sus diseños, no si quieren sobrevivir a los costes.

La expresión clave aquí es «estandarización comercial«, la cual por supuesto no va a ser fácil de llevar a cabo debido a los proyectos de cada compañía. Pero lo que se busca en la industria y con las futuras colaboraciones que van a tener que mantener los protagonistas es acelerar el tiempo de lanzamiento de sus productos al mercado, reducir el costo de la integración de chiplets y facilitar las pruebas de cada uno de ellos para un package distinto.

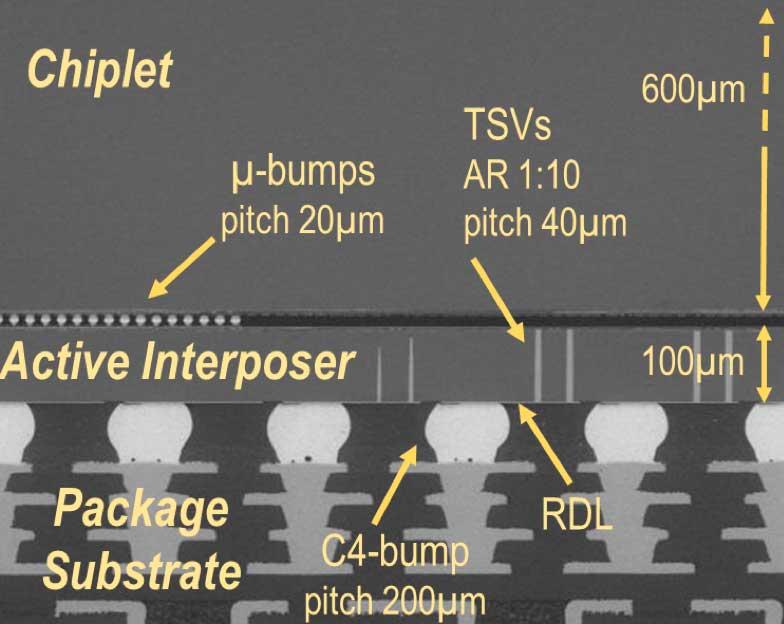

Esto va a necesitar de una serie de estándares comunes que delimiten los aspectos donde va a trabajar la industria y aquí es donde todas van a tener que trabajar codo con codo para definirlos y con ello dar vida a las CPUs del futuro. La intención es que cualquier cliente pueda mezclar y combinar diferentes chiplets y conectarlos utilizando un esquema de interconexión die a die que sea estándar, es decir, usar un interposer común.

Esto tiene que ser válido para diseños 2.5D como el de AMD o 3D como el de Intel, por lo que no será fácil llegar a una arquitectura de interposer estándar que normalice el uso de todo lo anteriormente explicado.

La estandarización evitará pruebas y detección de errores costosas

Uno de los puntos clave de la estandarización de las arquitecturas, chiplets y sustratos es el hecho de que las pruebas para detectar fallos en las obleas y chips deben ser más baratas, fáciles de realizar y por ende se debe dedicar un menor tiempo en ellas.

El problema del sistema actual es precisamente el descartar las capas que no son válidas por diferentes problemas en el grabado o impurezas. Recordemos que el apilamiento que sugieren tanto AMD como Intel requiere un gran número de capas, por lo que detectar a tiempo los problemas en las obleas permite eliminar los chips antes de la etapa de apilamiento, que es tremendamente costosa por detalles como las TSV.

Por lo tanto, uno de los primeros factores que tendrán que llevar a cabo Intel, AMD, TSMC y DoD es el equilibrio de los costos de las pruebas, del costo de malos rendimientos en las obleas y de la detección de los errores para poder llevar la tecnología diseñada a producción de alto volumen.

Los cuatro grandes se enfrentan por tanto a un reto gigantesco y solo de su colaboración saldrán las CPUs del futuro, ya que la escalabilidad de estas depende de dicha estandarización. Esto por supuesto no quiere decir que se dejen de fabricar CPUs monolíticas, pero tal y como dijo Intel hace algo más de un año, los costos también comenzaban a ser un problema.

A esto hay que sumarle el parón que veremos en poco más de diez años sobre los procesos litográficos. CPUs monolíticas verán entonces el problema frente al espejo: si no se reducen los transistores se necesitará más superficie de cada oblea para incluir mayor número de ellos, una historia que sabemos bien donde termina y que el límite del átomo tratará como un drama.