Hasta ahora hemos visto las muchas maneras que tienen las controladoras de los SSD para maximizar la vida útil de los dispositivos, siempre tratando de reducir los ciclos de escritura y borrado, que son los que producen desgaste. Hoy vamos a tratar cómo se gestiona la NAND interna de los SSD con el mismo fin, prolongar su vida útil para así maximizar su esperanza de vida.

Además del rendimiento, uno de los mayores objetivos de los diseñadores de SSDs es que sean duraderos, y para ello emplean una combinación de varias técnicas. En algunos modelos, y es lo que vamos a ver hoy, la controladora SSD es capaz incluso de gestionar el funcionamiento interno de los propios chips de memoria NAND Flash. Vamos a ver cómo lo hacen.

No todas las controladoras pueden gestionar la NAND

Aunque esta parezca una tarea de suma importancia (que la controladora gestiona cómo funcionan los chips de memoria parece algo obvio, ¿verdad?), en realidad no muchas controladoras adoptan este enfoque, y de hecho esta es una técnica que por norma general no está disponible, si bien cada vez más fabricantes de controladoras están implementándola.

¿Por qué esto es así? Por temas de propiedad intelectual. Básicamente, quienes fabrican las controladoras no son los mismos que fabrican los chips de memoria NAND Flash, y por lo tanto los unos no quieren compartir sus diseños con los otros, dado que para que la controladora pueda gestionar la NAND interna, debe saber exactamente cómo funciona y tener control sobre ella.

Esto significa que para que la controladora del SSD pueda gestionar la NAND interna, dicha controladora estará dedicada a una sola marca de NAND, es decir, sería una controladora específicamente diseñada para un único modelo de NAND o incluso para una única familia de SSDs. Entenderéis que, por lo tanto, son muy pocos los casos que encontraremos, y la mayoría son con tratos cerrados o de fabricantes que fabrican su propia NAND y controladora, sin recurrir a terceros.

Así se gestiona la NAND interna desde la controladora

Supongamos que tenemos un fabricante de SSD con un proveedor de NAND que está dispuesto a divulgar la información de diseño de sus chips. En ese caso la controladora del SSD podría administrar muchas variables que se pueden controlar cambiando la configuración interna de los chips NAND Flash internos, y si lo que queremos es maximizar la vida útil de un SSD, entonces se modifican los parámetros que influyen en los errores de bits:

- Umbrales entre niveles en MLC.

- Tiempos de programación y algoritmos.

- Relaciones de colocación física entre celdas adyacentes.

- Métodos para liberar electrones que se quedan atrapados por el camino.

Hay algunos métodos más que pueden colaborar en maximizar la vida útil del SSD y que pueden ser gestionados por la controladora, pero son tan sumamente internos que, en realidad, par el usuario no tienen ninguna repercusión ni interés.

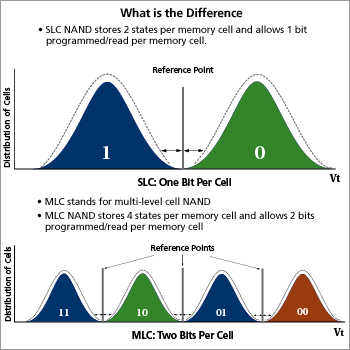

Para daros una idea de cómo funciona esto veamos solo un parámetro, la detección de nivel de MLC. Cuando se programa una memoria flash MLC, se colocan dos bits en una sola celda y ésta pasa a tener uno de estos cuatro niveles:

- Descargada.

- 1/3 de carga.

- 2/3 de carga.

- Totalmente cargada.

Ciertos problemas, inevitables, pueden hacer que estos niveles se desvíen de su punto de referencia. Los electrones pueden quedar atrapados en el óxido de los túneles de comunicación, y esto puede hacer que la puerta flotante parezca tener una carga mayor que el algoritmo de programación que realmente se le coloca. Las influencias térmicas y otros motivos pueden drenar electrones de la celda, reduciendo su carga, o las lecturas y escrituras de celdas adyacentes pueden agregar o eliminar electrones de la puerta flotante.

Una controladora que comprende estos fenómenos puede ajustar los umbrales de detección dentro del propio chip NAND para ayudar a reducir la posibilidad de que un bit sea malinterpretado. Si se supone que una celda tiene 2/3 de carga, pero parece que tiene 1/3 de carga, ¿se leerá como 1/3 ó 2/3? Si la controladora SSD gestiona estos umbrales para compensar otros factores, se puede reducir el impacto que tendría esta fuente de errores de bits.

Claramente, esta es una forma bastante extrema de exprimir hasta el último ápice de vida útil del SSD, pero ya sabéis que cada granito de arena cuenta y la suma de todos hace que la vida útil de los SSD sea cada vez más extensa.