Hace ya casi un año que Intel desveló una de las tecnologías más relevantes para esta década y con ella una arquitectura que sorprendió a todos por el enfoque y la implementación que los azules van a llevar a cabo. Dicha arquitectura es LakeField, la cual ha estado en desarrollo durante décadas y que tendremos el privilegio de contemplar, pero ¿qué es y por qué es tan revolucionaria?

Puede parecer complicado el enfoque que Intel ha dado a esta arquitectura y SoC, pero la realidad es que al igual que ARM ha entrado a competir de manera más o menos decente en el mercado de servidores y escritorio, ahora es Intel la que va a intentar asaltar el mercado de los smartphones, televisores y en general el llamado IoT.

LakeField es no un paso, si no un salto hacia el futuro por lo que representa y por como está diseñado, que al mismo tiempo es lo más interesante de la arquitectura.

Intel LakeField, llega la implementación 3D a los chips del futuro

Pongamos las principales cartas sobre la mesa de entrada para comprender el tipo de tecnología al que nos estamos refiriendo y que enumerándolas, será más sencillo de comprender:

- Estamos ante un SoC móvil.

- Ultra bajo consumo (2 mW).

- Primera arquitectura real multi núcleo de Intel.

- Primer Penta Core de su historia.

- Primer chip de la compañía basado en el concepto big.LITTLE.

- iGPU Gen 11 integrada.

- Tecnología Foveros con empaquetado de chips 3D.

- Soporte para LPDDR4X.

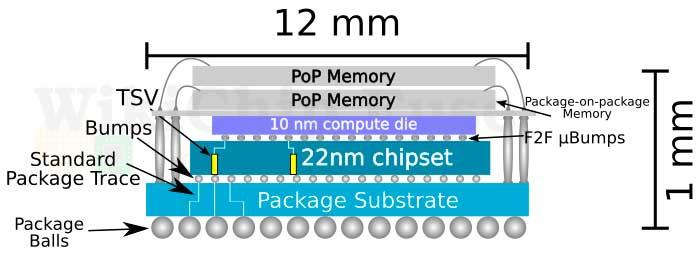

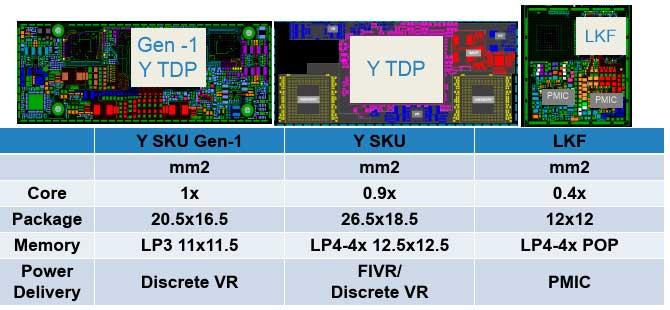

- Solo ocupará 12 x 12 mm con 1 mm de altura.

Muchos conceptos, mucha innovación y sobre todo muchos años de desarrollo que sentarán el pilar de los procesadores de nueva generación, no solo de Intel, sino de AMD y el resto de compañías que quieran poder competir. Todo el sector va enfocado al llamado package 3D, no nos engañemos, es el futuro y en breve será el presente, pero para comprenderlo es necesario entender cómo está hecho LakeField.

Apilamiento 3D, la base de la nueva generación de dies

No es difícil de comprender el concepto de dies 3D. Son chips que están unidos verticalmente, unos encima de otros con distintas tecnologías de las que ya hablamos, como EMIB, Foveros o Co-EMIB mediante ODI.

En LakeField Intel ha sido ambiciosa e inteligente a partes iguales, el sustrato (matriz) ha sido usado para todas las funciones que Intel denomina como «bajo consumo». Esto incluye la interfaz USB-C 3.0, algunos buses de entrada y salida de menor rendimiento y sobre todo la interfaz PCIe Gen 3.

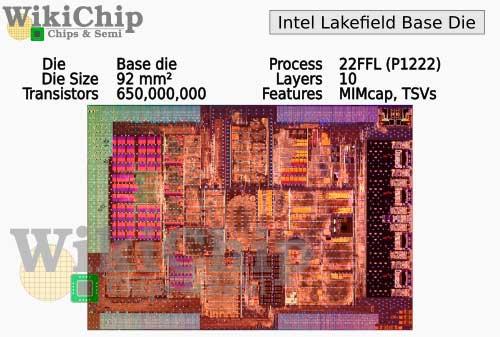

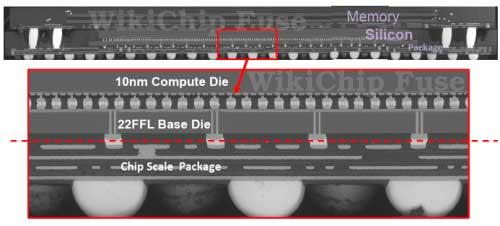

Como buena base, será mayor que el tamaño final del chip y ostenta 92 mm2 bajo el proceso de 22 nm FFL, también llamado 22FFL, que aunque no lo parezca por su nomenclatura, es realmente un proceso muy específico para este tipo de productos que se basa en los 14 nm, pero que está optimizado para SoC móviles.

Por lo tanto los transistores serán grabados a 14 nm y facilitarán con ello la eficiencia de toda la matriz. Es barato, tiene capacidades mejoradas específicas para este tipo de producto y tiene un menor número de capas que un die normal, así que tiene lo mejor de Intel salvando sus nuevos 10 nm y los próximos 7 nm, donde el coste todavía es muy alto.

El die es el más avanzado creado hasta la fecha por Intel

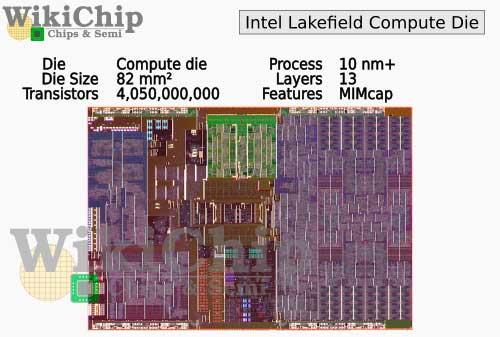

Vista su base, vamos a introducirnos con el die propiamente dicho, donde están todas las bondades y novedades de esta arquitectura y chip. Hablamos de un troquel de solo 82 mm2 con más de 4 mil millones de transistores, lo cual evidencia que la densidad es absolutamente brutal y no vista hasta ahora.

Esto tiene su explicación, y es que LakeField llegará bajo los nuevos 10 nm+ de Intel, es decir, la segunda generación de su nuevo proceso litográfico que aumenta la frecuencia bastante frente a su segunda versión y mejora un poco la densidad final. Aquí hay que recalcar que, según parece, el 37% del chip se gastará en la iGPU, lo que evidencia el esfuerzo que tiene que hacer Intel con Gen 12 para hacer tarjetas gráficas integradas más potentes y con menor área final en un die.

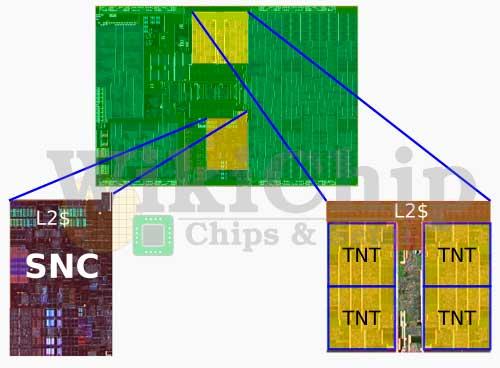

En cuanto a los núcleos en sí mismos, encontraremos cuatro basados en la arquitectura Tremont y un solo Sunny Cove, donde Intel no ha habilitado Hyper Threading. Esto se ha realizado así para facilitar el reparto de tareas en los sistemas operativos, ya que parece que esta tecnología necesitará un tiempo por parte de los desarrolladores para que rinda como se estima.

La ventaja aquí por otra parte es que un núcleo Tremont a misma frecuencia que un Sunny Cove alcanzará hasta un 70% del rendimiento de este, pero con un consumo infinitamente inferior.

Para ello se necesita que las cargas de trabajo lleguen en ráfagas para el mayor de los núcleos, mientras que los procesos en segundo plano son gestionados por los 4 núcleos Tremont, ahorrando así mucha energía.

Por último, se estima que los cuatro núcleos Tremont sean de un tamaño similar al núcleo Sunny Cove, incluidas sus cachés y las instrucciones AVX-512 (desactivadas de serie), por lo que podemos hacernos una idea del potencial que podrían tener los chips futuros casi a misma área.

Foveros

Ya hemos hablado largo y tendido sobre esta tecnología y sus hermanas, así que nos saltaremos la parte teórica para comentar brevemente como Intel piensa disponer sus chips verticalmente. Tendremos dos capas principales más los chips de memoria RAM LPDDR4X, lo cual es impresionante.

La matriz está unida «cara a cara» con el sustrato de 22 nm LFF mediante micro bumps de 50 um y este a su vez con el package principal. Las memorias se depositan justamente encima de los núcleos y su matriz de 10 nm+ con TSV de 350 micrones para su interconexión. Por lo tanto y resumiendo, tenemos 5 capas en total en un chip que mide 12 mm2 y 1 mm de altura.

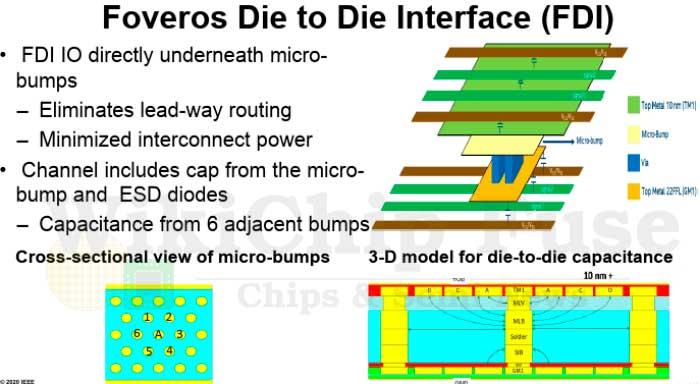

Las interfaces de comunicación se realizan mediante lo que Intel ha llamado como FDI o Foveros Die Interface, donde la velocidad máxima que alcanzan entre matrices es de 500 MT/s y por carril. Teniendo en cuenta que posee más de 200 carriles con un mismo clock, pues tenemos un ancho de banda realmente asombroso para un chip de ese tamaño.

Para finalizar este apartado, hay que tener en cuenta que esta disposición de los die da como final un factor de forma distinto que incluye un suministro de energía a través de las TSV al que se le ha denominado como PMIC y que nada tiene que ver con los controladores de voltaje de las series mobile U y Y.

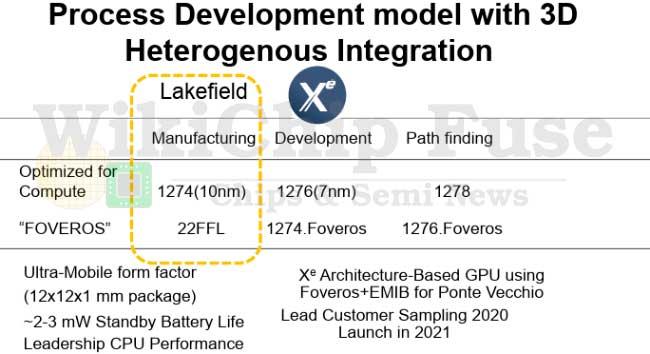

LakeField, el futuro del apilamiento 3D

Como ya vimos con Co-EMIB y ODI, el futuro de la compañía pasa por mejorar lo existente con LakeField. El primer paso será mejorar eficiencia y costes, para poco a poco ir implementando mejoras varias que requieren nuevos sistemas de creación CAD, suministros de energía, ESD, integridad de señales y un largo etc …

Lo que buscará Intel en un corto periodo de tiempo es compaginar núcleos de bajo consumo con núcleos de muy alto rendimiento, incluyendo GPUs Xe con HBM y todo en un mismo encapsulado vertical 3D que ofrezca lo mejor de todos los mundos.