Uno de los conceptos más extendidos de la informática actual es sin duda el de XMP. Cualquier usuario medianamente interesado en el hardware sabe que cuando hablamos de perfiles de overclock de memoria Intel le tiene cogida la medida a AMD, la cual intenta constantemente adaptarse a estos requerimientos mediante su tecnología AMP. Con la salida de Alder Lake-S como arquitectura revolucionaria Intel ha dado un paso más allá presentando con ello XMP 3.0, pero ¿qué novedades esconde?

Algunos se preguntan los porqués de las decisiones de Intel con respeto a la memoria RAM y en concreto al XMP. Aunque nunca lo sabremos, lo cierto es que el paso de la DDR4 a la DDR5 era un momento ideal desde la óptica del overclock para implementar cambios y mejoras, puesto que como estamos viendo los 4.800 MHz del JEDEC se están quedando atrás solo días después de ser presentadas las CPUs Core 12.

Por lo tanto y dado lo rápido que aceleran y actualizan los fabricantes sus módulos con velocidades de serie cada vez mayores solo queda preguntarse, ¿ha tenido en cuenta esto Intel? ¿XMP 3.0 está al día con lo que se le exigirá?

Intel XMP 3.0, una vuelta de tuerca necesaria

eXtreme Memory Profile o XMP lleva con nosotros desde 2007 y en esta tercera versión mirando hacia atrás y tras 14 años es normal que el gigante azul lance una nueva revisión con novedades. ¿Por qué? Por los cambios que supone DDR5 con respecto a DDR4. No entraremos en este tema puesto que ya lo tratamos en extensión, pero si algo hay que decir de XMP 3.0 es que es exclusivo de DDR5 como tal.

El término Profile de su nombre nos viene al dedo para explicar el primero de los puntos donde Intel ha dado a los fabricantes, ya que como bien sabemos esta tecnología se basa en el reconocimiento de una serie de tablas de configuración que integra cada fabricante al gusto por modelo, chip y versión de la memoria para lograr que el IMC reconozca mediante el firmware dicha configuración y la aplique.

Novedades de Intel XMP 3.0

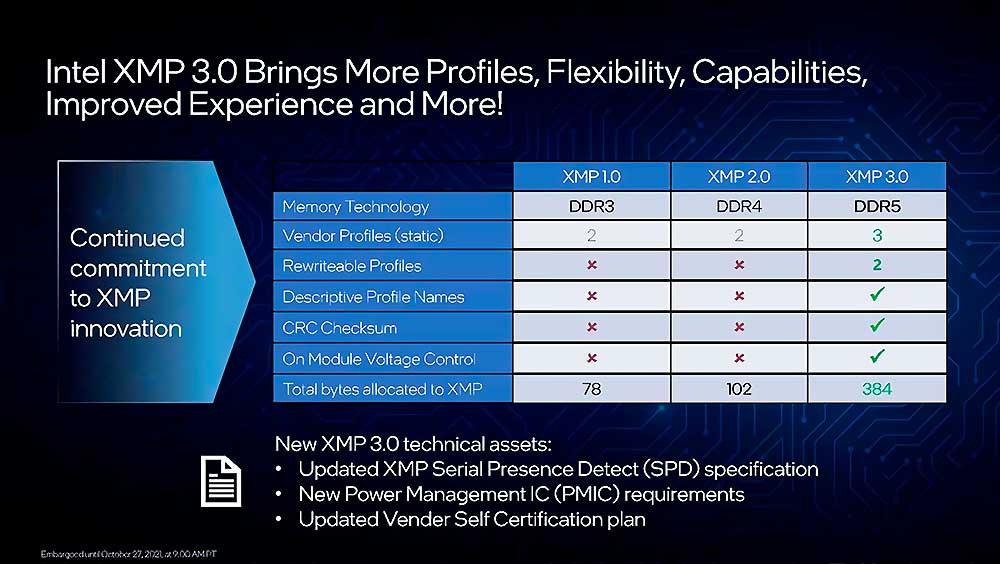

Estas tablas incluyen velocidades en MHz, clocks y tiempos de accesos primarios, secundarios y terciarios que lógicamente son más rápidos en unos casos o más lentos en otros, pero que en todos los casos aumentan el rendimiento general de la memoria y con ello del sistema. En la primera versión llamada como su propio nombre, XMP, Intel consiguió incluir en ella la inclusión de lectura de un perfil dentro de la memoria más el del JEDEC (técnicamente es un perfil, pero se contabilizan como dos)

XMP 2.0 subió el nivel a dos perfiles de lectura, donde los fabricantes podían establecer si así lo querían dos valores y tablas distintas personalizando la experiencia del usuario y favoreciendo distintos rendimientos (tres reales contando el JEDEC). Con XMP 3.0 los fabricantes ahora pueden disponer de dos o tres perfiles a incluir pudiendo seleccionar dos personalizados por el usuario.

Actualización del SPD

Uno de los puntos clave para el perfil XMP es precisamente la especificación SPD o Serial Presence Detect. Esto ha traído múltiples quebraderos de cabeza a fabricantes y usuarios, principalmente porque se pueden escribir desde EEPROM y por lo tanto corromperse. Hay algunos programas que pueden hacerlo y claro, crea bloqueos en el controlador de memoria, ya que este no puede leer los valores correctamente del XMP y la memoria queda inservible hasta que no se materialice un nuevo flasheo correctamente.

Ahora y con XMP 3.0 tendremos dos perfiles actualizables, lo que ayuda a que si uno se corrompe el otro pueda dejar la memoria funcionando, pueda extraerse su SPD y posteriormente podría flashearse módulo por módulo reparando la memoria como si tal cosa.

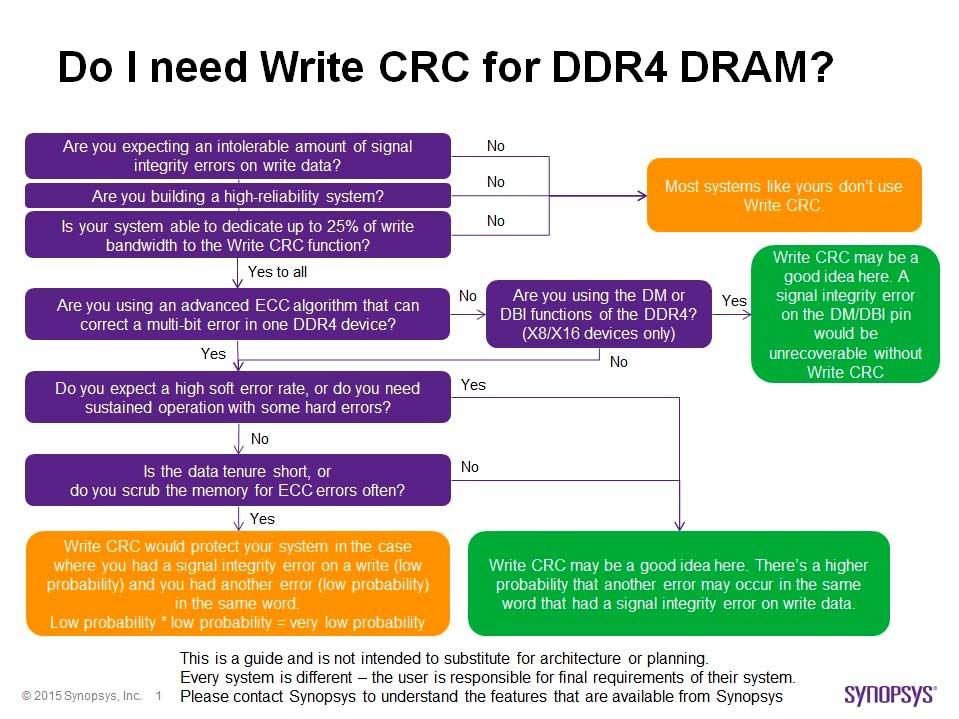

CRC Checksum

Aunque parezca mentira y ya explicado esto, ¿por qué los módulos DDR4 con XMP 2.0 no tienen CRC? No es exactamente así y lógicamente tiene un por qué. CRC como tal se agregó en su versión Write en el estándar JEDEC para DDR4, pero el código de redundancia cíclica tiene un problema: el alto consumo de ancho de banda. Los datos muestran consumos del 25% de la escritura total del sistema y claro, no es asumible perder esa cantidad de ancho de banda con los márgenes y velocidades que nos movemos hoy en día.

Esto deja de ser un problema con DDR5, puesto que además de incluir el PMIC en la propia memoria, en el módulo físicamente hablando, las velocidades son y van a ser monstruosas en comparación con DDR4, más si contamos con el doble ancho de banda que integra este tipo de memoria. Por lo tanto, Intel con XMP 3.0 integra el buscado CRC Checksum que protegerá los datos y la integridad del SPD así como del controlador de memoria de la CPU.

Mayor aumento del espacio para XMP 3.0

Uno de los aspectos clave y ya entendiendo todo lo que hemos comentado del nuevo XMP 3.0 es que, lógicamente, necesitamos más espacio para albergar todo esto. Por ello, Intel ha pasado de los 78 bytes por módulo de XMP 1.0, a los 102 de XMP 2.0 y ahora lo eleva hasta los 384 bytes de control para XMP 3.0.

Esto es lo que permite que los perfiles de memoria preestablecidos como SPD se puedan seleccionar desde la BIOS/UEFI de la placa base. La duda que nos queda entonces es el comportamiento del IMC de los nuevos procesadores Alder Lake y Meteor Lake (se espera un salto de frecuencia importante) con las diferentes velocidades que vamos a ir viendo por parte de los fabricantes y chips.

¿Vamos a ver perfiles XMP 3.0 por encima de los 6000 MHz? ¿Puede el IMC de las CPU soportarlos sin desbordar el voltaje y con ello el consumo y degradación? De momento sabemos que hay marcas trabajando en perfiles para DDR5-7000, por lo que parece que o bien estas nuevas memorias y los chips están consiguiendo evolucionar mucho más rápido que las CPU y su IMC, o bien quiere decir que el potencial de subida y soporte/aguante de los controladores de memoria integrados es mayor del que podíamos pensar.

Hay que tener en cuenta que aunque XMP 3.0 llegue a velocidades muy altas en ciertos módulos es el IMC el que determina si es capaz de soportar dicha velocidad y su voltaje, el cual es independiente lógicamente del de la propia memoria RAM.

Dicho y aclarado esto, solo podemos afirmar que Intel ha dado un paso adelante muy grande, el mayor desde que lanzó XMP en 2007 y como tal, ahora es AMD la que va a tener que adaptar su tecnología e IMC a estos nuevos requerimientos con Zen 4.