La tecnología conocida como X3D es una de las más importantes para AMD de cara al futuro por no decir la más importante, ya que es con la que van comunicar los diferentes elementos de sus procesadores entre sí. Su importancia radica en que va a reemplazar la tecnología Infinity Fabric y aunque se encuentra todavía en un horizonte que nos parece lejano cada día lo tenemos más cercano.

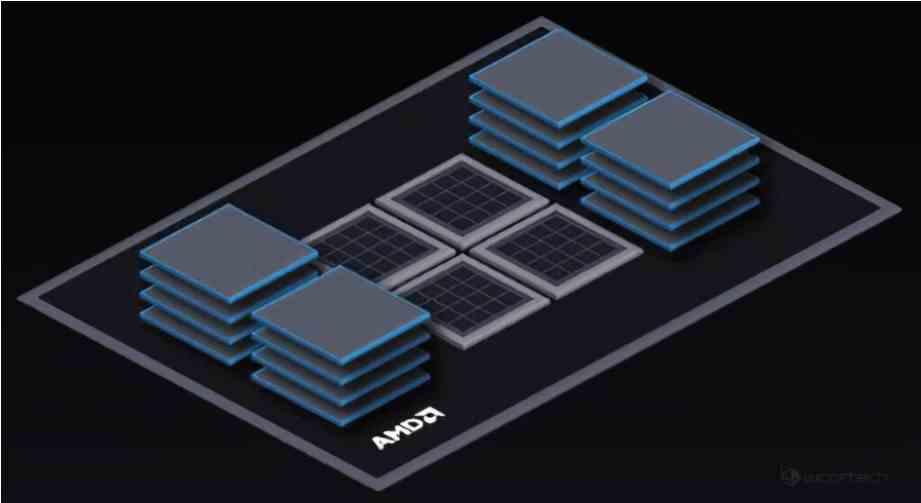

De cara al desarrollo del Exascale Heterogenous Processor, el cual ha sido clave para que AMD pueda ganar el contrato de construcción de El Capitan han tenido que crear un nuevo tipo de interfaz para que la comunicación entre la CPU y la GPU se pueda hacer en un entorno donde ambas compartan el mismo pozo de memoria, esto ha obligado que AMD haya tenido que desarrollar un nuevo tipo de interfaz de comunicación, la cual viene a solucionar un problema que hasta ahora AMD no había podido solucionar.

¿Por qué no hemos visto una GPU basada en chiplets todavía?

La razón por el cual no hemos visto GPUs dedicadas en un MCM que comparta el acceso a la memoria con la CPU es porque el ancho de banda que otorga el IOD no es lo suficientemente grande para alimentar a una GPU. En el caso de un MCM con el sistema de memoria unificado estamos hablando aplicar la Infinity Cache de la GPU como L4 del sistema.

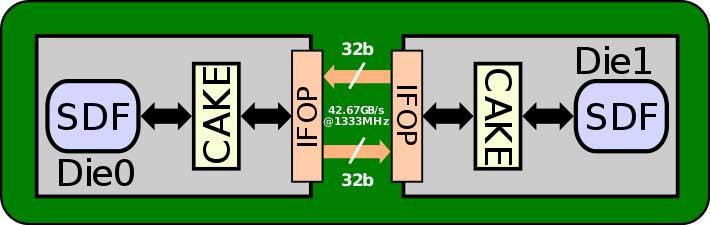

¿Por qué el Infinity Fabric no es suficiente? Pues por el hecho que este nos da una interfaz de 32 o 64 bytes/ciclo dependiendo de la versión

Imaginaos ahora que queremos conectar una Navi 21 (RX 6800, RX 6800 XT y RX 6900 XT), hay que tener en cuenta que entre la cache L2 dentro de la GPU y la Infinity Cache tenemos 16 particiones de Cache L2 con un ancho de banda de 64 bytes/ciclo cada uno, esto son unos 1024 bytes/ciclo en total y por tanto una interfaz de 8192 bits, la cual obliga a los ingenieros de AMD a desarrollar una interfaz de comunicación mucho más compleja que el Infinity Fabric con tal de poder comunicar una GPU utilizando el mismo pozo de memoria.

El problema del Infinity Fabric a la hora de comunicar externamente varios chips entre sí, es que es que al ser una conexión 2D en horizontal tiene una cantidad de pines limitada que podemos colocar sin llegar a aumentar enormemente el perímetro del chip. La otra opción si queremos aumentar el ancho de banda es aumentar la velocidad de reloj de cada uno de los pines, pero esto aumentaría enormemente el consumo energético, lo que provocaría que se saliese del presupuesto.

X3D, el reemplazo al Infinity Fabric

El problema del Infinity Fabric es que no sirve para comunicar los chips en vertical, por lo que no aprovecha la excelente relación entre el ancho de banda y consumo energético de las interfaces verticales que utilizan las vías a través del silicio y es con este problema encima de la mesa con el que AMD ha acabado por desarrollar de cara al futuro el reemplazo completo del Infinity Fabric.

El problema del Infinity Fabric es que no sirve para comunicar los chips en vertical, por lo que no aprovecha la excelente relación entre el ancho de banda y consumo energético de las interfaces verticales que utilizan las vías a través del silicio y es con este problema encima de la mesa con el que AMD ha acabado por desarrollar de cara al futuro el reemplazo completo del Infinity Fabric.

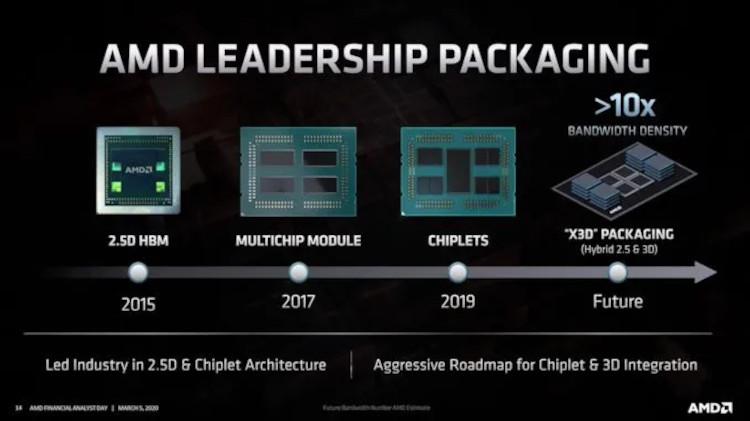

Cuando AMD anuncio el X3D, muchos pensaron que se trataba de un tipo de empaquetado, realmente no es así, sino que más bien se trataría de un nuevo tipo de interconexión como el Infinity Fabric, solo que esta funcionaría en vertical sobre un interposer, en una configuración muy parecida a la que se utiliza en los chips acompañados de memoria HBM.

La idea es tener una interfaz de comunicación con un consumo energético cercano a los 0.2 pJ/bit, lo cual permite un ancho de banda diez veces superior bajo el mismo consumo energético que el Infinity Fabric.

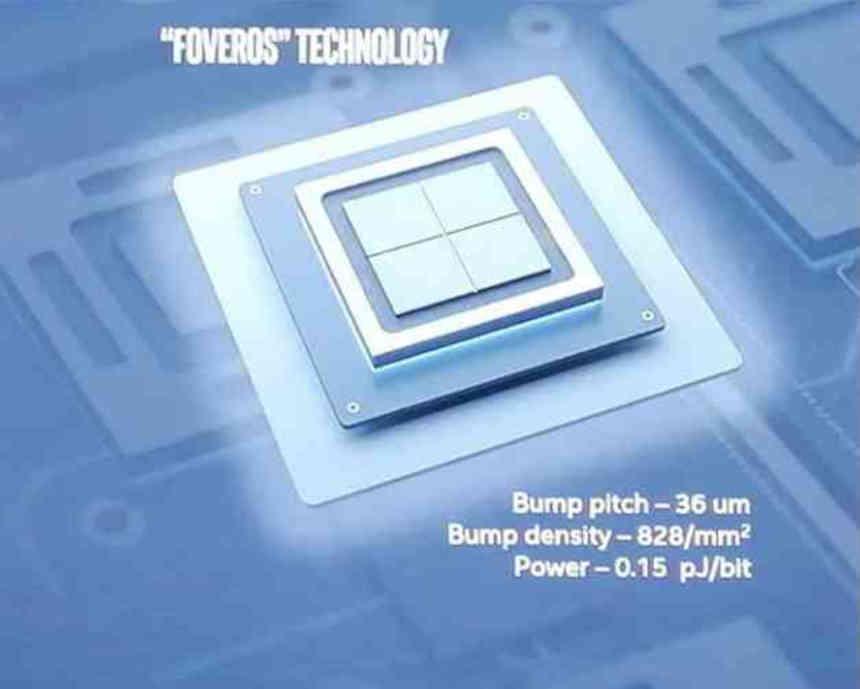

En realidad AMD va con retraso en comparación con Intel

La tecnología que AMD está desarrollando es una respuesta al Intel Foveros, donde Intel ha conseguido desarrollar ya un tipo de interconexión del mismo tipo bajo un consumo de 0.15 pJ/bit, por lo se puede decir que los de Lisa Su van con retraso y al igual que Intel son conscientes que los chips del futuro dependen del uso de nuevos tipos de interconexiones, la cuales están haciendo que el diseño de los diferentes procesadores resulte en un cambio de paradigma.

La tecnología que AMD está desarrollando es una respuesta al Intel Foveros, donde Intel ha conseguido desarrollar ya un tipo de interconexión del mismo tipo bajo un consumo de 0.15 pJ/bit, por lo se puede decir que los de Lisa Su van con retraso y al igual que Intel son conscientes que los chips del futuro dependen del uso de nuevos tipos de interconexiones, la cuales están haciendo que el diseño de los diferentes procesadores resulte en un cambio de paradigma.

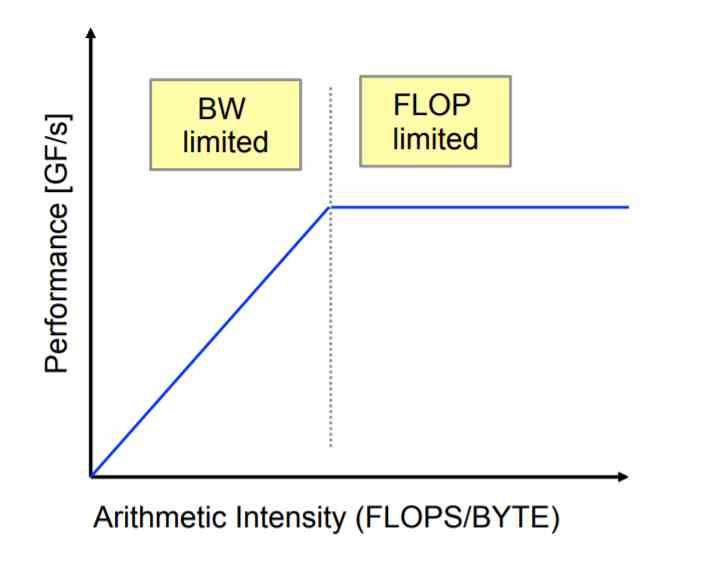

Pero, el motivo detrás de estas tecnologías esta en el desarrollo de superordenadores con la capacidad de llegar a la tasa de 1 ExaFLOPS, lo cual es fácil desde el punto de vista de ejecutar las instrucciones, pero casi imposible si hablamos del coste energético de la memoria. Para ello tenemos que introducir un concepto que es el de la intensidad aritmética.

La idea es que una arquitectura puede verse tan limitada por la cantidad de operaciones que realiza como por el ancho de banda que necesitan dichas operaciones. Claro está que si aumentamos enormemente la capacidad de procesamiento entonces también lo tenemos que hacer con la memoria. pero, ¿es la memoria que tenemos lo suficientemente adecuada para escalar en procesamiento?

La evolución de la RAM ha sido muy monótona, cada x tiempo aparece un nuevo nodo de fabricación, el cual permite reducir el consumo energético en la transferencia de datos, pero la velocidad a la que evoluciona la RAM no es lo suficientemente rápida como para hacer frente a los retos a los que los fabricantes de procesadores como Intel y AMD se enfrentan, lo que les lleva a solucionar el problema ellos mismos.

La necesidad de un nuevo tipo de memoria RAM

Hace tiempo que esperamos la HBM Next Gen o HBM3, su especificación lleva tiempo congelada y el motivo de ello es que cada uno de los principales fabricantes de procesadores (AMD, Intel y NVIDIA) están desarrollando su propia memoria «HBM3». En el caso de AMD estarían basando el desarrollo de este tipo de memorias en la creación de una 3D DRAM con una interfaz de comunicación basada en la interfaz X3D, la cual aplicarán por primera vez en superordenador El Capitan.

Hace tiempo que esperamos la HBM Next Gen o HBM3, su especificación lleva tiempo congelada y el motivo de ello es que cada uno de los principales fabricantes de procesadores (AMD, Intel y NVIDIA) están desarrollando su propia memoria «HBM3». En el caso de AMD estarían basando el desarrollo de este tipo de memorias en la creación de una 3D DRAM con una interfaz de comunicación basada en la interfaz X3D, la cual aplicarán por primera vez en superordenador El Capitan.

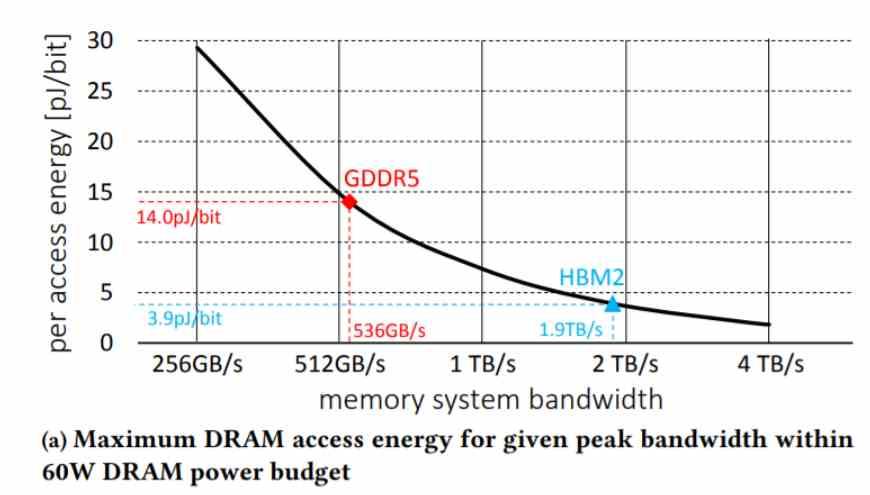

El problema es que todo sistema tiene un ancho de banda limitado por el consumo energético que se le asigna al sistema, y por mucho que aumentemos el ancho de banda se llega al punto en que no podemos aumentarlo más por el hecho que el consumo energético de la memoria es demasiado alto, de ahí a que continuamente se desarrollen memorias con una cifra de pJ/bit cada vez más baja.

¿Pero qué es lo que consume más energía? Las interfaces de comunicación que se utilizan para mover los datos, la idea es llegar a una cifra de pJ/bit lo suficientemente baja no solo para comunicar los chiplets GPU sin problemas sino también para poder crear memorias con un alto ancho de banda sin aumentar considerablemente el consumo.

¿Memoria X3D DRAM?

Si habéis visto el mapa de ruta de AMD en cuanto al empaquetado pensaréis de entrada que la memoria apilada en el concepto del X3D es un tipo de memoria HBM, pero, realmente no es así.

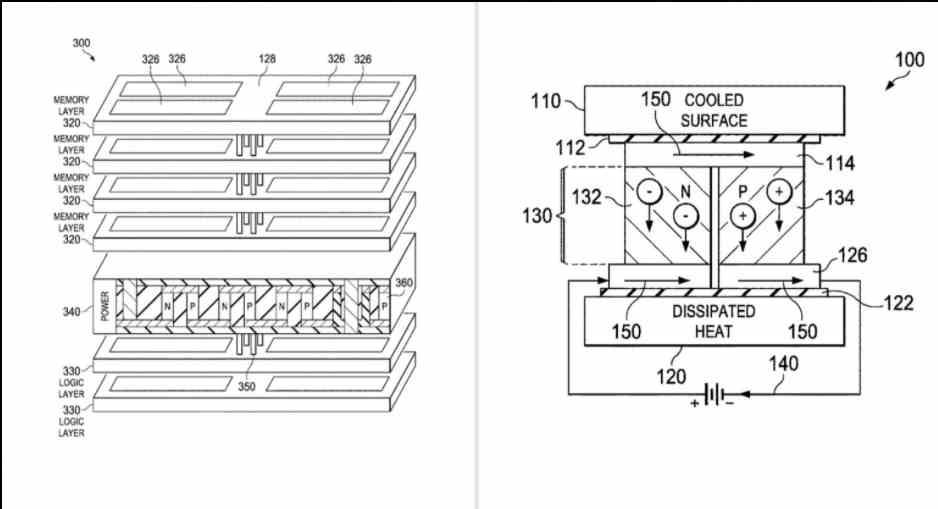

Se trata de un tipo de memoria creada como reemplazo a la actual HBM2e que AMD ha desarrollado internamente en el desarrollo del EHP para la creación del superordenador «El Capitan». ¿Las particularidades de este tipo de memoria? Sabemos muy poco, pero lo poco que sabemos es lo siguiente:

- Utiliza la interfaz X3D para comunicarse de manera externa, esto le ahorra a AMD tener que añadir piezas de conversión de un tipo de interfaz a otro.

- AMD estaría experimentando el uso de sistemas de refrigeración como células peltier encima de esta memoria, para así alcanzar velocidades de reloj más altas.

- AMD se plantea la inclusión de aceleradores o coprocesadores en la lógica de este tipo de memorias.

Desconocemos si AMD en el futuro va a vender esto en el mercado doméstico, pero lo más seguro es que veamos una versión reducida de esta tecnología. ¿Veremos MCMs de marca AMD en la que CPU+Memoria+GPU+Aceleradores formen parte de un todo? Quien sabe, pero lo que no hay duda es que AMD hará uso de esta tecnología también a nivel doméstico, para la creación de nuevos chips.

¿Vamos a ver por fin CPUs y GPUs de gama altas funcionando en conjunto en un MCM? Es muy probable, ya que es a lo que apunta AMD.