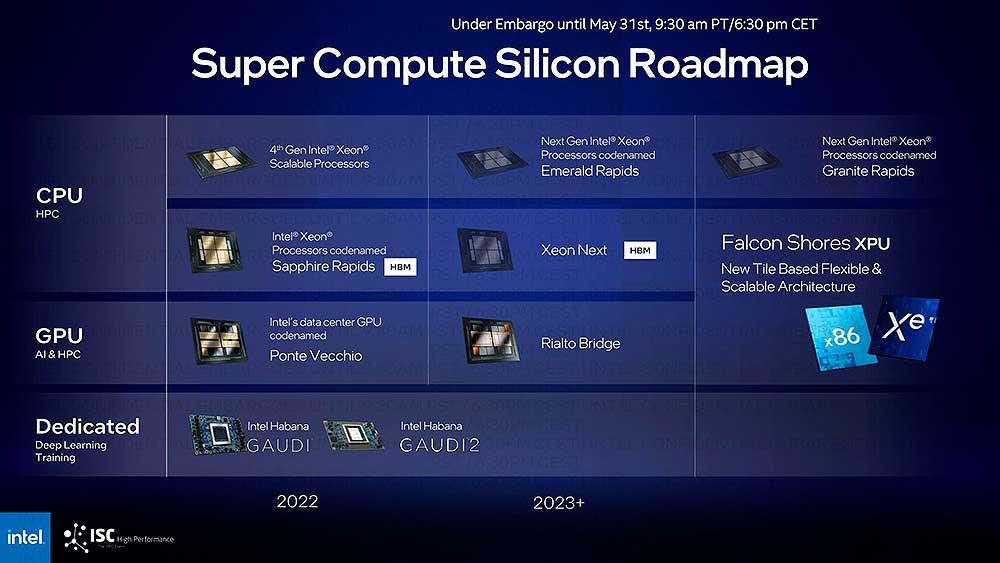

Tras la presentación oficial de la NVIDIA H100 con todas sus novedades tan sumamente alucinantes ahora llega Intel y da un puñetazo en la mesa con el anticipo del futuro más próximo y antesala de lo que está por llegar en el mundo de la IA y el HPC. Rialto Bridge será el punto definitivo y final de las GPU como las conocemos hoy en día, puesto que el futuro pasa por XPU bajo Falcon Shores. Entre tanto, estas nuevas GPU son un paso de gigante de los de Pat Gelsinger para hacerse con un importante hueco en el sector clave que domina el mundo en la actualidad.

Lo presentado por la compañía, sin rendimiento de por medio, supone el siguiente paso evolutivo frente a Ponte Vecchio, GPUs que todavía no han llegado al mercado como tal y que en cambio ya tienen sucesores. Lo revelado se centra en 6 aspectos clave que vamos a desgranar, aunque las declaraciones son escuetas como era de esperar.

Intel Rialto Bridge, la GPU más bestia diseñada hasta ahora

No hay grandes novedades aquí y algunas de ellas son esperables, podríamos decir perfectamente que Rialto Bridge es una evolución lógica de Ponte Vecchio siguiendo una estructura muy similar y estaríamos en lo cierto. Lo primero que tenemos que tener en cuenta es que la estrategia IDM 2.0 de Intel que tiene como baluarte precisamente las GPU Ponte Vecchio llegará a un nivel mucho más avanzado y que tendrá como principal reclamo los cambios de nodo en sus diferentes partes.

No se han especificado como tal, pero hay ciertos rumores que afirman que los Link Tile podrían llegar a 5 nm bajo TSMC, los die de las GPU en N4 y las cachés y otras partes como los Passive Die Stiffeners con Intel 4.

Pero, por otro lado, las diapositivas mostradas eliminan uno de los factores comentados hace un momento, puesto que no muestran curiosamente la RAMBO Caché de Intel. Esto podría indicar que Intel va a incluirla dentro de los Tiles de la GPU y crear con ello chips más complejos que podrían llegar con su nodo de fabricación Intel 4 y dejar con ello de lado a TSMC en esta parte del juego.

También se rumorea el hecho de usar memoria HBM3, lo que daría un mayor ancho de banda y obliga a Intel a actualizar su arquitectura Xe Link. Hay que entender que cualquier GPU aceleradora de este tipo tiene como principal limitación el ancho de banda de la memoria, el rendimiento es proporcional a este, así que por eso Intel anuncia más FLOPS y GT/s sin dar mayor explicación.

Dicho esto, saltemos a otros menesteres igual de importantes con Rialto Bridge.

OAM 2.0, el consumo y el aumento de Cores

El tipo de socket que usará Intel para Rialto Brigde será OAM 2.0, la cual es una sorpresa puesto que no sabíamos nada sobre ella y además según lo comentado va a suponer una cifra brutal en cuanto a capacidades y consumo, puesto que pasamos de 700 vatios con su primera versión a nada menos que 800 vatios en esta segunda.

Este aumento realmente está pensado para lograr más eficiencia, puesto que si tenemos en cuenta que Ponte Vecchio incluye 128 EUs, Rialto Brigde se va hasta los 160 Cores Xe en su haber, un aumento del 25%, lo que dado el incremento de 100 vatios repercute en mayor eficiencia realmente.

En cuanto a rendimiento en sí mismo, Intel asegura que veremos despegar el mismo un 30%, lo cual no es impactante dadas las cifras que hemos expuesto de Cores, pero es un salto adelante en términos generales a falta de ver las frecuencias finales.

Por último y antes de hablar del futuro como tal de esta tecnología, Intel ha puesto como fecha de Sampling 2023 para Rialto Bridge sin especificar trimestre alguno, unas cifras muy parecidas a las de NVIDIA con H100 y sus servidores Grace, donde aquí los de Huang llevan algo de ventaja. Y es que el objetivo de Intel está claro si miramos el roadmap que ha facilitado: 2023 será el año donde llegarán los nuevos Xeon y Rialto Bridge para ya en 2024 o 2025 dar el salto a Falcon Shores, la arquitectura que unirá ambos en un nuevo concepto llamado XPU.

El futuro es Falcon Shores, las XPU que revolucionarán el mercado

Falcon Shores será la implementación con Tiles de forma flexible y escalable, una vuelta de tuerca a lo que hemos visto con los NVIDIA Grace SUPERCHIP donde con EMIB y Foveros 3D Intel da el salto a un solo producto modulable que mediante un solo socket pueda disponer de todo tipo de productos a gusto del consumidor. Desde GPUs, CPUs hasta una mezcla de ambos, un concepto este de XPU que está claro será el dominante en la industria hasta el punto que no descartemos que puedan incluir algunas partes de un FPGA.

Intel da detalles más o menos interesantes, puesto que afirma que con Falcon Shores se aumentará el rendimiento por vatio en hasta 5 veces, la densidad por socket x86 en 5 veces y la capacidad de memoria y B/W en el mismo valor, un concepto que más tarde se importará a PC de manera mucho más simple y sobre todo barata donde por suerte no tendremos tantos cambios como tal (menor precio).

Y es que partimos de una base de CPU y GPU muy decente que solo se verá potenciada por las tecnologías de empaquetado e interconexión modulares, pasando Intel directamente a arquitectura MCM como va a hacer AMD con Zen 4 y sus iGPU.