¿Qué pasaría si os dijésemos que las piezas están dispuestas para un cambio importante en la memoria de los PCs? Uno en el que la memoria NVMe utilizada en los discos SSD y la memoria RAM se irán unificando poco a poco, ya sea utilizando una interfaz de comunicación común o evolucionando a memoria persistente, todo ello gracias al futuro estándar CXL 2.0.

La estandarización del SSD es algo que vamos a ver en los años siguientes, el motivo de ello es porque muchas aplicaciones van a empezar a hacer uso de estas unidades de almacenamiento masivo, las cuales disponen de un impresionante ancho de banda. No obstante todo se puede mejorar y es por ello que os vamos a dar un repaso rápido de hacía donde va a evolucionar el acceso a la memoria NVMe y como esto cambiará la forma en la que los PCs estarán organizados de cara al futuro en cuanto a la memoria.

El acceso a la memoria NVMe desde la CPU en la actualidad

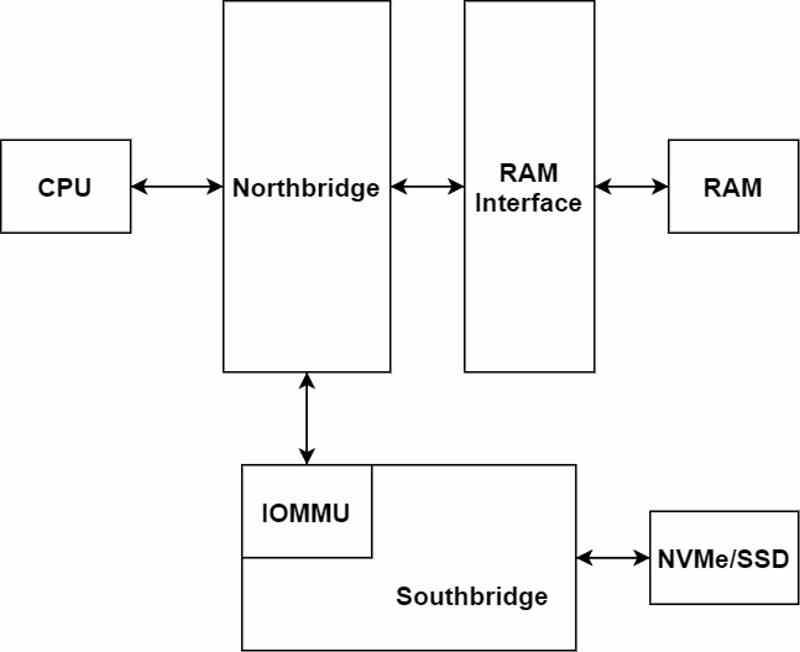

Para entender la actual situación en la comunicación de la CPU con la RAM y la memoria NVMe hemos de tener en cuenta que pese a que el direccionamiento virtual de la CPU incluye toda la memoria del sistema de manera unificada, en realidad de cara al acceso físico tanto a la RAM como al NVMe la cosa no es igual, dado que para acceder a la memoria NVMe es necesario hacerlo a través del IOMMU al encontrarse conectado a la interfaz de E/S del Southbridge.

Esto significa que para acceder a los datos de una memoria NVMe hay una gran cantidad de pasos, lo cual si queremos copiar los datos de la manera más rápida posible desde los chips NVMe del disco SSD hacia la RAM supone una gran latencia, pese al enorme ancho de banda que pueden otorgar las interfaces PCI Express.

Los arquitectos hace tiempo que llevan buscando no solo unificar el espacio de memoria en lo que al direccionamiento se refiere, sino también el acceso a la memoria con tal no solo de reducir la latencia sino disminuir la cantidad de cableado interno por el que mover los datos. Siendo el objetivo principal el de hacer procesadores con comunicaciones menos complejas y de menor consumo energético.

El acceso a la memoria NVMe via CXL 2.0 en el futuro

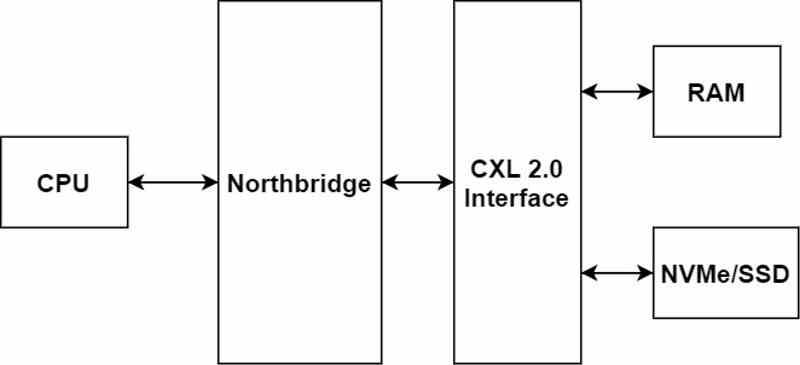

La clave de todo esta en la versión 2.0 del protocolo CXL, el cual va a llevar todos los aceleradores y dispositivos de E/S a un direccionamiento común con la RAM, lo que se traduce en no va a ser necesario el IOMMU y abre la posibilidad de que se pueda acceder tanto a la RAM como a la memoria NVMe bajo la misma interfaz CXL 2.0.

La CPU no accedería de manera directa a los chips NVMe, pero estos a través de la interfaz CXL 2.0 pueden copiar directamente los datos a la RAM del sistema de manera directa sin tener que pasar por el IOMMU y todo el trabajo de la conversión de direcciones.

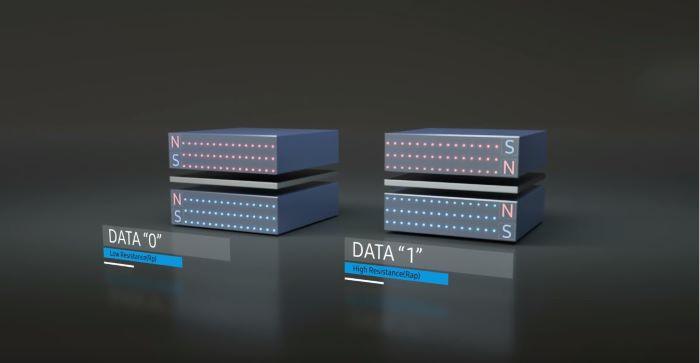

Este paso es importante de cara a la adopción de memorias RAM perpetuas como la MRAM, las cuales mantienen su contenido incluso después de haber perdido la carga eléctrica y que combinan el almacenamiento persistente de las NAND Flash con la velocidad de la memoria RAM.

Obviamente para ello habrá que crear nuevas interfaces de comunicación tanto para la RAM como la memoria NVMe, el motivo de ello es que el consumo energético del puerto PCIe es demasiado alto de cara a los anchos de banda de memoria, es por ello que una futura memoria DDR6 o DDR7 compatible con una interfaz CXL 2.0 no la podemos descartar.

¿Unificación previa de la RAM y los NVMe antes de la memoria persistente?

Tampoco podemos olvidar la existencia de memorias que pese a no ser memorias persistentes, incluyen en tanto la memoria NVMe como la LPDDR en un mismo empaquetado, claro esta que estas memorias no están diseñadas para utilizar la interfaz CXL 2.0, pero dado que los fabricantes de memoria NVMe y RAM son los mismos, entonces no nos debería extrañar ver en un futuro módulos DIMM, SO-DIMM o memoria soldada a la placa que integre tanto la memoria RAM como la NVMe en un mismo empaquetado.

Hay que tener en cuenta que uno de los problemas de diseño más comunes tienen que ver con el espacio, el hecho de integrar la RAM y la memoria NVMe en un mismo espacio se traduce en una reducción del espacio y en sistemas más compactos, obviamente el hecho de unificar ambos tipos de memoria bajo un mismo empaquetado abre la posibilidad de que ambas compartan una misma interfaz de comunicación, la cual viendo la evolución de las cosas va a ser la CXL 2.0, ya que es un estándar común en el que todos los fabricantes están de acuerdo.