¿Cómo afectará a Intel y AMD la litografía EUV para fabricar sus procesadores?

Actualmente estamos viviendo una época donde es posible que muchos no se estén dando cuenta de la revolución tecnológica que se nos avecina y que ya es casi una realidad. Hablamos de los procesos litográficos con litografía Ultravioleta Extrema, también conocida como EUV o EUVL, donde todas las grandes fundiciones están trabajando con ella para seguir avanzando en la miniaturización de transistores, pero ¿está realmente lista para ser una realidad a gran escala en Intel y AMD?

Intel y AMD/TSMC en plena carrera litográfica

Por todos es sabido que hay actualmente dos carreras en el mercado que van estrechamente ligadas y donde ambas están siendo impulsadas por los mismos protagonistas. Hablamos de la carrera por un mayor número de núcleos y por el menor proceso litográfico, donde el binomio AMD/TSMC parece que van a llegar antes que Intel para poner sus productos encima de la mesa y en disposición de los usuarios.

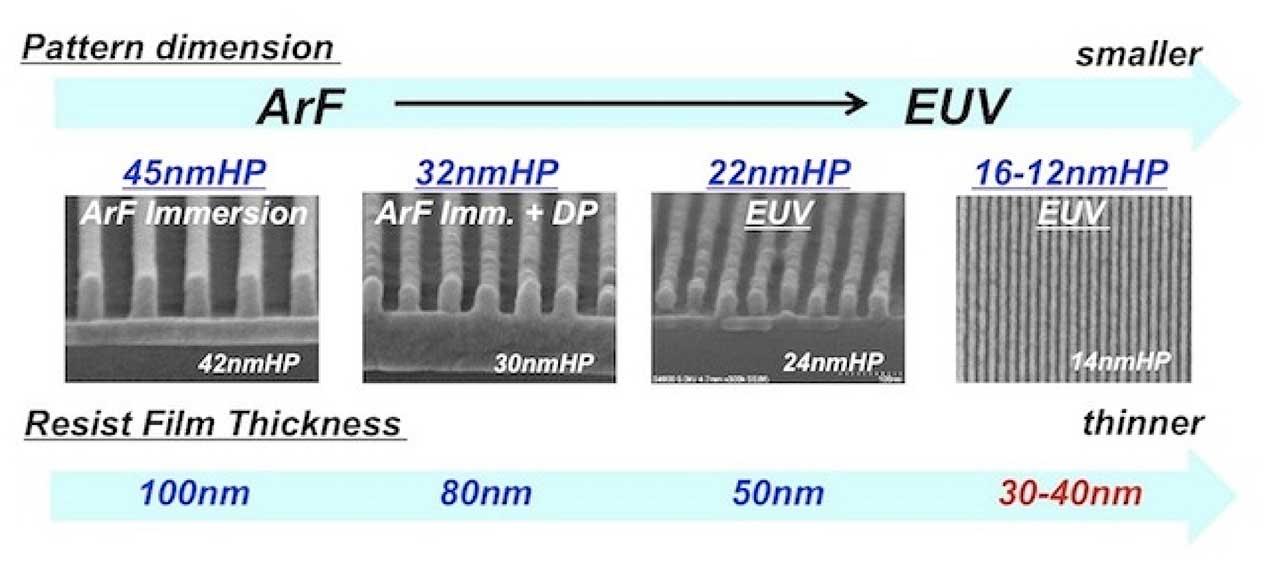

Esto no significa que la apuesta de unos sobre otros sea mejor, pero normalmente en este negocio el que llega primero golpea dos veces, siempre que el trabajo esté correctamente hecho. El paso evolutivo a los 7 nm de TSMC y 10 nm de Intel no podía ser mediante las técnicas actuales de inmersión, por lo que se tuvo que virar hacia un proceso de grabado de nueva factura y donde se necesitaba una mayor simplificación de los procesos.

Dicha técnica es EUV o EUVL, siendo esta última una desviación significativa del estándar EUV común. Con EUV, de la que ya hemos hablado en otros artículos, todo se basa ahora en el uso de patrones simples o multi patrones. El uso de estos es vital a la hora de enfrentar nuevas reducciones litográficas y representan un nuevo desafío aún por resolver en litografías inferiores a los 5 nm.

Por ejemplo, 7 nm EUV necesita un solo patrón para fabricarse, mientras que los 5 nm harán uso de un patrón doble en las capas críticas aun usando EUV. Esto tiene unas ventajas e inconvenientes, ya que por un lado se reduce el número de defectos de la oblea, pero por otro requiere pasos más costosos para conseguirlo, lo que aumenta los costos de diseño de CI, los cuales son actualmente astronómicos. Situándonos correctamente, la litografía tradicional para 7 nm de TSMC y 10 nm de Intel estaba usando patrones de onda de 193 nm, pero esta longitud es demasiado grande para producir litografías de menor tamaño.

EUV y EUVL esperan llegar a unos patrones de onda de solo 13,5 nm, lo cual evidencia la precisión que pueden ofrecer. Por desgracia, pero siendo totalmente lógico, ninguna compañía escogerá un nodo que no les sea rentable económicamente, por lo que las fundiciones principales enfrentan también el reto de mantener unos bajos costes por oblea si quieren adquirir clientes. A día de hoy, ni TSMC ni Samsung ni Intel son rentables en cuanto a obleas/euros, por lo que cuando la tecnología ya se domina, el último paso es hacerla rentable para los clientes.

¿Está EUV y EUVL realmente listas?

Los chips, sea cual sea su naturaleza, están formados por tres partes: transistores, contactos e interconexiones. El transistor es la parte más baja del proceso, ya que funciona como un interruptor como todos sabemos. Las interconexiones por su parte se generan como último paso, estando en la parte superior del estrato y consistiendo en esquemas de cableado de cobre, donde finalmente los contactos son las capas que cada fundición genera en el proceso litográfico.

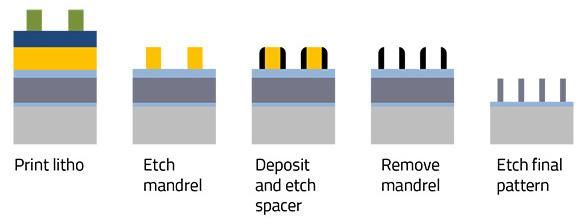

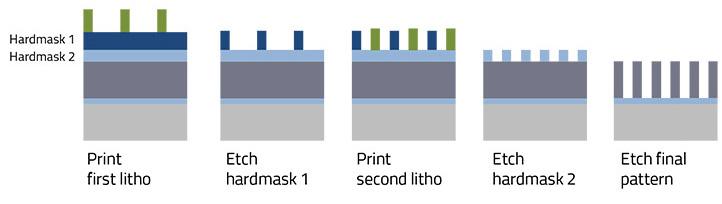

Como es de esperar, mayor número de capas/matrices, mayor complejidad y por lo tanto mayor coste final. Para hacerlo más simple, o al menos simplificar los procesos, se crearon lo que llamamos patrones múltiples, donde las matrices se dividen en dos o más para imprimirlas por separado en un principio y finalmente dibujarlas en orden en la oblea.

Actualmente, el número de capas es enorme y requieren un proceso altamente complicado y costoso, mirando hacia el lado opuesto de lo que buscan los clientes. Por seguir con los ejemplos nombrados, los procesos de 7 nm de TSMC y 10 nm de Intel usan proceso de inmersión con 193 nm y doble patrón, donde el paso mínimo (pitch) es de 38 nm.

Para ello se utilizan dos pasos de litografía y grabado para una sola capa, lo que aumenta la complejidad cuando se van añadiendo mayor número de ellas. En algunos casos, TSMC está utilizando 3 exposiciones para procesar capas críticas en 7 nm, lo que todavía añade más complejidad. EUV hace exactamente lo mismo, pero usando un solo patrón y una sola exposición, por lo que toda la industria quiere implementarla lo antes posible para comenzar de nuevo a ser más rentables.

EUV: o cómo convertir el plasma en luz y longitudes de onda

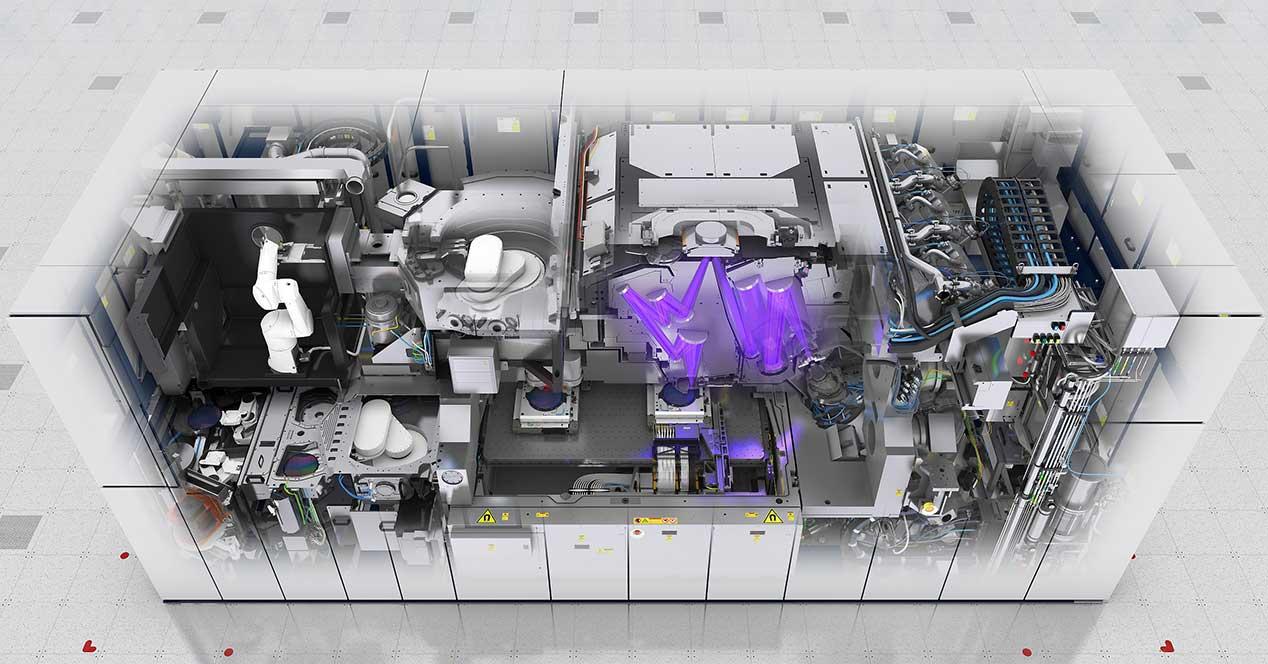

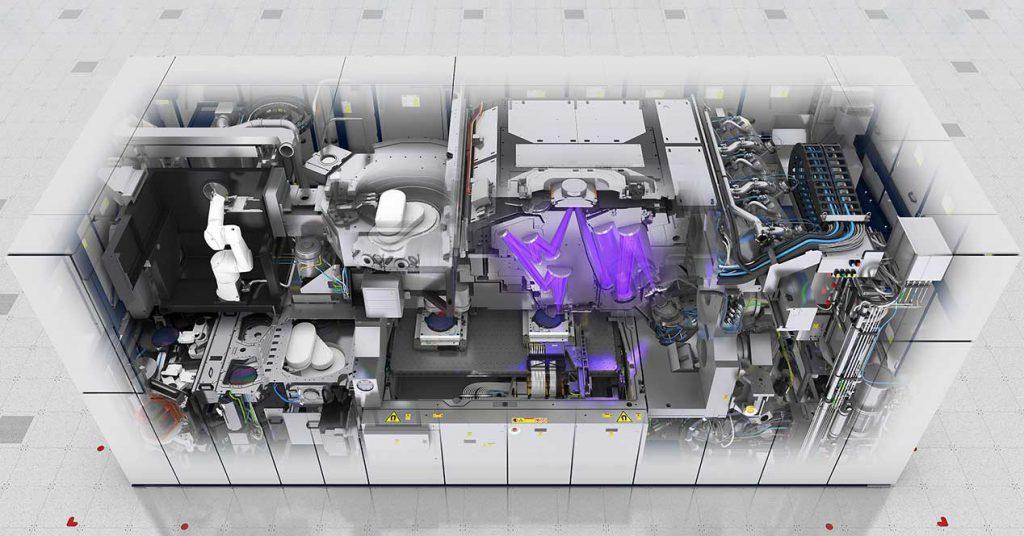

Lo más increíble de esta tecnología es como funciona: una fuente de energía convierte el plasma en luz a longitudes de onda de 13.5 nm, para una vez completado el cambio dicha luz rebota en 10 espejos multicapa dentro de un escáner, donde cada uno de estos espejos absorbe aproximadamente un 30% de la luz incidente que no total.

Por ello, crear un sistema EUV de doble patrón implica dividir un patrón de chips en dos máscaras más simples. Cada una se imprimiría como una capa separada, para luego unirla de la última etapa. Esto será necesario, en teoría, para los 5 nm, donde ya hay rumores de que podrían reducir el pitch a menos de 30 nm.

Esto está generando debate, ya que muchos ingenieros no lo ven posible, no por debajo de 32 nm, lo cual es parte esencial como hemos visto en cuanto a la densidad de los procesos litográficos. Un menor pitch implica una mayor densidad total del nodo, pero como se ha comentado, esto tiene que ser a un coste razonable.

La balanza en la que se mueven los grandes fabricantes es realmente difícil de compensar, ya que si usan más patrones consiguen mayor densidad y menor pitch, pero el costo se dispara. Si usan un patrón único, pueden mejorar algo la densidad, pero mantienen un pitch mayor, aunque más rentable el coste por oblea. Hay pros y contras, pero de igual manera hay interés por parte de muchos en el uso de dobles patrones, ya que algunos buscan reducir los problemas estocásticos.

El problema de más patrones y por lo tanto más capas es el problema de la auto alineación de estas. Más capas requieren esquemas que se auto alineen para reducir con ello el llamado LER o rugosidad del borde de línea. Si las fundiciones no pueden alinear las capas de forma perfecta o al menos con una precisión extrema, el sistema de doble patrón no sería apto.

Todos intentan evitar el uso de patrones triples

El problema es que EUV a cada paso que se reduzca puede llegar a necesitar incluso patrones triples, lo cual dispara actualmente los costos y la dificultad de auto alineación de las capas.

En cualquier caso, EUV ha llegado para quedarse, ahora la industria tiene que trabajar en intentar reducir el tamaño de los transistores, pitch e intentar que todo sea en un patrón simple, aunque como ya hemos visto esto es realmente complicado. En cuanto a las implicaciones en Intel y AMD, parece claro que habrá generaciones de procesadores donde su precio será más alto que la anterior, donde es esperable que la siguiente generación sea más asequible y vuelta a empezar.

Estaremos en un llamado TICK TOCK de precios por oblea que se reflejarán en el precio final de los chips, donde es entendible que empresas como NVIDIA se hayan mantenido en 12 nm ante el poco rendimiento por oblea de chips de gran tamaño en TSMC, o como Intel no ha lanzado sus procesadores de alto rendimiento esperando a tener una tasa de éxito y rendimiento mayor para ser rentables.

AMD por su parte apuesta por los 7 nm mediante inmersión de TSMC con un diseño más simplificado y chips más pequeños para maximizar en la medida de lo posible cada oblea. El futuro con 7 nm+ y EUV volverá a bajar los precios, donde ya la propia TSMC ha afirmado que es muy probable que todos sus clientes pasen a 6 nm antes de sus 5 nm por mantener un patrón simple y un coste mucho más ajustado que el nodo inferior.