Desde las memorias HBM, pasando por los chips 3D NAND, hay multitud de chips en el mercado del hardware que están construidos haciendo uso de lo que en Inglés se llama TSV, siglas que significan «Through Silicon Vias» y se traduce como vías a través del silicio por el hecho que atraviesen verticalmente los chips y permiten la intercomunicación vertical entre ellos. En este artículo os vamos a contar lo que son, cómo funcionan y para qué sirven.

En el mundo del hardware a menudo se suele hablar en términos que tienen que ver con tasas de velocidad, ya sea el ancho de banda de una memoria, los ciclos de reloj de un procesador, cuántas veces hace un procesador un tipo de cálculo por segundo, etc., pero muy pocas veces nos preguntamos cómo se intercomunican los chips entre ellos y si esto tiene alguna importancia.

En este artículo os vamos a hablar de una tecnología llamada TSV, la cual es utilizada para intercomunicar chips, sean del tipo que sean.

¿Qué son las vías a través de silicio o TSV?

Si nos ponemos a observar la mayoría de placas base podremos ver dos cosas: la primera de ellas es que la mayoría de conexiones entre chips son en horizontal, lo que significa que las vías en la placa que envían la señal entre chips se comunican horizontalmente.

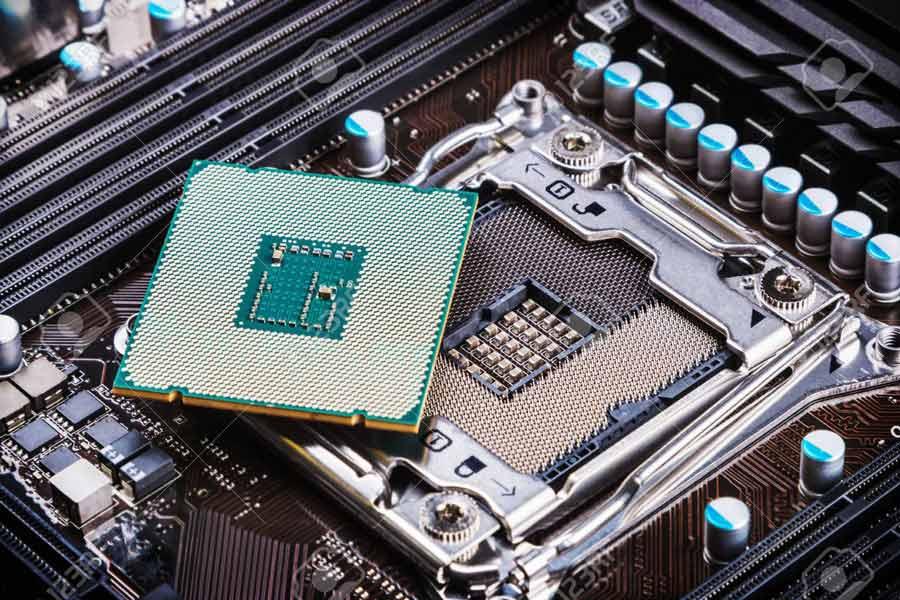

Luego tenemos el caso de las CPUs, las cuales están colocadas encima de un interposer al que llamamos socket y en el que los procesadores se encuentran conectados verticalmente sobre ellos.

Pero en general en el 99% de las veces observamos que no suele haber chips conectados entre sí de manera vertical, y no obstante el diseño de chips y procesadores está evolucionando hacia ese sentido y ya hay algunos ejemplos de este tipo en el mercado. ¿Pero cómo lo hacemos para intercomunicar entre sí dos chips o más en vertical?

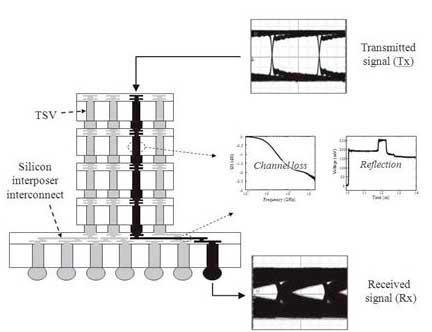

Pues precisamente esto se hace con lo que llamaos vías a través de silicio, las cuales atraviesen verticalmente los diferentes chips o capas del mismo chip que forman la pila, por eso se llaman vías «a través» del silicio porque literalmente pasan a través.

Las aplicaciones y ventajas del uso de los TSV

Una de las aplicaciones del TSV es que permite separar procesadores complejos compuestos por diferentes partes en varios chips diferentes con la ventaja añadida de que la conectividad en vertical permite una mayor cantidad de conexiones, lo cual ayuda a alcanzar mayores anchos de banda sin necesidad de una frecuencia de reloj muy alta que aumente el consumo energético durante la transmisión de datos.

Por ejemplo, en un futuro vamos a ver CPUs y GPUs donde la caché de último nivel de estas estará fuera del chip, con el mismo ancho de banda pero con una capacidad de almacenamiento varias veces mayor, lo que aumentará enormemente el rendimiento. También tenemos el ejemplo del Intel Foveros que utiliza TSV para comunicar las dos partes del SoC Lakefield, el Compute Chiplet con el Base Die donde esta la E/S del sistema.

El motivo de dividir un procesador en diferentes partes está en el hecho de que a medida que un chip es más grande las posibilidades de que haya un error en la circuitería van creciendo cada vez más, y por tanto la cantidad de chips buenos sin fallos que se pueden aprovechar es menor y los que salen bien han de pagar el coste de los que han salido fallidos; esto significa que reduciendo el tamaño de los chips se reduce en teoría el coste en conjunto, aunque luego vamos a ver que la cosa no es totalmente así.

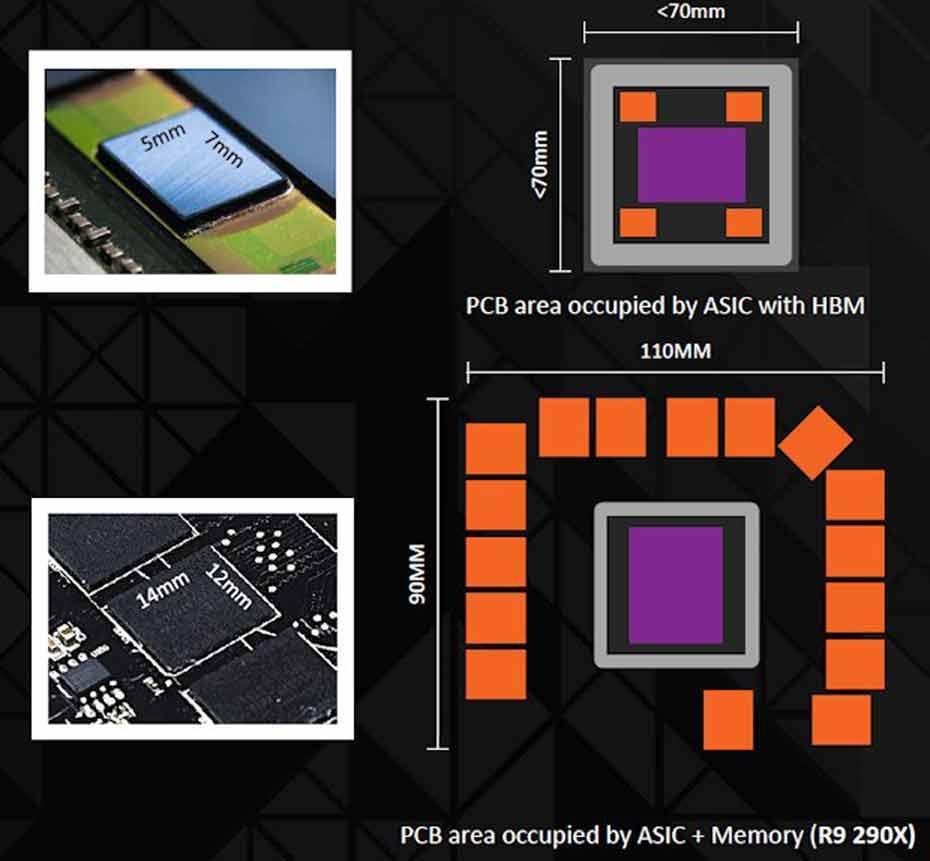

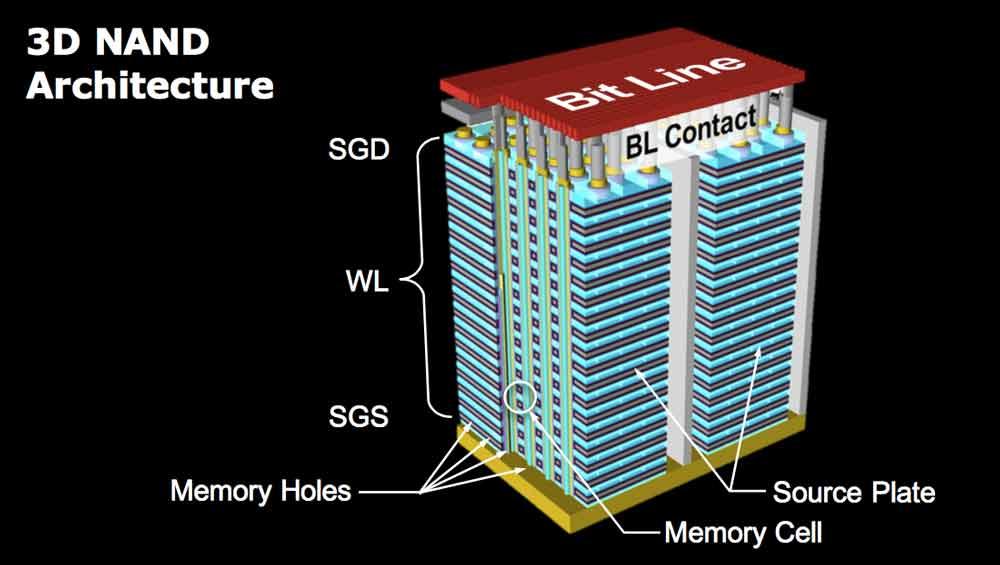

La segunda aplicación tiene que ver con el espacio ocupado; el hecho de poder apilar varios chips en vertical reduce enormemente el área que ocupan, ya que estos no se encuentran desperdigados por la placa, siendo el ejemplo más famoso de ello la memoria HBM utilizada como VRAM para ciertos procesadores gráficos, pero tenemos otros ejemplos como la memoria V-NAND de Samsung, la cual apila varios chips de memoria NAND Flash uno encima del otro.

Otras opciones menos conocidas son la combinación de lógica y memoria, en la que se coloca la memoria encima de un procesador siendo el ejemplo más conocido la memoria Wide I/O, un tipo de memoria que apareció en smartphones hace unos años y que consistía en una memoria encima del SoC interconectada por vías a través de silicio.

¿Por qué la adopción de las vías a través de silicio está siendo tan lenta?

El TSV tiene varios problemas inherentes, lo que ha hecho que pese a ser una tecnología muy prometedora sobre el papel desde hace décadas no acabe de despegar del todo y se haya quedado como una forma de fabricar chips para mercados muy pequeños pero con altos márgenes.

- Su primer problema es que es una tecnología extremadamente cara de implementar que requiere cambios profundos en las líneas de fabricación de muchas empresas, las cuales llevan años haciendo chips sin TSV y para muchas aplicaciones se ha demostrado que el proceso de fabricación convencional es lo suficientemente bueno.

- El segundo problema es que si una parte de la que compone la estructura vertical falla por completo entonces se ha de tirar la estructura entera, y esto hace que los sistemas interconectados vía TSV sean mucho más caros de fabricar. El ejemplo de la memoria HBM es significativo en esto, su coste es tan alto que es inviable como memoria para el mercado de consumo.

- El tercer problema es el ahogamiento térmico, los chips alcanzan las velocidades de reloj que alcanzan bajo ciertas condiciones de temperatura, las cuales se ven afectadas si hay otro chip cercano que también emite calor. Puede que tengamos por ejemplo dos procesadores que por separado llegan a 1 GHz cada uno pero juntos colocados en vertical en una estructura TSV alcancen solo 0.8 GHz cada uno por los problemas de temperatura.

Es el tercer punto el que más preocupa a día de hoy a los ingenieros y se están desarrollando mecanismos de refrigeración para mantener lo más frío posible los chips que forman la pila, para evitar los problemas de ahogamiento térmico.