Si los seis chips de memoria HBM2 para la GPU A100 que NVIDIA presentó hace ya meses os parecieron una exageración, preparaos para ver gráficas para el mercado de la computación de alto rendimiento, HPC, con hasta 12 chips de este tipo de memoria, gracias a que la tecnología para la creación de circuitos integrados en 2.5DIC de TSMC, llamada CoWoS, permite estas configuraciones en su sexta generación.

La memoria HBM, en todas sus variantes y generaciones, se ha convertido en la memoria de los sistemas de alto rendimiento dado que su alto coste no la hace económicamente viable a gran escala para el mercado doméstico; no obstante para el mercado de la computación de alto rendimiento donde los presupuestos son más «holgados» (por decirlo de alguna manera), se ha convertido en la memoria estándar.

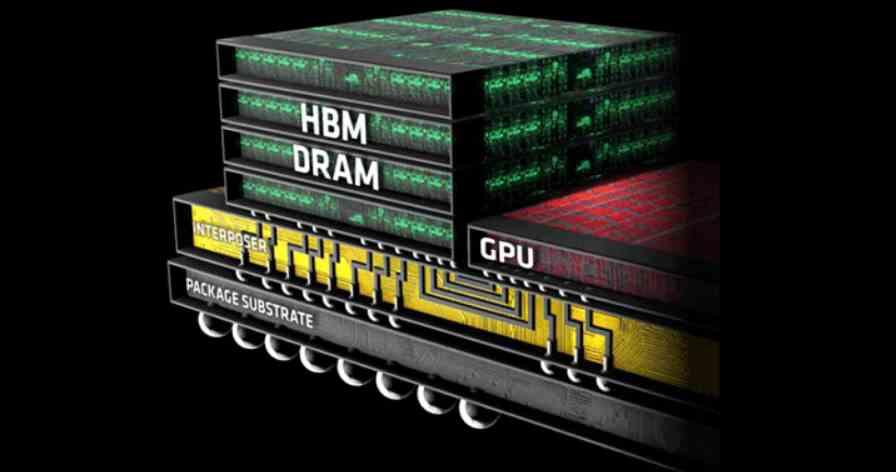

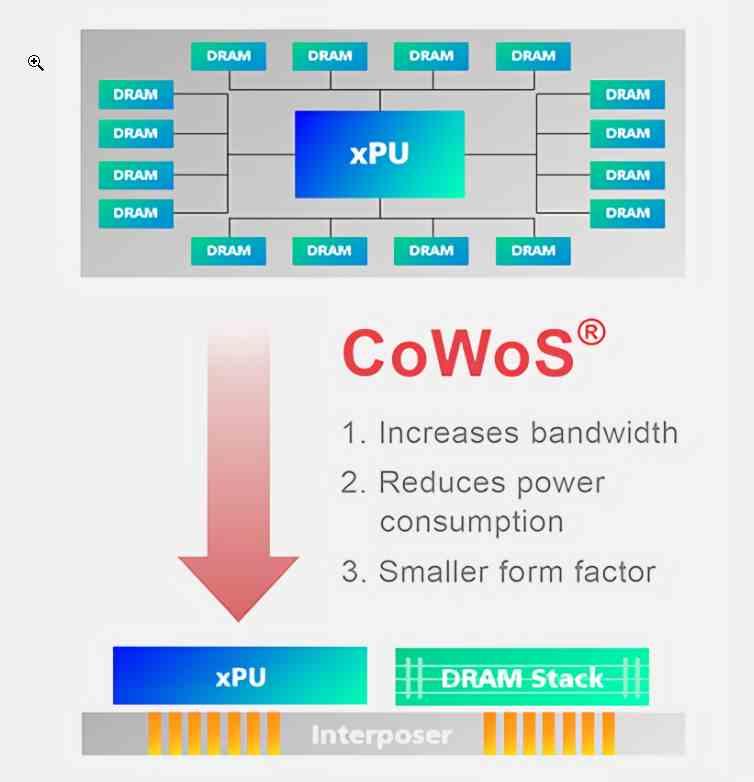

Este tipo de memoria necesita el uso de un interposer para funcionar, el cual va montado encima la GPU y la memoria HBM para la comunicación entre los diferentes elementos del conjunto.

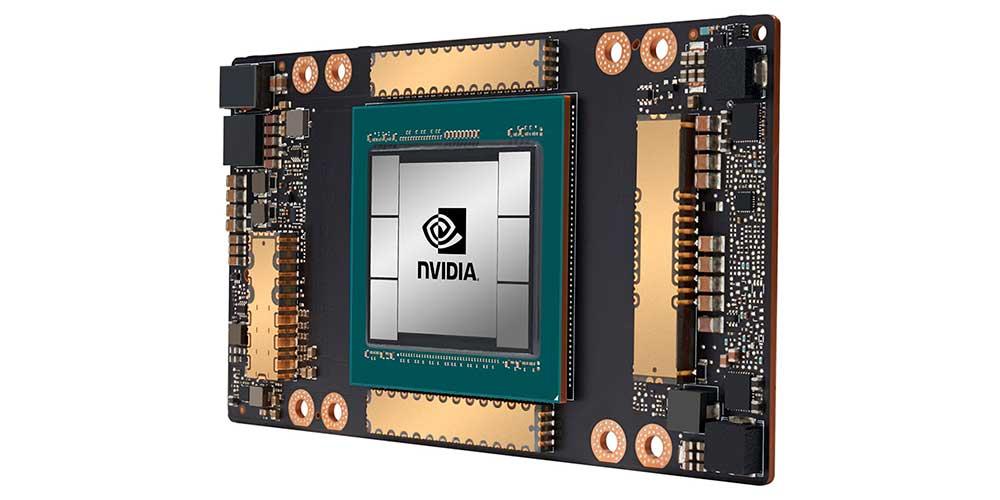

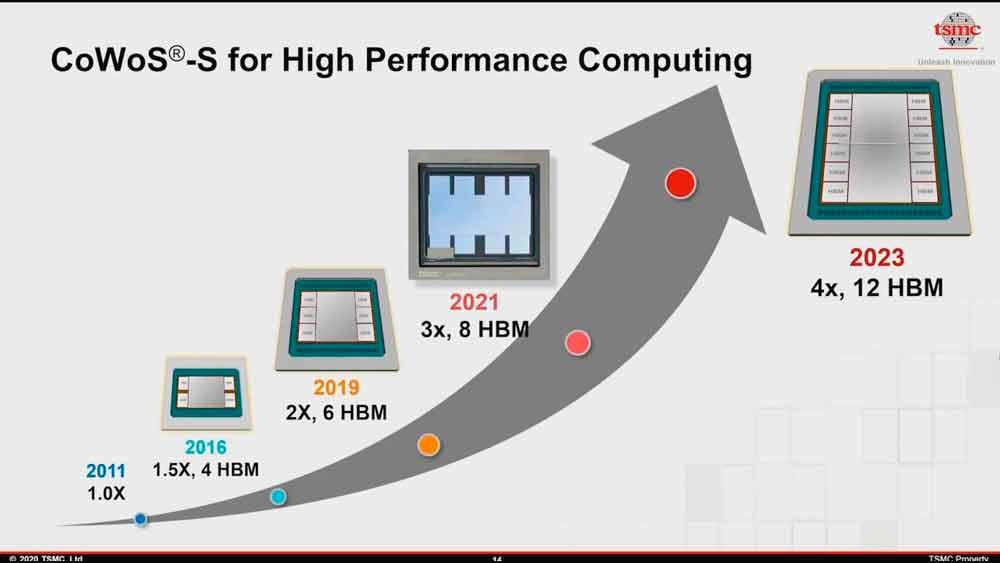

Cada fundición de chips tiene su propia forma de construir los circuitos integrados en 2.5D que es como se llaman este tipo de estructuras, y en el caso de TSMC su implementación recibe el nombre de CoWoS. Con cada nueva generación, la cantidad de chips HBM2 encima del interposer ha ido creciendo a más y más, siendo la A100 de NVIDIA la GPU con más memoria HBM2 del mercado hasta la fecha.

CoWos ha sido ampliamente utilizada para la creación de GPUs de alto rendimiento con memoria HBM por parte de NVIDIA y AMD, y es una tecnología que va a seguir evolucionando, aumentando con ello la cantidad de chips HBM 2 que acompañan a estos mastodónticos y extremadamente potentes chips gráficos.

CoWos de sexta generación: hasta 12 chips HBM2

Los últimos rumores nos dicen que en TSMC la sexta generación de CoWoS, con interposers de hasta 12 pilas HBM2, habría entrado en producción, lo cual es sorprendente por el hecho que la propia TSMC afirmó no hace mucho que estos estaban originalmente planeados para 2023.

Aunque antes veremos en el mercado los interposers con 8 pilas de memoria HBM2, recordad que los chips HBM son memoria apilada en un solo chip y conectada a través de vías de silicio, ya que por el momento no hemos visto ninguna GPU de alto rendimiento con esta configuración y viene antes en el mapa de ruta, seguramente la configuración de la AMD CDNA sea de 8 chips HBM2e.

BFGPUs con hasta 12 chips de memoria HBM2

Sea cual sea la opción va a resultar interesante cuando NVIDIA y AMD muestren sus gráficas para computación de alto rendimiento con 12 chips de memoria del tipo HBM en un futuro, y es que en estos momentos los chips más avanzados de este tipo de memoria tienen una densidad de 16 GB de almacenamiento por pila, por lo que estaríamos hablando de 192 GB de VRAM si ahora mismo estuviese disponible una GPU con 12 chips HBM2e.

Actualmente sabemos que CDNA se va a construir bajo el nodo de 7 nm de TSMC, el mismo nodo que su antecesora Vega 20 y que la A100 de NVIDIA, y aunque por el momento desconocemos de manera oficial la configuración de memoria de las CDNA de primera generación tendría sentido que AMD utilizara 8 pilas HBM2e para CDNA. Por otro lado, creemos que también vamos a ver una segunda iteración de los A100 de NVIDIA, también utilizando 8 chips HBM2e en vez de 6.

La GPU que tiene más posibilidades de utilizar 12 chips de memoria HBM será la que se basará en la arquitectura NVIDIA Hopper, la cual seguramente no vamos a ver hasta el 2022 como mínimo pudiendo ver la luz incluso en 2023, ya que el tiempo que hubo entre la V100 (Volta) y la A100 (Ampere) fueron tres años justos. No olvidemos que Hopper va a ser la primera GPU de NVIDIA que va a ser conformada por un módulo de múltiples chips, y por tanto va a estar construida por diferentes chips en vez de uno solo como ha ido ocurriendo hasta ahora.

En todo caso aún falta un tiempo, y el hecho de que TSMC ya tenga la capacidad para fabricar no significa que lo esté haciendo a gran escala por lo que aún tendremos que esperar para ver las primeras GPUs utilizando 12 chips HBM2.