CoWoS es el nombre de la tecnología de empaquetado 2.5DIC de TSMC, la cual es clave para la construcción de procesadores que hagan uso de memoria HBM. Ya sean estos CPUs, GPUs o APUs. Desde el lanzamiento de las primeras GPU con memoria HBM hasta el día de hoy la tecnología CoWoS-S ha tenido una evolución constante y TSMC ha aprovechado el Hot Chips para hablar de su tecnología CoWoS-S.

La tecnología de empaquetado 2.5DIC de TSMC ha sufrido un avance importante en los últimos meses, en concreto con el lanzamiento de la quinta generación de CoWoS-S. El cual permite integrar procesadores de con interfaces HBM de hasta 8192 bits y por tanto de hasta 8 pilas HBM 2 en el interposer. ¿Los primeros en estrenar el nuevo empaquetado? AMD con su GPU Dual para computación de alto rendimiento Aldebarán o más conocida como AMD Instint MI200.

TSMC nos habla del pasado, presente y futuro CoWoS-S en el Hot Chips

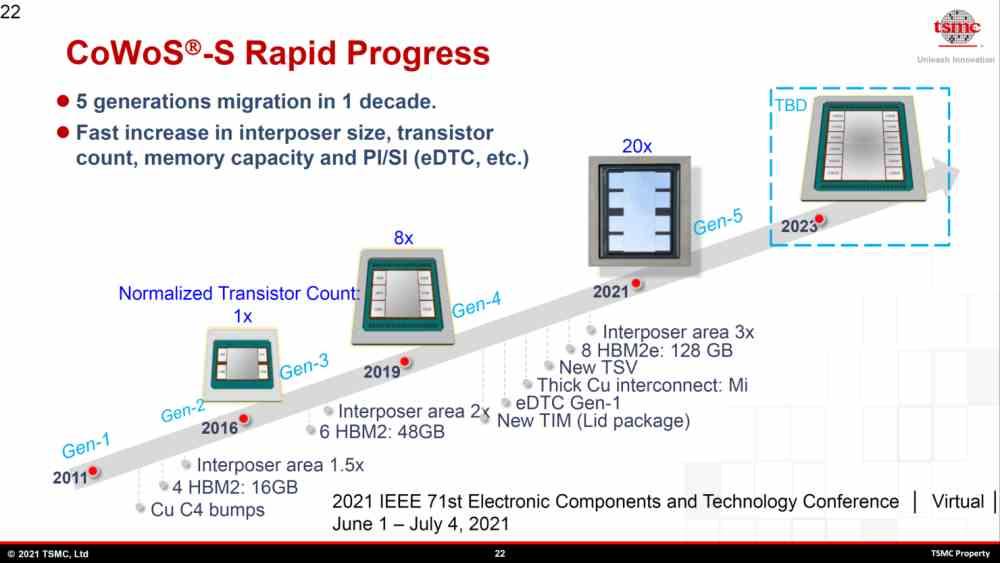

TSMC lleva más de una década desarrollando su tecnología de empaquetado 2.5DIC CoWoS, la cual viene en dos versiones. Por un lado CoWoS-S que hace uso de un interposer de silicio. Por el otro CoWoS-R y CoWoS-L hace uso para la intercomunicación de un puente de silicio. A nivel comercial CoWoS-S fue lanzado a partir de la tercera generación, la cual se lanzó en 2016 con el lanzamiento de las primeras GPU de gama alta con memoria HBM, las cuales se basaron en las arquitecturas AMD Fury y NVIDIA Pascal.

La llamada quinta generación trae un interposer con un tamaño tres veces más grande respecto a los de hace cinco años y 2.5 veces respecto al de cuarta generación. El cual es utilizado por la GPU NVIDIA A100. Este aumento ha permitido que del 2016 al 2021 hayamos visto un aumento de 20 veces la cantidad de transistores en total, un aumento muy por encima del tradicional por la Ley de Moore, pero que ha sido a base de tener estructuras cada vez más complejas. Esto lo han conseguido implementando un nuevo tipo de interconexión llamada Thick Cu Interconnect.

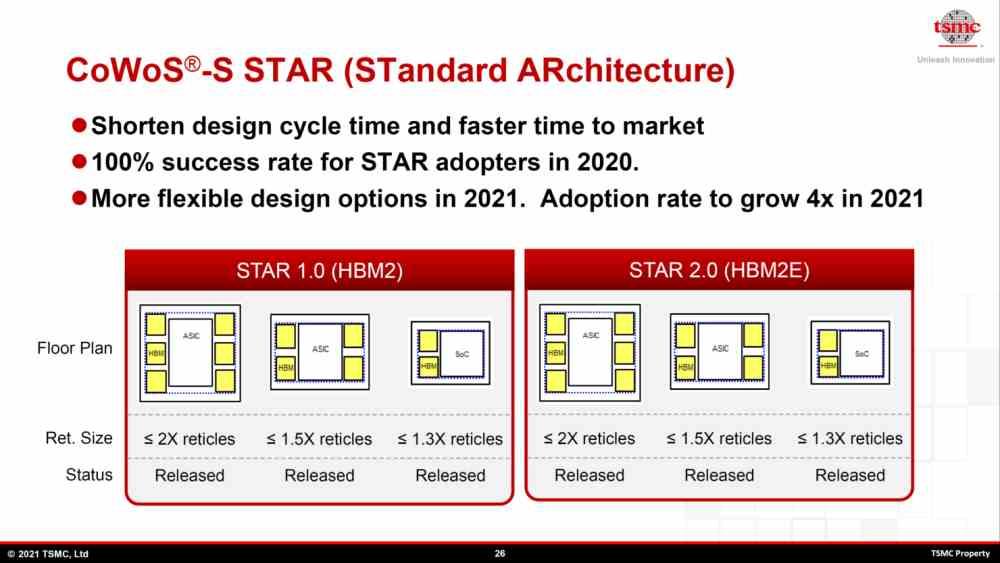

Otra de las novedades tiene que ver con el tiempo de introducción de los diseños basados en CoWoS al mercado, es por ello que han diseñado una solucion semicustom para el diseño de chips bajo el nombre de CoWoS-S STAR. Al ser un diseño semicustom esto le permite a la mayoría de diseñadores de chips no tener que crear su propio diseño y pueden licenciar el de TSMC. Lo que no solo les permite adelantar el tiempo de despliegue al mercado, sino que aumenta la cantidad de compañías que pueden hacer uso de esta tecnología. TSMC espera que la cantidad de sus clientes en utilizar CoWoS-S STAR se cuadruplique.

TSMC se prepara para competir contra Intel en 3DIC y 2.5DIC

Sabemos que Intel va a combinar sus tecnologías EMIB y Foveros en empaquetados sumamente complejos, la prueba de ello es Ponte Vecchio que reúne varias de estas tecnologías. Dado que TSMC es su principal rival e Intel pretende alquilar sus fábricas a terceros pues no se pueden quedar atrás y el futuro pasa en combinar las tecnologías CoWOS de diferentes tipos con la tecnología SoIC. Siendo CoWoS el equivalente a Intel EMIB y SoIC a Foveros.

Por el momento sabemos poco de la sexta generación de CoWoS-S, pero se espera que se aumente de nuevo la cantidad de chips HBM, así como el tamaño del Interposer, pero también veremos la unión de las tecnologías SoIC, ya sea en sus variantes WoW o CoW. También sabemos que TSMC se está preparando para la implementación de la memoria HBM3, cuyo estándar no está terminado.

En todo caso TSMC nos habla de un lanzamiento para 2023. ¿Será esta la fecha de la GPU NVIDIA Hopper? No lo sabemos, pero parece ser que el siguiente en GPUs HPC no lo veremos hasta 2023. Por el momento en la quinta generación de la tecnología CoWoS-S NVIDIA es la gran ausente.