La aparición de los circuitos integrados de dos dimensiones y media, 2.5DIC, trajeron consigo a los llamados interposers de silicio para la intercomunicación de los diferentes elementos que forman parte de los mismos. Debido a su alto coste y complejidad estos se convirtieron en un cuello de botella para la adopción masiva de este tipo de circuitos. Los puentes de silicio son una alternativa que promete solucionar estos problemas.

El mayor desafío en un sistema compuesto por varios procesadores distintos es la comunicación. No obstante existen aplicaciones donde la potencia que requiere el hardware impide colocar la arquitectura en un solo chip y se ha de tirar de una composición más compleja, siendo la más habitual la que llamamos un circuito 2.5DIC.

El problema de los interposers de silicio

Debido a la complejidad de la comunicación necesaria y la necesidad de ahorrar en la transferencia de datos se necesita el uso de interfaces de comunicación complejas. ¿El truco más común? El uso de vías de silicio colocadas en vertical que van desde el interposer y atraviesen los chips en vertical. Esto permite aumentar la cantidad de interconexiones y hacer que cada una vaya a una velocidad de reloj baja, lo cual es sumamente importante desde que el consumo energético crece de manera exponencial con la velocidad de reloj.

El problema de los interposers de silicio es que son extremadamente caros debido al tamaño del interposer, ya que este realmente no es más que un chip sobre el que se montan el resto de chips y además ha de ser de gran tamaño. Por lo que el tamaño del interposer está limitado por la retícula del nodo de fabricación. Con la tecnología actual, el tamaño máximo que puede tener un interposer de silicio es de 30 x 30 mm, por lo que los chips, tanto de memoria como procesadores, han de ser por tanto de menor tamaño que el interposer sobre el que van montados.

Todas estas limitaciones hacen que desde hace un par de años se haya desarrollado una alternativa en forma de los llamados puentes de silicio, los cuales han sido adoptados tanto por Intel como por AMD para sus diseños 2.5DIC presentes y futuros.

¿Qué son los puentes de silicio?

Los puentes de silicio, silicon bridges en inglés, no son una tecnología futurible, ya que ya los hemos visto en productos que han salido al mercado. Dado que la tecnología EMIB e Intel utiliza esta tecnología para comunicar varios chips entre ellos en sus diseños basados en circuitos integrados en dos dimensiones y media.

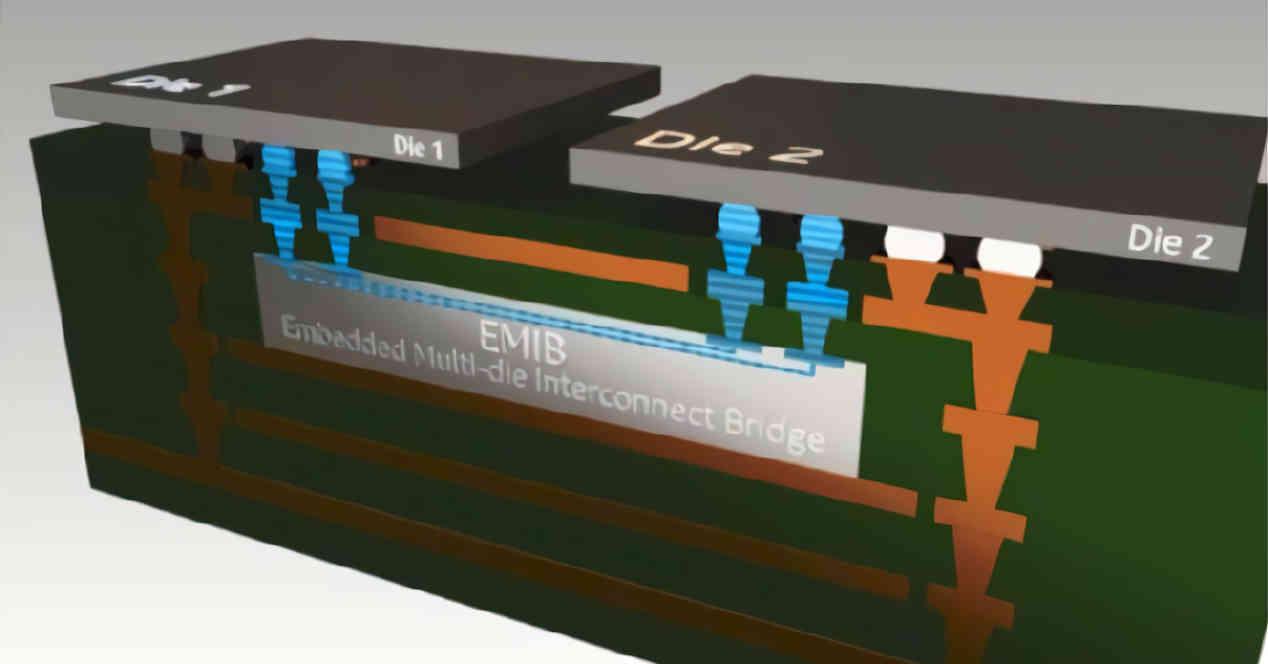

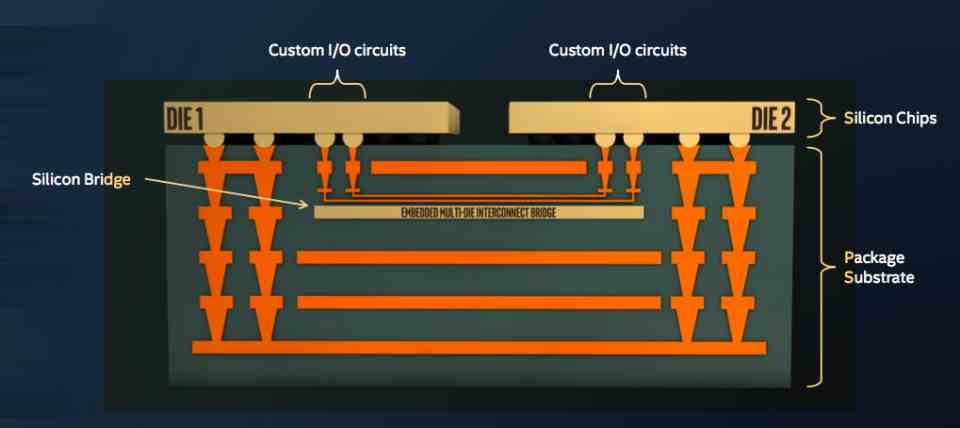

La ventaja de los puentes de silicio es que no utilizan todo un interposer entero para la comunicación, sino que crean un canal de comunicación entre los dos chips que están comunicados que se encuentra en el sustrato de ambos chips. Algo que a simple vista nos puede parecer que es un interposer, pero realmente la cantidad de silicio necesaria para la intercomunicación de los diferentes chips es mucho más pequeña.

Además, los puentes de silicio lo que permite es libertad a la hora de unir diferentes chips entre sí, los creadores no quedan limitados por el tamaño del interposer y tampoco hay una sobrecarga de interconexiones en el interposer que luego hay elementos que no utilizan para comunicarse entre sí. Es por tanto una solución mucho más barata y acerca los diseños 2.5DIC al mercado doméstico y por tanto fuera de la computación de alto rendimiento.

¿Cómo funcionan los puentes de silicio?

Una de las particularidades de los puentes de silicio es que no hacen uso de las vías a través de silicio o TSV para intercomunicarse con los chips, lo cual reduce enormemente los costes, ya que no hace falta crear una serie de vías en vertical que atraviesa todo el chip de arriba a abajo. El problema de adopción de las vías a través de silicio es que es tan complejo como construir un edificio. Y una vez esta este construido decir que tienes que pasar una red de cañerías por el medio, lo que técnicamente supone tener que tirar el edificio al suelo y hacerlo de nuevo.

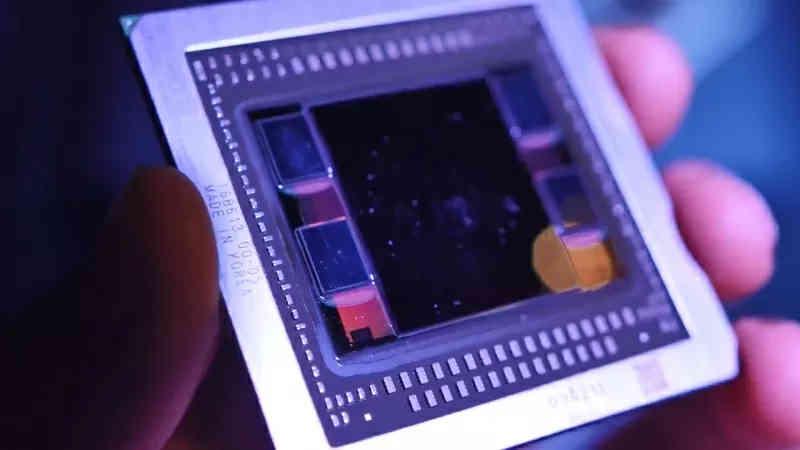

Al igual que con el TSV de los interposers de silicio, los puentes de silicio también se intercomunican verticalmente, pero dicha intercomunicación se hace en un puente que se encuentra entre ambos chips y da el suficiente ancho de banda para la comunicación. Por ejemplo Intel con el lanzamiento de su tecnología EMIB de primera generación pudo comunicar una GPU de AMD con su memoria HBM haciendo uso de uno de los puentes de silicio en Kaby Lake-G.

¿Quiénes lo están adoptando?

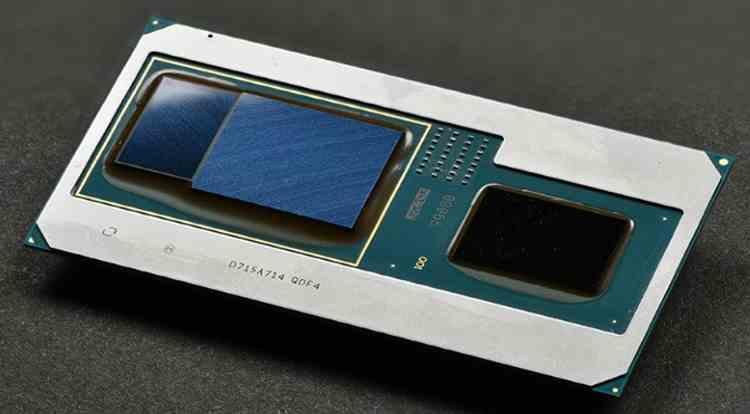

Tanto Intel como AMD están adoptando los puentes de silicio en el desarrollo de futuros productos, aunque como ya hemos comentado antes, Intel ya los adoptó y en concreto fue en un proyecto en conjunto con AMD. Nos estamos refiriendo al NUC Hades Canyon y la forma en la que CPU y GPU estaban interconectadas entre sí a través de un puente de silicio.

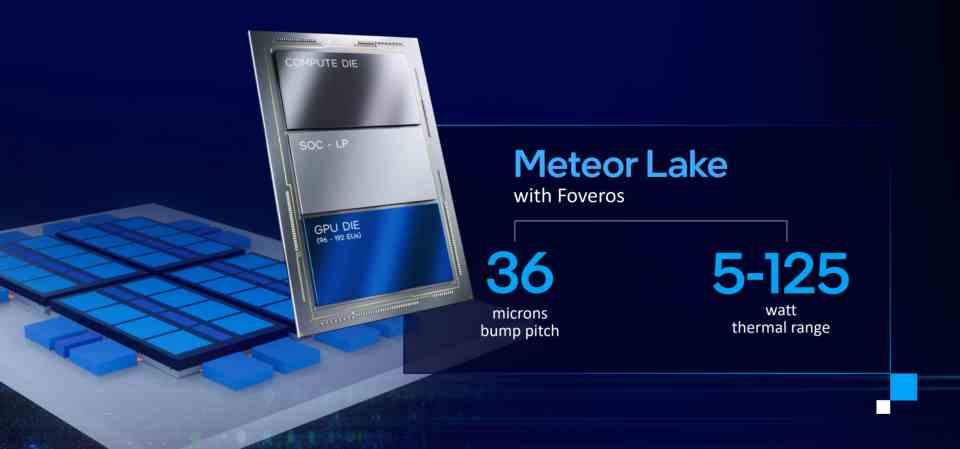

El producto no tuvo mucho éxito, pero Intel ha desarrollado su tecnología de puentes de silicio, EMIB, durante todo este tiempo y lo ha convertido en la forma de interconectar los diferentes tiles, que es como ellos llaman a los chiplets, en diseños tanto de las aún no lanzadas GPU Intel Xe-HP, así como la futura CPU Intel Meteor Lake. La cual esperamos que para 2023 esté en el mercado.

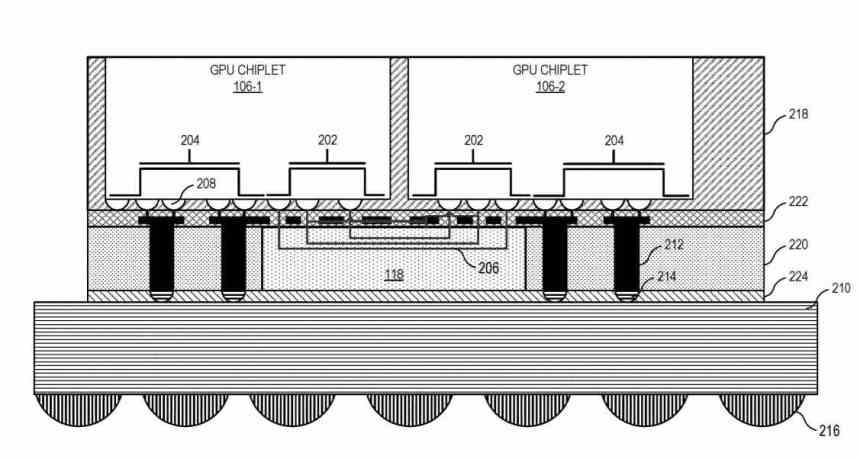

En el caso de AMD en cambio, la adopción de los puentes de silicio la veremos en RDNA 3, cuya referencia la tenemos gracias a una serie de patentes de AMD donde describen una GPU Gaming compuesta por varios chiplets de GPU. Las cuales se ven por el sistema operativo como si fuesen una sola GPU. Curiosamente para la gama de GPUs MCM basadas en CDNA 2, AMD utiliza un interposer común, pero se ha de tener en cuenta que el mercado de la computación de alto rendimiento tiene unos costes que pueden asumir el TSV y el uso de interposers de silicio.

En general se espera que en los próximos años los puentes de silicio sean adoptados por los diferentes fabricantes que quieran construir soluciones 2.5DIC para el mercado doméstico, algo que llevamos años esperando y que será uno de los elementos que solucionará el problema de la subida de costes por el fin de la Ley de Moore. Pero, por el momento y para terminar, nos quedamos con lo siguiente: no se trata de una tecnología no probada y por tanto no estamos hablando de algo de ciencia ficción.