TSMC duplicaría la densidad de transistores con los 5 nm bajo EUV

Las principales fundiciones del mundo no paran ni un segundo, donde actualmente TSMC lidera los procesos litográficos con sus 7 nm. Pero la tecnología EUV pone en jaque a los procesos convencionales y enfrentará a las tres principales potencias: la propia TSMC, Samsung e Intel. Por ello el salto completo a EUV marcará el camino y el éxito futuro, cosa que TSMC implementará con su nodo de 5 nm.

Los 7 nm+ y 6 nm+ no serán fabricados íntegramente en EUV

Todo salto generacional y de innovación sufre diferentes pasos a seguir y donde normalmente todo es paulatino en el tiempo. No es normal ver a empresas como Samsung dar un salto de rendimiento tan grande y quedándose casi un año en la estacada para retomar con más fuerza, donde en el caso de Intel van incluso más despacio en este sentido.

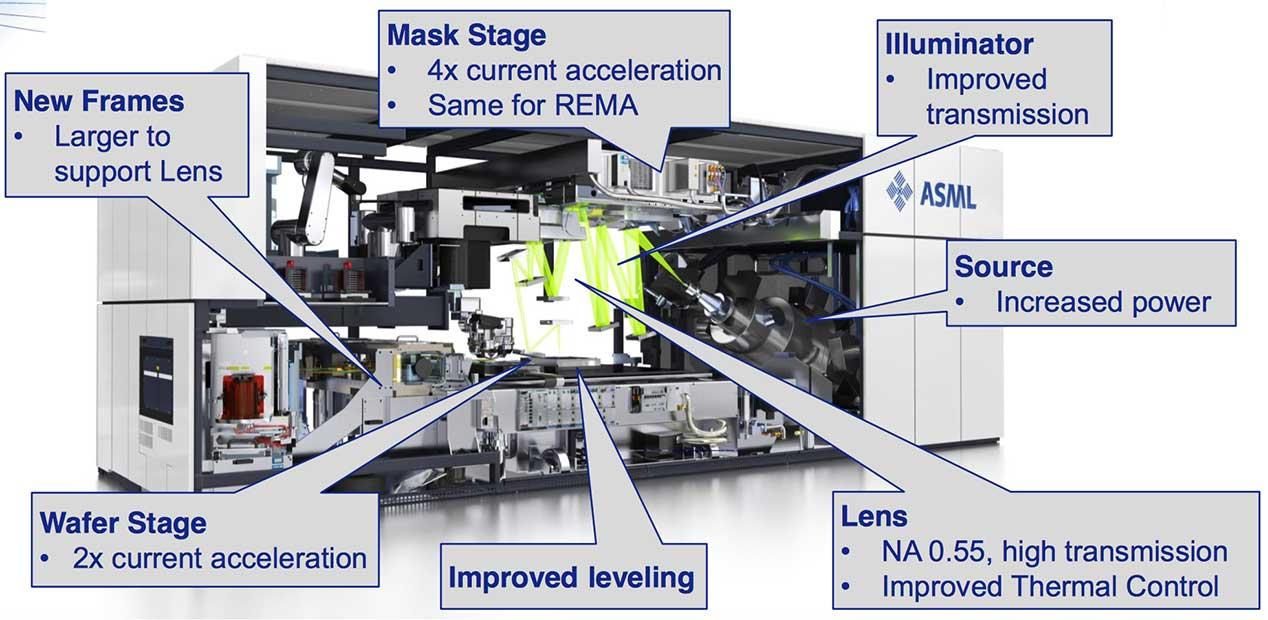

Mucho hemos hablado de la tecnología EUV y de los procesos litográficos de transistores que la incluirán, donde estos deben de reducir el precio de las obleas y lograr importantes saltos de rendimiento. Siguiendo con TSMC, por lo que sabemos su nodo de 7 nm+ llegará al mercado en breve y será el primer proceso litográfico en incluir EUV en su haber, pero solo parcialmente.

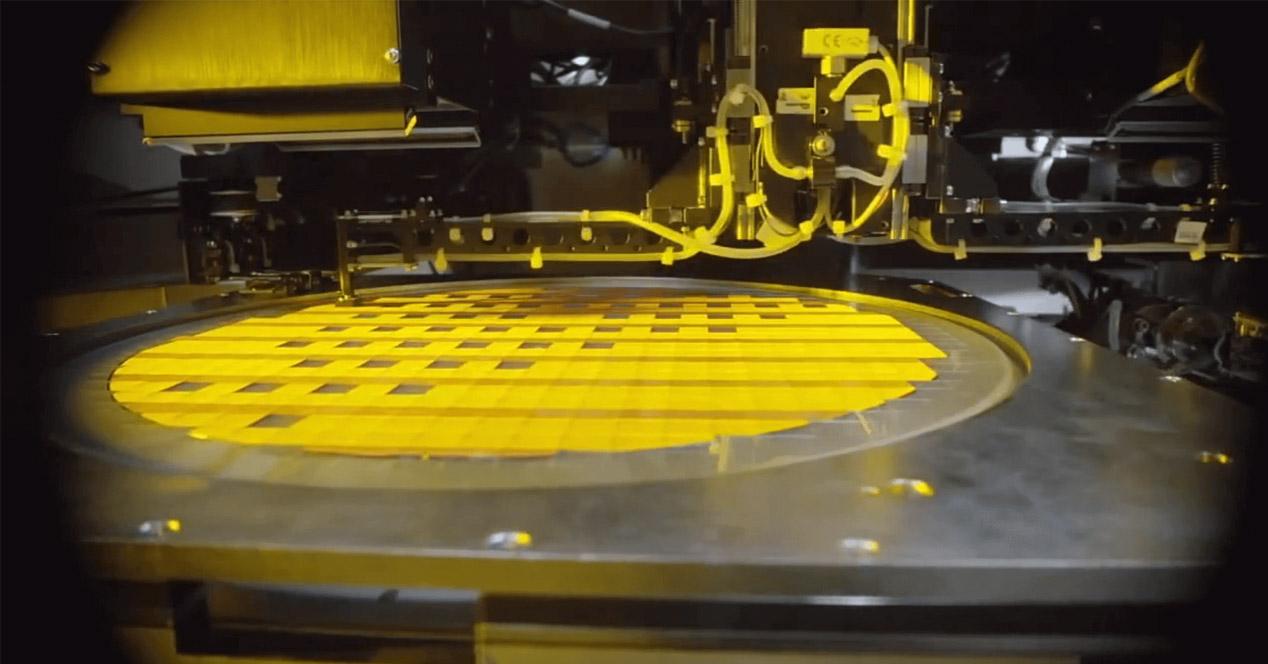

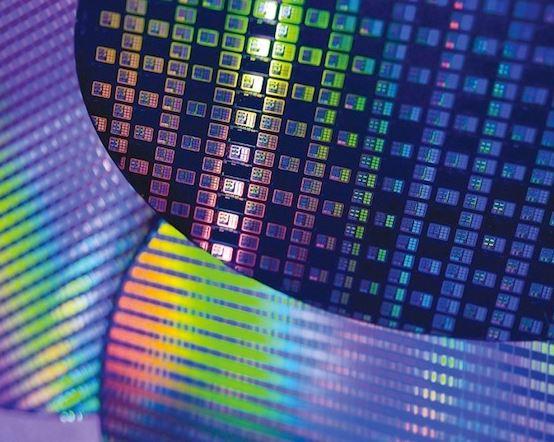

Y esto es así debido a que TSMC solo introducirá dicha tecnología en algunas capas de su proceso litográfico, por lo que estos 7 nm+ que debutarán con el nuevo procesador A13 de Apple para su iPhone 11, es un proceso mixto y no íntegro de EUV. Por ello, la compañía lleva meses innovando de cara a poder completar obleas puramente fabricadas en EUV y no sucedáneos trabajados con las tecnologías wafer comunes.

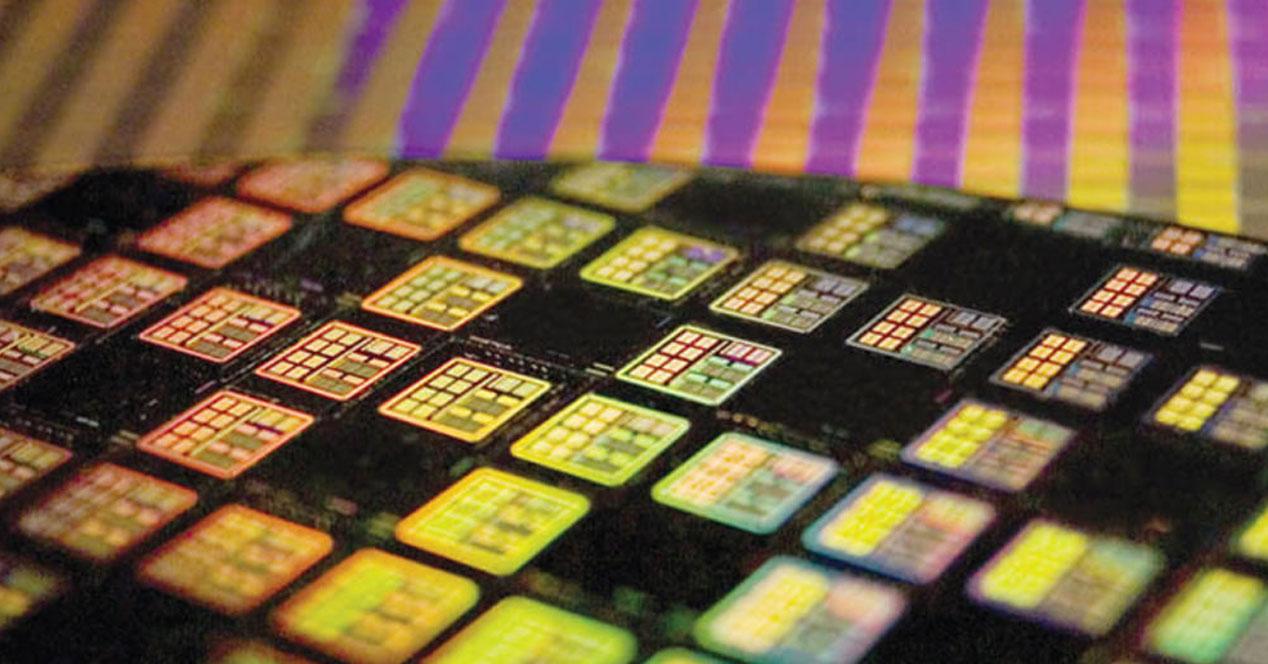

A este tipo de nodos se les denomina como «completos«, es decir, nodos realizados íntegramente con una misma técnica de producción litográfica desde su inicio hasta su fin. Hoy sabemos que el nodo de 7 nm que actualmente vende TSMC será el último completo por inmersión tradicional y que el primer completo con EUV será el de 5 nm de la compañía.

TSMC trabaja en 4 nodos actualmente: 7 nm (N7), 7 nm+ (N7P), 6 nm (N6) y 5 nm (N5)

A diferencia de Samsung o Intel, que van a apostar más claramente por EUV de forma directa y en menores saltos litográficos, TSMC está exprimiendo el llamado diseño DUV. Por ello, tras los 7 nm+ que tendrán como principales valedores a AMD y Apple en primera instancia, llegará poco después su nodo a 6 nm, siendo este la primera implementación real de EUMC.

Todo gracias a que N6 es totalmente compatible en diseño e IP con N7, siendo un paso intermedio hacia EUV, donde las mejoras de este nodo se cifran en una densidad un 18% mayor frente al N7+, lo cual evidencia que estamos hablando de un posible salto de rendimiento bastante interesante. La producción, según TSMC, comenzará en algún punto del 2020, por lo que todo está muy avanzado en este nodo.

En cambio, y como curiosidad, la llamada «Risk Production» del nodo de 5 nm va por delante de lo ofrecido por los 6 nm. Esto no quiere decir que se lance o se tenga listo antes, sino que han estimado que el proceso en tiempo para depurarlo llevará más meses que en el primer caso. Así, TSMC espera tener su primer proceso íntegro EUV a 5 nm para 2021, donde la producción entrará en aumento a finales de 2020, siendo el verdadero sucesor de los 7 nm actuales y obteniendo el doble de densidad frente a este con un 15% más de rendimiento o en cambio reduciendo el consumo un 30%.

Esto evidencia que N7P y N6 son sucedáneos de lo que veremos en poco más de un año, y es que el salto real es N5 y N5P, el cual introducirá FEOL y MOL como optimizaciones litográficas, mejorando otro 7% el rendimiento o un 15% el consumo.