Como sabéis, los chips que utilizamos en nuestro día a día como pueden ser los procesadores de PC están conformados en su mayoría por transistores, unos transistores que siguiendo la ley de Moore son cada vez más pequeños para poder aumentar la densidad (meter mayor número en el mismo espacio), pero los ingenieros llevan tiempo con dificultades para poder llevar esto a cabo. Intel tiene la que parece ser la solución: transistores apilados en nanoplacas, y en este artículo te vamos a contar en qué consiste y cómo, gracias a ello, lograrán no solo mantener sino alargar durante mucho tiempo la ley de Moore.

La ley de Moore nos dice que aproximadamente cada dos años se duplica el número de transistores en un microprocesador, y para hacer esto lo que se lleva décadas haciendo es reducir el tamaño de estos transistores, cuyo tamaño es del orden de nanómetros. No obstante, cada vez es más complicado hacerlos más pequeños y para poder seguir integrando más en el mismo espacio han tenido que buscar técnicas alternativas como la que hoy vamos a contaros.

¿Qué son los transistores apilados en nanoplacas?

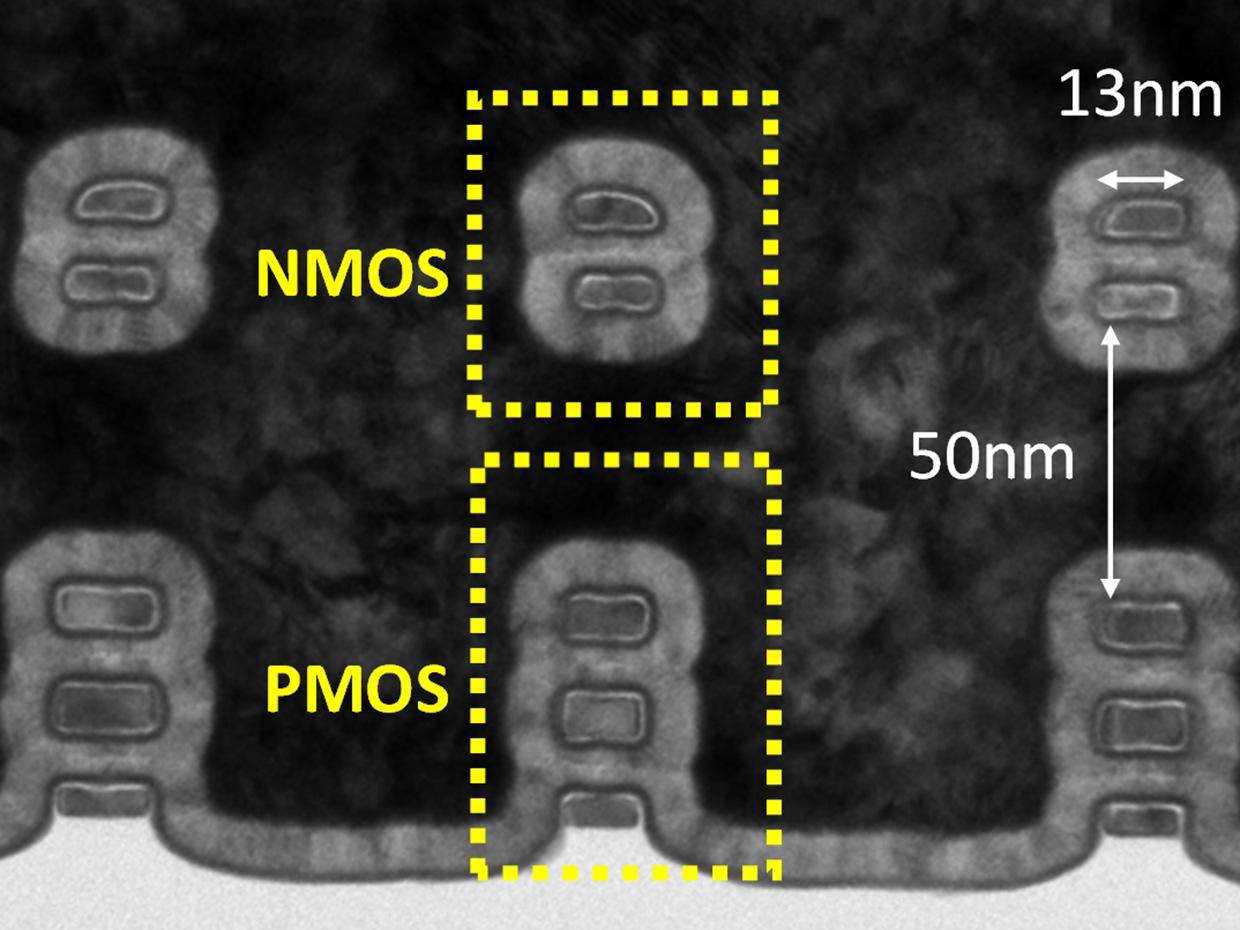

Los circuitos lógicos detrás de casi todos los dispositivos digitales actuales se basan en un emparejamiento de dos tipos de transistores: NMOS y PMOS. La misma señal de voltaje que enciende uno de ellos apaga el otro, y ponerlos juntos significa que la electricidad debe fluir solo cuando un bit cambia de valor, reduciendo en gran medida el consumo de energía.

Estos pares han estado colocados el uno al lado del otro durante décadas, pero si los circuitos electrónicos deben seguir reduciéndose tendrán que acercarse todavía más. Ahora Intel ha mostrado una aproximación diferente sobre cómo colocar los transistores: apilando uno encima del otro. El esquema reduce efectivamente a la mitad el espacio que ocupan los transistores en un circuito CMOS simple, lo que significa que se puede duplicar la densidad de transistores que tiene un chip fácilmente.

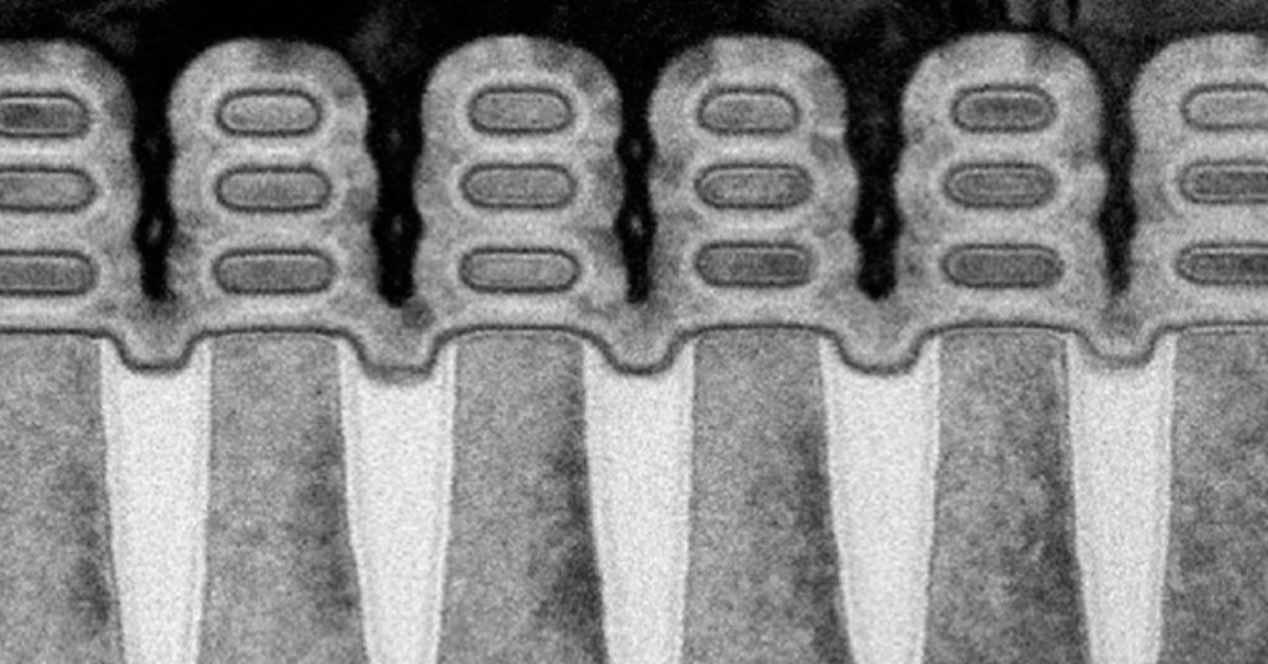

El esquema comienza utilizando lo que se acepta ampliamente como la estructura de transistores de próxima generación, denominada de diversas formas: nanoplacas, nanohojas, nanocintas, nanocables… o simplemente GAA (gate-all-around). En lugar de que la parte principal del transistor consista en una aleta vertical de silicio como se hace hoy en día, la región del canal de la nanoplaca consta de múltiples hojas horizontales de grosor nanométrico apiladas una encima de otra (podéis verlo claramente en la imagen de arriba).

¿Cómo se implementa este tipo de circuitos?

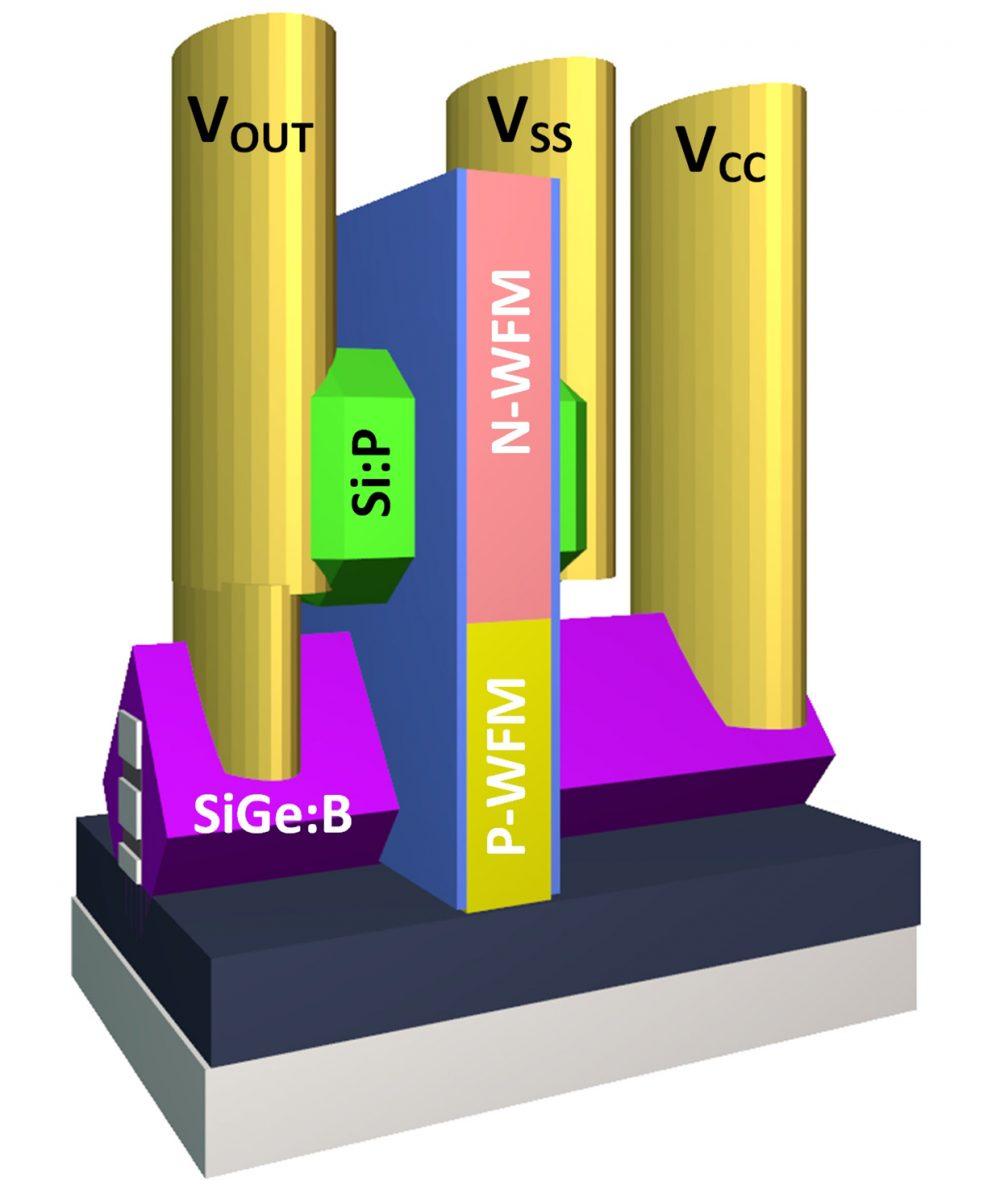

Los ingenieros de Intel utilizaron estos dispositivos para construir el circuito lógico CMOS más simple: un inversor. Requiere dos transistores, dos conexiones de alimentación, una interconexión de entrada y otra de salida. Incluso cuando los transistores se colocan los unos al lado de los otros como se hace hoy en día, la disposición es muy compacta, pero al apilar los transistores y ajustar las interconexiones el área se reduce a la mitad.

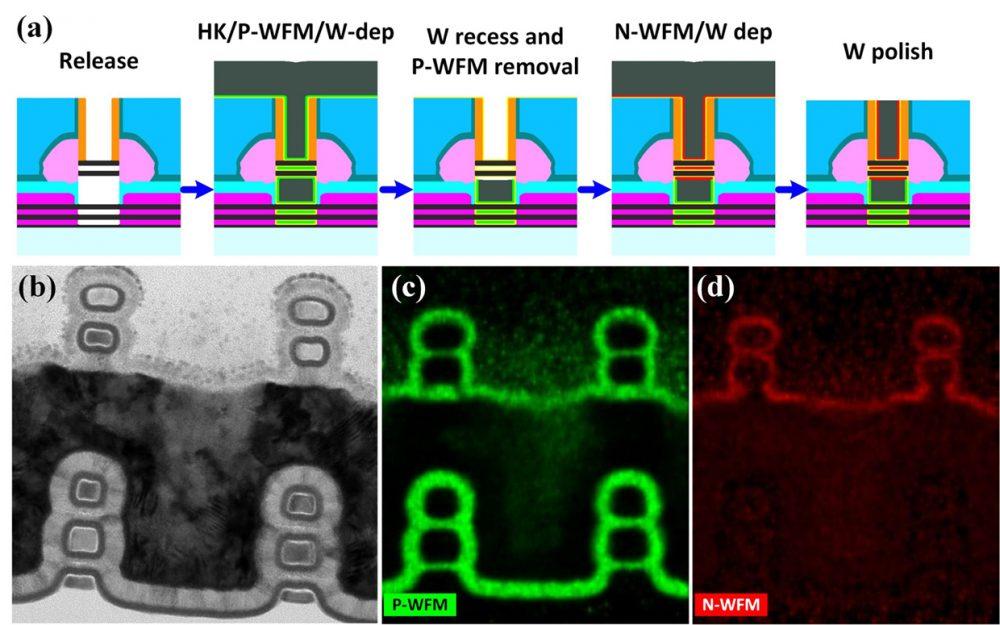

La receta de Intel para crear estos transistores apilados en nanoplacas se denomina proceso autoalineado porque construye ambos dispositivos durante el mismo paso de la producción. Eso es importante porque agregar un segundo paso, digamos construyendo dos obleas separadas y luego juntándolas, podría conducir a desalineaciones que destruirían el circuito.

En esencia, el proceso es una modificación de los pasos involucrados en la fabricación de transistores de nanoplacas. Comienza con capas repetidas de silicio y germanio de silicio, que luego se talla en una aleta alta y estrecha y el germanio de silicio se graba para dejar un conjunto suspendido de nanoplacas de silicio. Normalmente, todas las nanoplacas irían a formar un solo transistor, pero aquí las dos nanoplacas superiores están conectadas a silicio dopado con fósforo con el objetivo de formar un dispositivo NMOS, y las inferiores a germanio de silicio dopado con boro para producir PMOS.

El «flujo de integración» completo es, por supuesto, más complicado (lo podéis ver en la imagen de arriba), pero los investigadores de Intel han trabajado para mantenerlo lo más simple posible (según Robert Chau, director de investigación de componentes de la compañía). Una vez que dominen la técnica de fabricación, que es el punto en el que están ahora, el siguiente paso será ir tras la actuación.

EWs probable que eso implique mejorar los dispositivos PMOS, que en este momento están a la zaga de los NMOS en cuanto a su capacidad para impulsar la corriente. La respuesta a ese problema es la introducción de tensión en el canal del transistor, según Chau. La idea es distorsionar la red del cristal de silicio de tal manera que los portadores de carga (agujeros en este caso) pasen más rápido. Intel ya introdujo tensión en sus dispositivos en 2002, y en varios documentos de investigación la compañía ya mostró que es posible producir tensión de compresión y de tracción en transistores de nanocintas.

Otras organizaciones de investigación también están trabajando en diseños de transistores apilados en nanoplacas, aunque a veces se les llama FET complementarios o CFET. La organización belga Imec fue pionera en el concepto CFET e informó sobre su construcción ya en 2019, pero los componentes de Imec no se hicieron completamente a partir de transistores de nanoplacas sino que la capa inferior consistía en un FinFET y la parte superior una única placa. En Taiwán también informaron de la producción de una estructura CFET que tiene una sola hoja nanométrica para PMOS y NMOS (por el contrario, la de Intel tiene un NMOS de dos placas encima de un PMOS de tres, con un aspecto que probablemente esté más cerca de este concepto de transistores apilados).