El diseño de AMD para Zen 2 ha sorprendido a muchos, pero realmente es un paso lógico para ser más eficientes en varias áreas clave. Aunque no se han mostrado datos de rendimiento por parte de los de Lisa Su, es fácil suponer que los problemas de Zen y Zen + se han solventado en gran manera, pero ¿entonces por qué AMD separa el I/O de sus núcleos en Zen 2?

AMD escoge el camino más eficiente y sencillo

Aunque pueda parecer lo contrario, AMD ha escogido el camino más sencillo para realizar su arquitectura pero sobre todo el más eficiente, aunque hay que matizar que sencillo lo podríamos poner entre comillas y explicaremos el por qué.

Es de sobra conocido que AMD junto con TSMC van a impulsar el proceso litográfico a 7 nm, se podría resumir brevemente en: mientras uno diseña el otro construye.

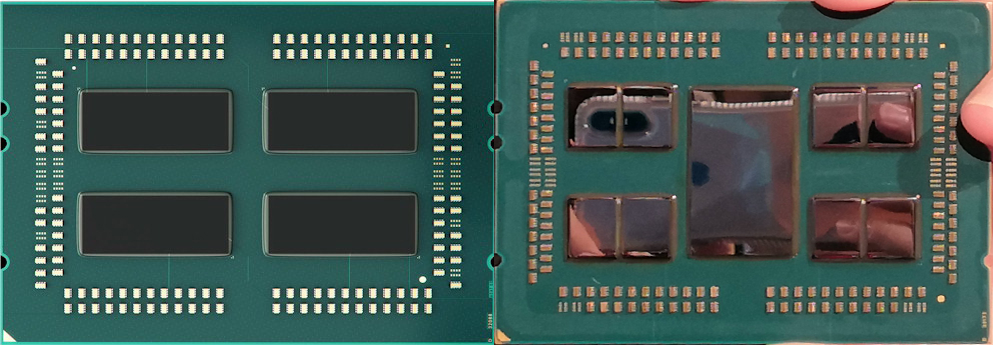

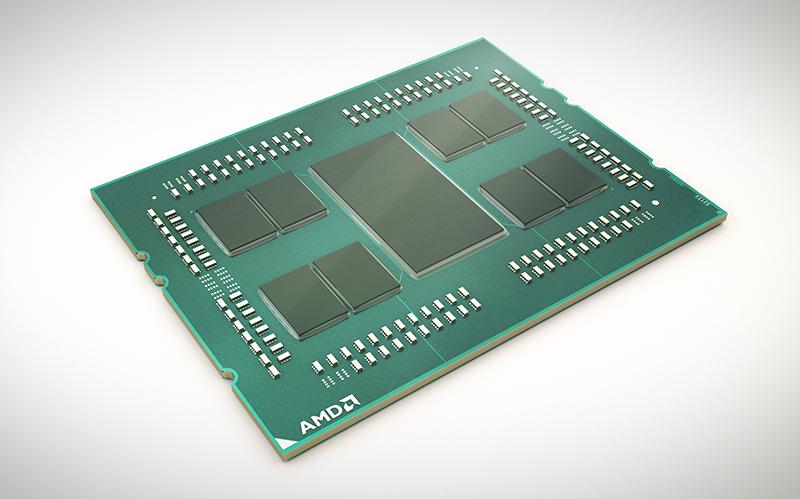

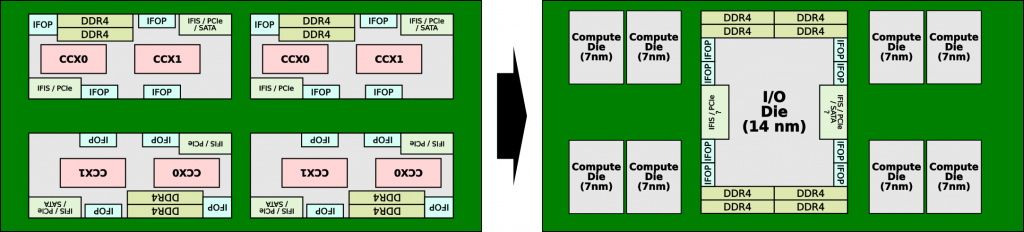

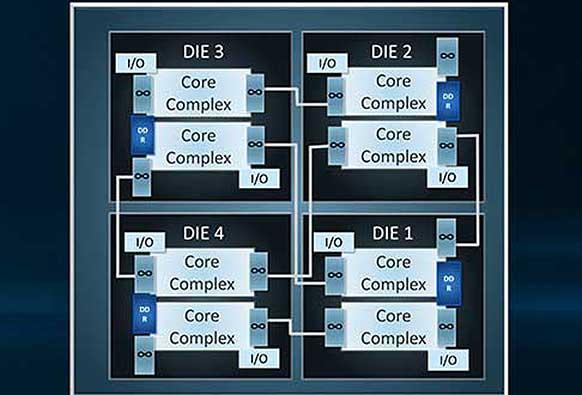

El sistema que está usando AMD en sus arquitecturas Zen no ha cambiado, sus MCM serán piedra angular durante muchos años y por lo tanto lo que veremos son evoluciones del mismo, tal y como podemos ver en las siguiente imágen entre Zen y Zen 2:

Hemos pasado de unos núcleos totalmente completos a un diseño donde parte de los componentes (y con ello funciones) han sido depositadas en un chip externo a ellos dentro del mismo PCB.

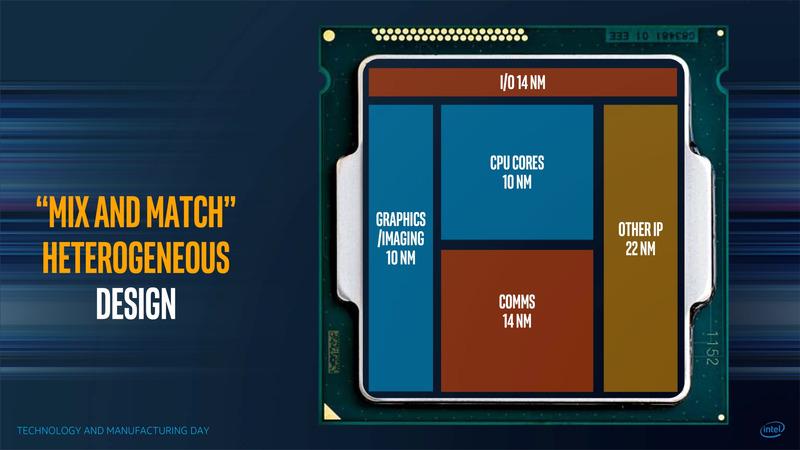

Este diseño puede parecer un paso atrás en un principio, ya que si la lógica impera debe ser más rápido trabajar con unidades de cómputo completas en un mismo die que tener que trasladar los datos a un segundo chip, pero entonces ¿por qué Intel, rey de las CPU monolíticas, planea algo similar con sus 10 nm?

¿Dónde están las ventajas de este sistema de I/O externo y cuáles son los problemas?

Empecemos por los problemas e intentaremos solventarlos sobre la marcha para terminar con sus ventajas, ya que este tema es muy extenso y en algunos puntos se complementa con otros artículos que hemos hecho de forma extensa.

El principal problema que impulsa a los dos grandes fabricantes de chips x86 a tomar este camino no es más que el costo de los chips monolíticos. En el caso de AMD es todavía mucho más grave ya que no dispone del capital de Intel ni de las ventas del mismo.

Si nos atenemos a la Ley de Moore, donde se dijo que cada dos años se duplicaría el número de transistores, podemos entender que como ya adelantó el propio Moore, dicha ley está actualmente muerta.

El problema es que las necesidades son básicamente las mismas: dependemos del número de transistores en casi toda su totalidad para aumentar el rendimiento. Para lograr esto es necesario lograr procesos litográficos de menor tamaño, reduciendo en ello el tamaño de los transistores y por ende en menos espacio podremos incluir mayor número de ellos.

Esto implica el desafío de mayor calado que existe actualmente en el mundo de la informática en general, no ya por la reducción del proceso litográfico en sí, sino por los costes que ello implica.

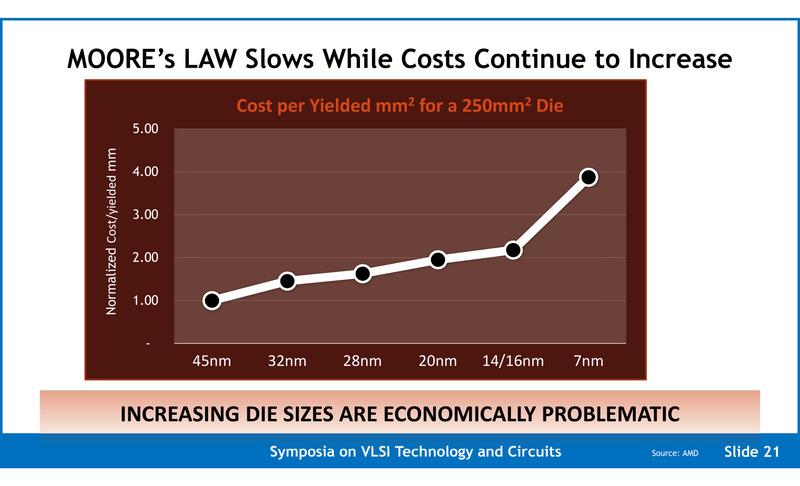

Como se puede apreciar, de los 14 nm actuales en los que nos encontramos (los 12 nm LPP son solo una mejora en eficiencia de los 14 nm en TSMC) a los 7 nm donde AMD y TSMC han llegado hay casi una duplicidad en el costo. Esto quiere decir que a mismos milímetros físicos en un die el costo por rendimiento alcanzado es el doble.

Si miramos desde los 45 nm, el costo se multiplica por 4, lo cual es bastante esclarecedor.

¿Cómo van a conseguir AMD e Intel bajar el costo?

Para entender cómo van a conseguirlo tenemos que centrarnos en las tecnologías que permiten la grabación de los procesos litográficos en sí mismos. El problema de los costos, como siempre suele pasar, es la falta de tecnología para conseguir una reducción de nanómetros sin que se dispare el precio.

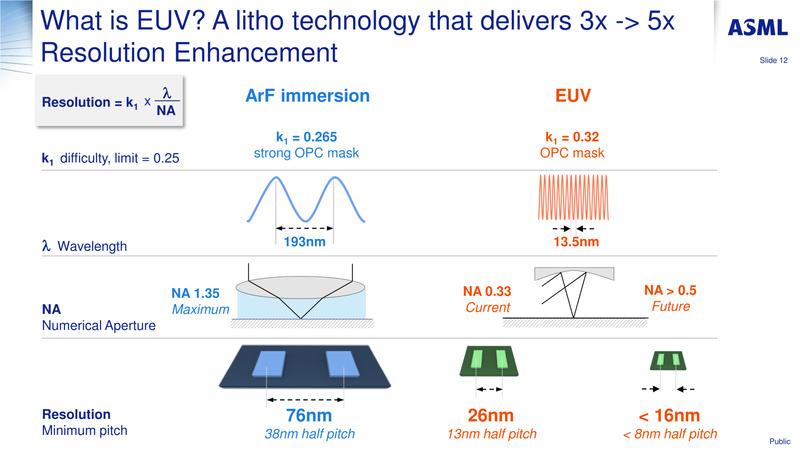

Las técnicas usadas hasta ahora por la mayoría de fabricantes del mundo era ArF, concretamente el proceso de inmersión ArF. Solo existen actualmente dos fabricantes que pueden crear la maquinaria precisa para este tipo de técnica de resolución fotolitográfica: ASML y Nikon.

El proceso de grabado es «sencillo» y no nos vamos a extender en él pero si lo explicaremos brevemente: el aire habitual entre la lente final y la superficie de la oblea es reemplazado por un medio líquido que tiene un índice de refracción superior a uno. Por lo tanto la resolución se incrementa en un factor igual al índice de refracción del líquido usado.

Pero como toda tecnología se llega a un límite donde el seguir reduciendo la resolución se hace más y más complicado, sobre todo para conseguir una densidad que merezca realmente la pena para el inmenso gasto generado en I+D.

En este caso hemos llegado al final del camino, tanto Intel como TSMC llevan años luchando para mejorar el tan buscado Half pitch con una resolución menor.

Actualmente ArF por inmersión consigue una longitud de onda de 193 nm pero mediante el líquido se consigue un patrón mínimo de 76 nm con un half pitch de 38 nm.

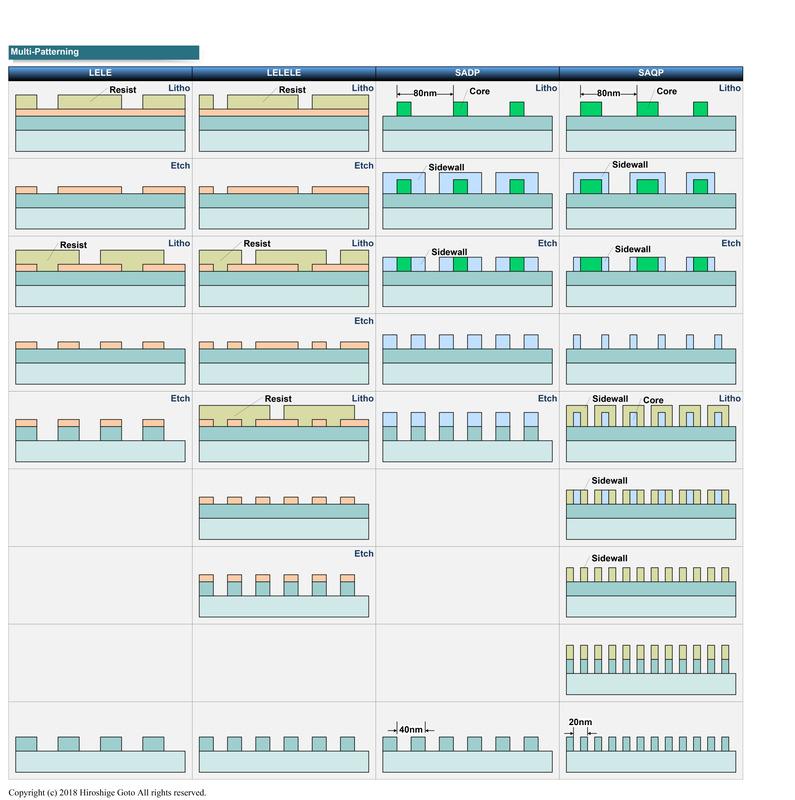

Para reducir este pitch es necesario recurrir a un nuevo sistema de múltiples patrones con un mayor número de máscaras, lo cual de nuevo aumenta el costo para conseguir un menor espacio entre las aletas del transistor.

Según ASML los pasos para conseguir los 7 nm por inmersión aumentan hasta 34, mientras que los 10 nm son solo 23, mientras que el riesgo crítico de fallar en los alineamientos aumenta de 40 a 65 pasos.

La solución a todos estos problemas la tendremos en los 7 nm+ de TSMC y los 7 nm de Intel, donde ambos usarán la nueva tecnología EUV y los costes bajarán mucho, ya que por ejemplo de 32 pasos en 7 nm pasaremos a solo 9 con un riesgo de 12 pasos.

Entonces ¿AMD con sus 7 nm hará que sus CPUs cuesten más?

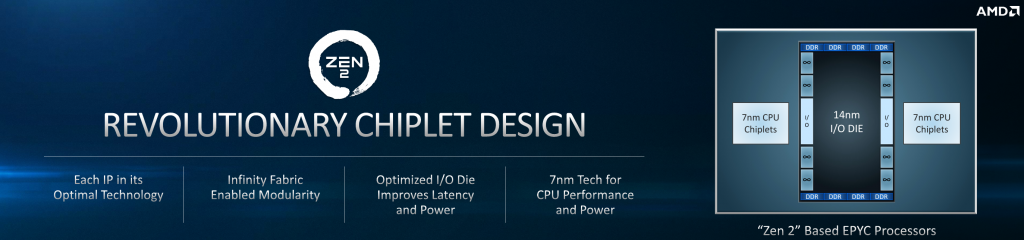

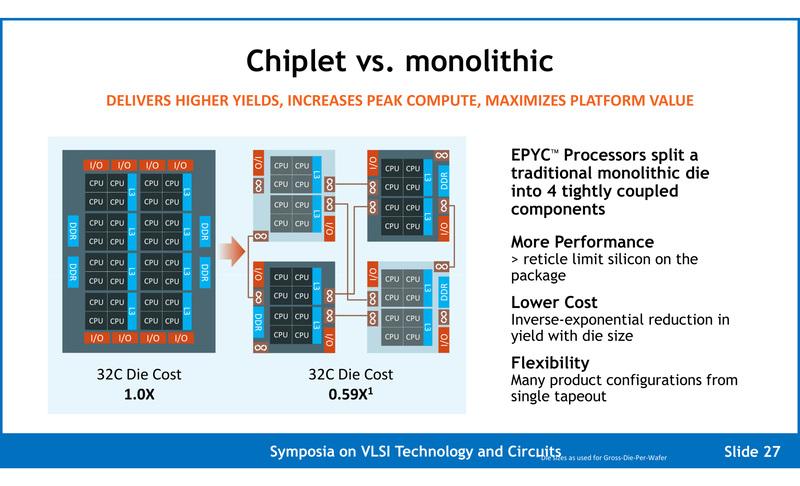

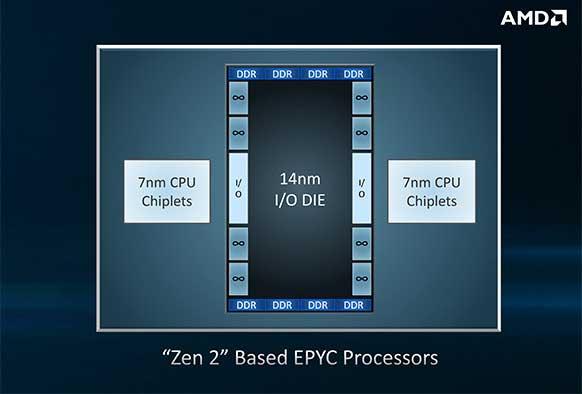

Este es el punto de nexo con la rama principal del hilo. El sistema de AMD permite usar unos núcleos más simples y por lo tanto más pequeños, reduciendo el coste y moviendo partes esenciales del mismo a un nuevo chip central que se encargará de múltiples tareas.

Dicho chip es el llamado I/O chiplet, y vendrá fabricado en un proceso litográfico de 14 nm por GlobalFoundries, mientras que como ya sabemos los chiplets de los núcleos vendrán de la mano de TSMC.

Cada chiplet de núcleos se comunica directamente con el I/O a través de un enlace Infinity Fabric dedicado, por lo que el diseño es totalmente modular, debido a ello pasaremos de un sistema NUMA en Zen y Zen+ a un sistema UMA en Zen 2 donde el chip I/O proporcionará una latencia más uniforme y es más predecible.

Dicho chip I/O alberga partes importantes como los controladores SATA o las líneas PCIe 4.0, por lo que AMD obtiene lo mejor (en un principio) de las dos vertientes: consigue chips más pequeños y por ende más baratos de fabricar y con menos tasa de fallos para sus núcleos con TSMC y al mismo tiempo GlobalFoundries les proporciona un nodo maduro y fiable a 14 nm que a su vez es extremadamente barato.

Por eso, antes hablábamos de eficiente y sencillo entre comillas, es un sistema de construcción eficiente y más sencillo, pero tiene partes complicadas como el interposer y la disposición de buses y características.

Si AMD hubiese seguido por el sistema monolítico de Intel estaríamos hablando, según AMD, de unas CPUs un 59% más caras de fabricar, cifra nada despreciable.

Desde el punto de vista económico, es un desperdicio de dinero intentar crear unos dies más grandes incorporando todas las unidades y buses de Zen 1 en Zen 2 a 7 nm, por ello AMD inteligentemente decidió sacar dichos buses a un I/O central.

Si este sistema funciona como se espera, en un futuro y gracias a EUV podríamos ver un mayor recuento de núcleos al disponer de mayor espacio y al mismo tiempo unos dies más pequeños y sencillos de fabricar, pero eso será para otro artículo.

De momento no tenemos información de las características del chip I/O, ya que es la pieza central de la arquitectura Zen 2, pero AMD ha dicho que pondrá la información disponible en la presentación de EPYC 2, así que tocará esperar pacientemente.