El año pasado TSMC ya anunció bastantes novedades sobre el sucesor real de su aclamado nodo de 7 nm, donde AMD lo está exprimiendo a base de bien en todos los productos de la compañía. Ahora, los taiwaneses han desvelado muchos de los entresijos de dicho proceso litográfico y a raíz de esto, parece que la compañía va a marcar de nuevo una distancia muy grande con Intel y Samsung de cara al año que viene. ¿Dominará el mercado AMD en solitario con Zen 4 con TSMC 5 nm?

Como decimos, TSMC ha desvelado casi todo lo referente a su nuevo proceso litográfico, que como ha ocurrido con sus 7 nm, volverá a marcar la pauta el año que viene de la mano de AMD y puede que de NVIDIA.

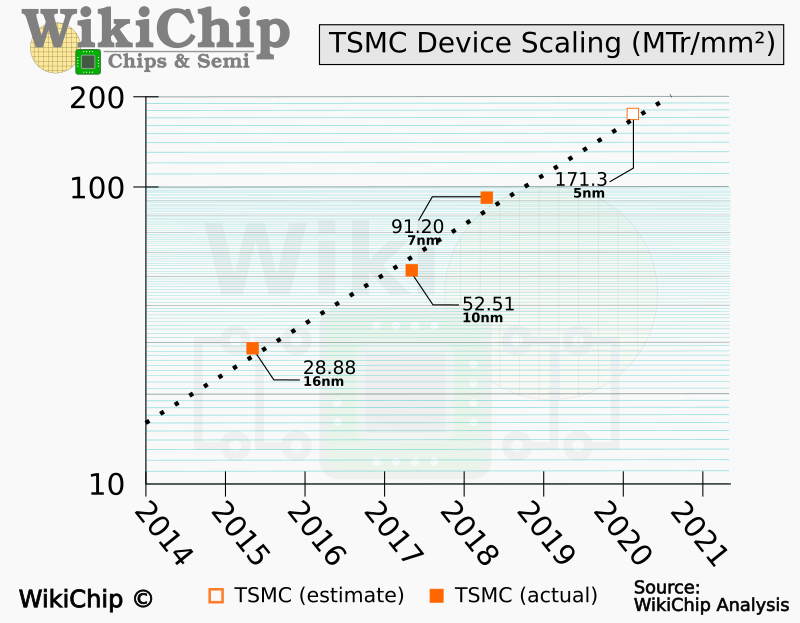

Tanto es así, que la compañía va más rápido que la línea de tendencia actual e histórica de la Ley de Moore, lo cual ya de por sí es impresionante. Así que vamos a entrar en más detalles de lo que está por venir y cómo AMD puede situarse al frente de la industria si Intel y Samsung no responden en muy breve espacio de tiempo.

TSMC 5 nm: casi duplica la densidad de los 7 nm actuales

Solo han pasado 5 años, repito, 5 años, desde que la compañía lanzase sus 16 nm FinFET al mercado con una densidad de 28,88 millones de transistores por mm2 hasta este año que veremos sobre el último trimestre las primeras obleas salir de sus fábricas a 5 nm.

Aunque la compañía no ha ofrecido todavía el dato concreto de la densidad de este nuevo proceso litográfico, las estimaciones vertidas por diversas fuentes lo sitúan en 171,3 millones de transistores por mm2. Esto es casi el doble si lo comparamos con los 91,20 MTr/mm2 que tiene el actual proceso de 7 nm, es decir, TSMC va a conseguir casi duplicar la densidad en solo dos años.

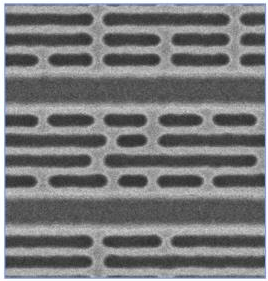

Por supuesto, dicho proceso litográfico será el primero en ser totalmente fabricado mediante EUV y eso supone unas distancias y aletas para cada oblea inferiores y superiores a lo visto hasta ahora. El Fin Pitch será de aproximadamente 25 o 26 nm mientras que el Metal Pitch pasará a ser de solo 30 nm donde se estima dos alturas de celdas distintas según el tipo de proceso designado: SoC o HPC.

Y es que este nodo de 5 nm parece tan depurado en pleno 2020 que la compañía asegura que es un proceso litográfico de alto nivel, alta densidad y alto rendimiento.

Esto es un paso definitivo para construir procesadores de las más altas prestaciones y sorprende por no llegar en primer lugar como un nodo para smartphones o procesadores de bajo consumo, como suele ser habitual en la industria.

Se mantienen las 12 pulgadas por oblea y se fabricarán en exclusiva en Taiwán

Será la Fav18 de TSMC en el Parque Científico del Sur de Taiwán donde se dará vida a los procesadores de AMD y otras compañías de cara al año que viene. Como bien sabemos, un SoC se compone de tres partes principales: lógica, SRAM y analógica/IO, donde cada parte tiene un porcentaje distinto para completar dicho SoC.

Según informó TSMC, estas proporciones para un SoC móvil a 5 nm serían del 60%/30%/10% lo que si lo comparamos con los 7 nm actuales significaría una reducción del 35% al 40% del tamaño del chip.

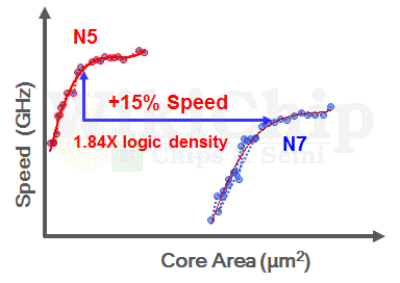

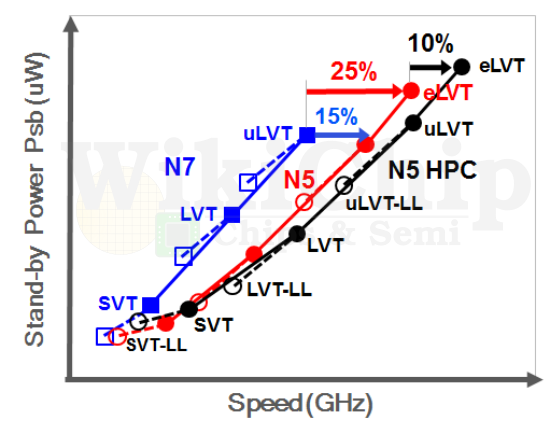

Las mejoras no terminan aquí ya que TSMC afirma que los dispositivos que integren su nodo ofrecerán un 15% más de velocidad o en cambio, un 30% menos de potencia a misma velocidad.

Por si fuese poco, es posible que mediante eLVT (que no uLVT) se logre un salto más amplio de velocidad, hasta el 25%, o un 10% a costa de la densidad.

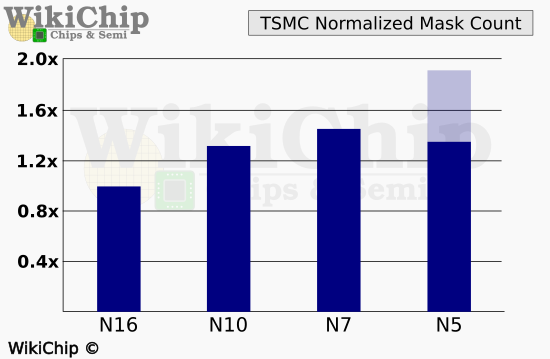

Este logro es posible debido a que solo se van a usar 10 capas EUV en vez de las 40 que serían necesarias para este mismo proceso litográfico pero en DUV. Gracias a ello, N5 será el primer proceso litográfico que use menos capas que su predecesor.

SRAM

Tendremos dos tipos de variaciones SRAM, las cuales dependerán del tipo de celda que quiera el diseñador del chip y por lo tanto a grandes rasgos TSMC ofrecerá una de alto rendimiento y otra de alta densidad. La lógica nos dice que esto se implementará en las distintas gamas de procesadores o SoC gracias a las distintas matrices de fabricación.

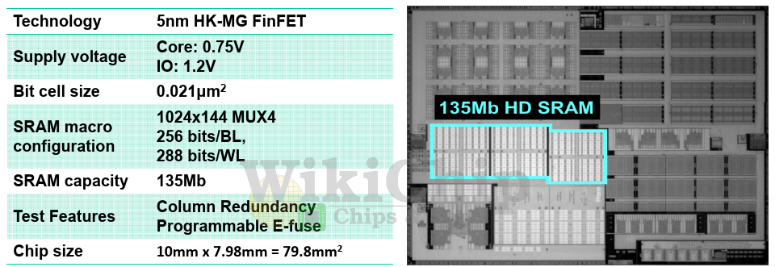

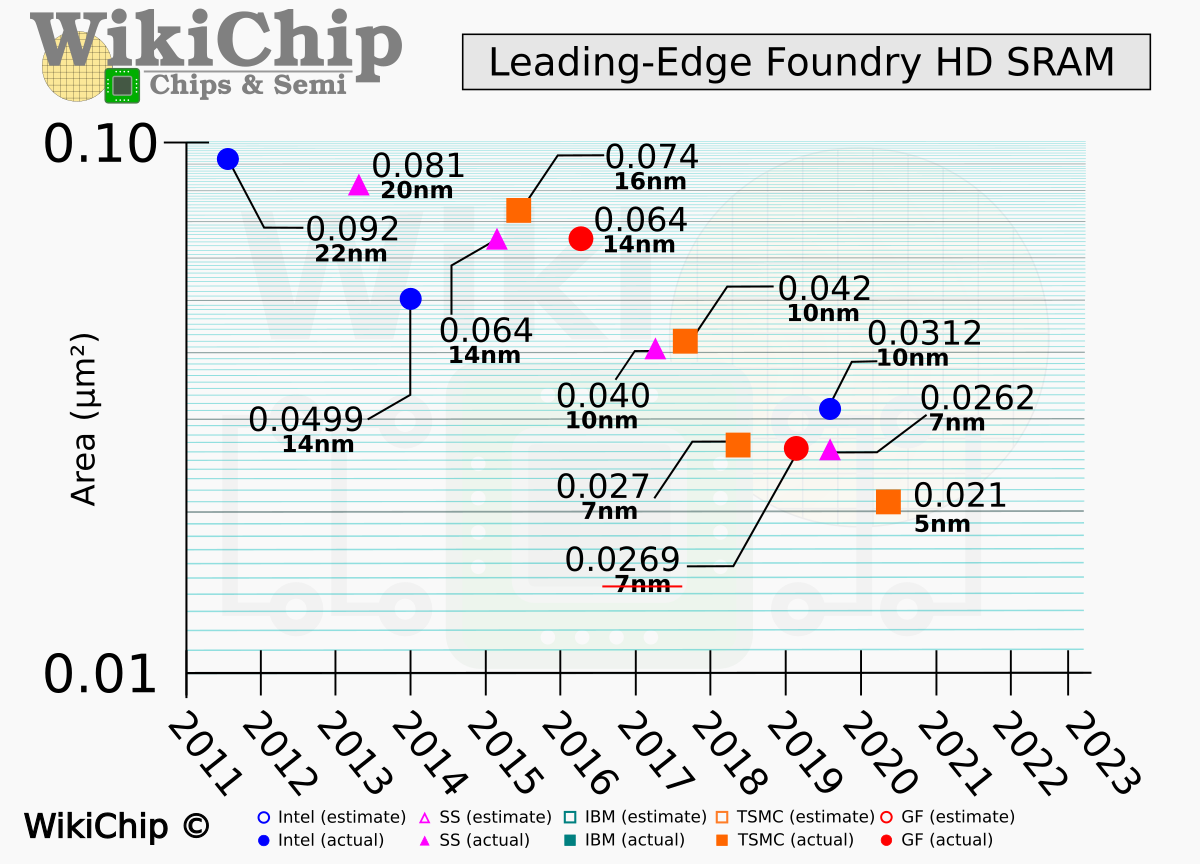

La celda de alto rendimiento es de 0.025 µm², mientras que la de alta densidad se irá hasta los 0.021 µm², por lo que viendo estos números podemos afirmar que en ambos casos son, de momento, las celdas más densas creadas hasta la fecha.

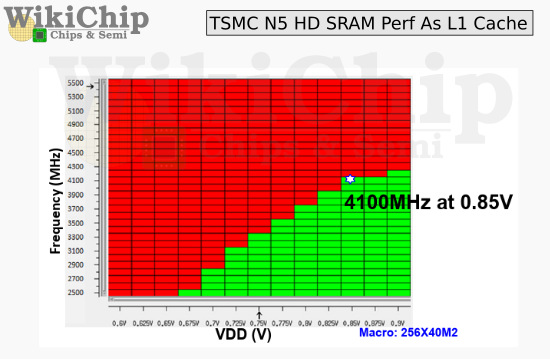

Para TSMC 5 nm la compañía mostró un diagrama de la matriz HD SRAM donde usaban cachés L1 de alto rendimiento y gracias a ellas se pudo alcanzar una velocidad de 4,1 GHz con solo 0.85V.

Siguiendo el mismo gráfico, parece que se podría alcanzar casi los 4,5 GHz con 1V, algo simplemente a otro nivel frente a lo que tenemos en el mercado actualmente.

En resumen, TSMC llegará en 2021 con un proceso litográfico un paso y medio por delante del resto, donde Intel podría implementar sus 7 nm EUV con mucha suerte y esfuerzo y Samsung es, de momento, una incógnita, puesto que está centrando sus esfuerzos tanto en DRAM como en el resto de obleas para chips de alto rendimiento.

Si ninguno de sus rivales llega a tiempo, AMD puede dominar desde principios de año el mercado con mano de hierro en base a Zen 4 y posteriormente RDNA 3 con Navi 3X. El ritmo que impone TSMC no parece que tenga freno y ya piensa en sus 3 nm, realmente impresionante.