Apple ha colapsado las entregas de los 5 nm de TSMC y visto el rendimiento del A14 y del futuro Kirin 9XXX, donde en ambos casos el rendimiento apenas ha despegado, el consumo apenas se ha reducido y en general, las mejoras parecen menores de lo esperado, sobre el aire pandea una pregunta, ¿Es el N5 un fracaso de TSMC? ¿qué hará AMD si la versión de alto rendimiento no consigue las mejoras previstas?

TSMC se podría decir que ha triunfado con los 7 nm en todos los ámbitos, ya que es el nodo estrella del momento en muchos sectores. Pero sus N5 no pintan tan bien, sobre todo si tenemos en cuenta las mediciones de muchos SoC como el del Apple y Huawei, ¿qué está ocurriendo?

Mejoras muy leves en un proceso que no es de alto rendimiento

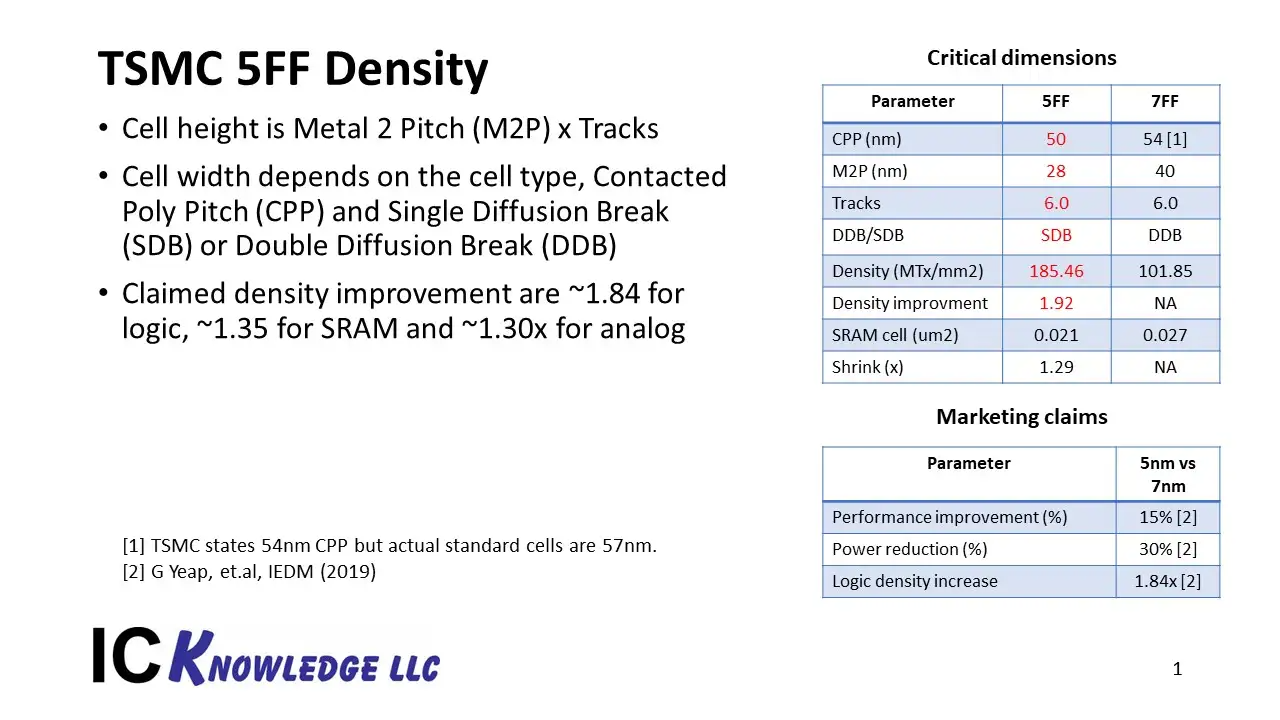

Lo visto con el A14 nos hizo preguntarnos, ¿qué está pasando con Apple? cuando la pregunta realmente es, ¿qué está pasando con los N5 de TSMC? Las mejoras del chip de Apple, siendo su primera versión ARM exclusiva con nodo igualmente exclusivo nos dejaron fríos. No es que el chip sea malo en sí mismo, porque no es así, pero las mejoras frente al A13 tras los cambios de arquitectura y salto en nanómetros nos hacían pensar en un rendimiento muy superior en todos los ámbitos.

Los problemas parecen ser derivados de EUV, donde el mayor número de capas puede estar dificultando lo que a priori no parecía un problema y no es más que lograr una mayor eficiencia y un mayor rendimiento. Históricamente Apple siempre se ha jactado de alcanzar al menos el 90% de la densidad teórica del nodo en el que estuviese trabajando, pero con el A14 no ha habido ni una reseña al respecto hasta ser preguntados.

Resulta que, tras cierta entrevista, el A14 a 5 nm solo ha conseguido el 78% de densidad de transistores efectiva, lo que implica una seria pérdida total en el conjunto del chip.

¿Estamos ante un fiasco de nodo N5 por seguir en FinFET?

No está realmente claro, pueden ser el mayor número de capas, puede ser que FinFET ya no esté tan optimizado bajo EUV y tanta capa o puede que simplemente Apple no se haya adaptado al nodo. En cualquier caso, hay que recordar que la propia TSMC habló de una reducción de 1.84X, pero es que el A14 está muy por debajo con 1.49X.

Intel y Samsung ya trabajan con GAA en nanosheet y TSMC va a llevar FinFET hasta el límite de su vida útil con 3 nm. Si los 5 nm son un nodo de transición y la variante de alto rendimiento va a sufrir los mismos problemas, quizás AMD deba replantearse el uso de este nodo si no hay cambios significativos frente a 7 nm.

Hay que recordar que Intel llega pisando fuerte con 10 nm SuperFin, que AMD ha tenido que lanzar Zen 3 y RDNA 2 en 7 nm sin + y que EUV podría ser la solución temporal en esos 7 nm si finalmente se saltan los 5 nm de alto rendimiento.

Y es que no todo es densidad como estamos viendo, el diseño de las celdas, la altura, las gates y un sin fin de conexiones es tan importante o más que conseguir simplemente meter más transistores por milímetro cuadrado.